Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может найти применение в высокопроизводительных машинах и системах. Целью изобретения является повышение быстродействия за счет введения двух регистров, двух коммутаторов, двух сумматоров и соответствующих связей. Устройство работает по принципу конвейера, за счет наличия в нем регистров частичных произвеений, причем в каждом цикле осуществляется умножение на очередные P разрядов старшей и младшей частей множителя, (где P*983), и в процессе умножения простой основной части оборудования сведен к минимуму. 3 ил.

А1.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1615706 (g1)g G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А 8ТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

llO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР (21) 4626)98/24"24 (22) 14,11.88 (46) 23. 12. 90. Бюл. У 47 (72) А.И.Бобровский, В.П. Буяло, Ж.Б.Ерема-Еременко, В.Н, Петрунек, А.И. Трубицын и В. А. Осипов (53) 681. 325 (088. 8) (56) Авторское свидетельство СССР

И! 754412, кл. G 06 F 7/52, 1970.

Самофалов К.Г. и др. Цифровые электронные вычислительные машины. . Киев: Высшая школа, 1983, с. 304, рис. 5. 1 7. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ (57) Изобретение относится к цифроИз обр ет ение отно сится к цифровой вычислительной технике,.предназначено для умножения чисел, представленных в двоичной системе счисления, и может найти применение в качестве операционного блока в высокопроизводительных вычислительных машинах и системах.

Целью изобретения является повышение быстродействия.

В устройстве операнды - положительные числа, представленные в виде

11

«1

А,> а 2, а; 6{0,1), гда А

1 а„ а ... а и - двоичный п-разрядный код числа А. Выполнение операции умножения в устройстве основано на таблично-алгоритмическом методе умножения с использованием конвейеризации за счет совмещения во времени получения элементарных произведений

2 вой вычислительной технике н может найти применение в высокопроизводительных машинах и системах, Целью изобретения является повышение быстродействия за счет введения двух регистров, двух коммутаторов, двух сумMsTopoB и соответствующих свяэейа

Устройство работает по принципу конвейера за счет наличия в нем регистров частичных произведений, причем в каждом цикле осуществляется умножение на очередные р разрядов старшей н младшей частей множителя (где р 0 3), и в процессе умножения простой основной части оборудования eseден к минимуму. 3 ил.

I и накопления сумьа! частичных произведений и распараллеливания эа счет совмещения во времени вычисления произведений множимого на старшую и младшую части множителя. я в

Пусть Х= х; 2 и Y- у2 а 1 множимое и множитель соответственно, где х; и у, — значения i-x разрядов. кодов сомножителей. Тогда для представления точного результата 2 . Х Y требуется 2п-разрядньп!. двоичный код.

Процесс вычисления произведений

Z запишется в виде

P P г

Z,О (7,0 Х ° (2 ) ) ° (2 ), (1)

1-! lm I где х; = x x,... x ., — i-я двоично-кодирован!!ая циФра кода множимого в !:а!!онической

1615706

10 (2) 15 позиционной системе счислес ocHo aHHeM q = г ; у зи ° у p +< ° ° еу1+р < 1 я двоично

J кодированная цифра кода множителя.

Если Y представить как сумму старшей и младшей частей:

Q а

6 ст+ Ygg = У; 2 + ь

I=l

+ у; ° 2 с а тогда процесс вычисления Z запишется в виде

Р

2Р Р р 1

Z (Y ° x ° (2 ) ) (2 ) + .1 .

1 и TI

Р P

+ 0 (7 Г х;(2 ) ) .(2 ) . (3)

1;

20 LP

Таким образом, процесс умножения состоит из однотипных повторяющихся циклов. Во время очередного j-ro цикла j-ro частичное произведение Y

III P р ст.) 25 х - 2 множимого на очередные р разрядов старшей части множителя

1 . и

;; вычисляется на = К умножителях

P л ! выполняющих операцию умножения р-раз-, 30 . :рядного двоичного кода Y на р-раз. рядный двоичный код Х; с образовани1 ем произведения разрядности 2р. Далее элементарные произведения "собираютII ся в и + р двоично-разрядный код частичного произведения х Y, на 35 сумматоре, одновременно на тех же К . умножителях формируются элементарные .произведения Х на очередные р разря: дов младшей части множителя Y которые затем "собираются" в частичное 40 произведение на другом сумматоре.

Наличие регистров частичных произведений при соответствующем управлении позволяет организовать конвейер при вычислении Х Y т или Х ° Yллл, 45 когда в один и тот же момент времени на соответствующем сумматоре формируется частичное произведение

Х 7,„. +, (или Х Умл.+,), а на другом сумматоре формируется сумма частичных произведений Z T,> = Е . 2 +

+ X ° Yc1. (или Емл,, = Ещ,, l 1 +

С ° ст, + Х Ум„) . Процессы вычисления

X Y T. I Емл.1 anH X YINII +1 H Zn совмещены во времени. 55

После вычисления и-разрядных

2 значений Е и Е л для определения

Е = Ес + Ел л происходит суммирование на одном из сумматоров Z и и ст старших разрядов Z >. В результате

3 определяются — — n старших разрядов и

Е, а младшие разрядов опреде. 2 ны при вычислении Z .

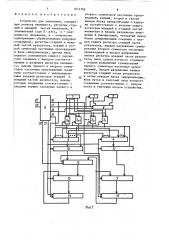

На фиг.l приведена функциональная схема устройства для умножения; на фиг.2 — относительная временная развертка сигналов на выходах блока синхронизации; на фиг.3 — пример реализации блока синхронизации.

Устройство (фиг.1) содержит регистры множимого 1 и младшей части множителя 2, К умножителей 3 { — 3

Кл второй сумматор 4 элементарных произведений, второй сумматор 5 частичных произведений, блок 6 синхронизации, регистр 7 старшей части множителя, первый коммутатор 8, первый сумматор 9 элементарных произведений, первый 10 и второй 11 регистры частичных произведений, второй коммутатор

12, первый сумматор 13 частичных про" изведений, регистры старшей 14 и младшей 15 частей результата.

Блок 6 синхронизации (фиг.3) содержит выходы 16-21, вход 22 пуска, тактовый вход 23, RS-триггер 24,элемент И 25, счетчик 26 и элемент 27 памяти.

Регистр 1 множимого предназначен для хранения множимого и х=, > х (2),0 х; (2 )

1= I ;1

Регистр 7 старшей части множителя.— и сдвиговый, -«2- -разрядный, причем сдвиг осуществляется на р разрядов, предназначен для хранения Y сг

Умножители 3 1 — 3 предназначены для вычисления очередного элемента— ного произведения Х; Y, i = 1,. ...,К, имеют два р"разрядных входа и 2р-разрядный выход. В качестве умйожителей могут быть применены однотактные матричные умножители или ПЗУ с прошитой таблицей умножения в

2 -ной системе счисления.

Первый коммутатор 8 — р-разрядный, предназначен для передачи на вход умножителей 31-3 соответствующих р разрядов с регистра 7 или 2.

Регистр 2 младшей части множите- п ля — — — + р-разрядный, сдвиговый, 16 5706 причем сдвиг осуществляется на р рязрядов, предназначен для хранения уел

Первый и второй сумматоры 4 и 9 элементарных произведений — и-разрядные, предназначены для формирования старших и разрядов частичных произведений Y „ ° Х и У ° Х соответственно.

Первый и второй регистры 11 и 10 частичных произведений — п -р-разрядные, предназначены для хранения частичных произведений Y „ Х и У,г" X ми. соответственно, п разрядов которых поступ .от из соответствующего сумматора 4 и 9, а младшие р разрядов из умножителя 3

Второй коммутатор 12 предназначен для передачи на вход второго слагаемого сумматора 13 частичных произведений операнда из регистра 10 частичных произведений или старших и разрядов регистра 15 младшей части результата, Сумматор 5 частичных произведений — двухвходовый, п -р-разрядный, предназначен для вычисления значений Zyp в

Сумматор 13 частичных произведе3 ний — двухвходовый, †- n-разрядный, предназначен для вычисления значений 2ст и суммы Z = Z qT + Z q. .!

Регистр 14 старшеч части произве3 дения — — — и + р-разрядный сдвиго2

1 вый, причем сдвиг осуществляется на

3 р разрядов ° Регистр 15 — — — и+р-раз2 рядный, сдвиговый, причем сдвиг осуществляется на р разрядов.

Блок б синхронизации обеспечивает формирование последовательностей управляющих сигналов (фиг.2).

Устройство работает следующим образом.

В исходном состоянии в регистре 1 находится множимое Х, в старших разрядах регистра 2 — младшая часть множителя Ум< в регистре 7 — старшая ,часть множителя Y T-, регистры 10, 11, 14 и 15 обнулены (на фиг.! цепи с6роса и питания не показаны).

В каждом цикле по сигналу на выходах 19, 21 и 17 блока синхронизации происходят формирование К элементарных произведений Х1 Уст

1,...,К, сдвиг содержимого регист5 !

О !

3С

50 ра 2 в сторону младших разрядов на р разрядов, сложение сформированных на предыдущем (j-1)-цикле элементарных произведений на сумматоре 4 и за-! пись результата на регистр 11,сложение сформированного в (j-1)-м цикле частичного произведения Х; У г — 1 с содержимым регистра 14 на сумматоре 13 (при j =! складываются нули), сдвиг содержимого регистра 15 в сто рону младших разрядов на р разрядов.

Далее по сигналам на выходах 18, 19 и 16 блока синхронизации происходят формирование К элементарных произведений Х, Y, ä, сдвиг содержимого регистра 7 в сторону младших разрядов на р разрядов, сложение сформированных ранее Х;Y, i = 1,...,К на сумматоре 9 и запись полученного

XY > на регистр 10, сложение содер-! жимого регистра 11 с содержимым регистра 15 на сумматоре 5 и запись результата на регистр 15 (при j = 1 складываются нули), сдвиг содержимого регистра 14 в сторону младших разрядов на р разрядов. !

К

После — — циклов умножения по сиг2 налу на выходе 2! блока синхронизации происходят сложение на сумматоре

l3 содержимого регистра 10 с содержанием регистра 14 и запись сформированной старшей части произведения Z сТ на регистр 4. По тому же сигналу происходят сложение на сумматоре 4 сфорI ° . К мированных в последнем (j = †-)

2 цикле элементарных произведений

Х;УМ и запись сформированного частичного произведения ХУ>> на реМФ! гистр 1 1. Далее по сигналу на выходе

16 блока синхронизации происходит сложение на сумматоре 5 содержимого регистров 11 и 15 и сформированная младшая часть произведения Z»запими сывается на регистр 15. По сигналам на выходах 20 и 21 блока синхронизации происходит сложение на сумма3 торе 5 --- n-разрядного кода 2 и и

2 сг старших разрядов Z,, полученные

3 значения — — и разрядов Z записыва2 и ются на регистр 14 а — — младших

2 разрядов Z находятся в младших разразрядов Z находятся в младших разрядах регистра 15.

1615706

Формула изобр етения

Устройство для умножения, содержащее регистр множимого, регистры старшей и младшей частей множителя, К умножителей (где К - рЪ и, n — раз,рядность операндов, р — количество ! одновременно обрабатываемых разрядов операндов), регистры старшей и младшей частей результата, первый и второй сумматоры частичных произведений и блок синхронизации, причем вход первого сомножителя каждого умножи теля соединен с выходом соответст,вующих р разрядов регистра множимо-! го, выходы первого и второго сумма торов частичных произведений соеди:нены соответственно с информацион. ными входами регистров старшей и ! .младшей частей результата, выходы ! .которых соединены соответственно с входами первых слагаемых первого и ! второго сумматоров частичных произведений, первый, второй и третий выходы блока синхронизации сгедине5 ны соответственно с входами сдвига регистров младшей и старшей частей множителя и входом разрешения умножения К умножителей, четвертый выход блока синхронизации соединен с входом сдвига регистра старшей части результата, входом разрешения суммирования второго сумматора частичных произведений и входом разрешения записи регистра младшей части результата, вход сдвига которого соединен с входом разрешения суммирования первого сумматора частичных произведений, входом разрешения записи регистра старшей части результата и пятым выходом блока синхронизации, . вход пуска и тактовый вход которого соединены соответственно с входом пуска и тактовым входом устройства.

)6)5706

Фиг. 2

Редактор 0.)Орковецкая

Заказ 3987

Тираж 567

Подписное

ВНИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 с И

1 17

> 18

h fg ъ 2О 27

Со ст авит ель Е . Мурзина

ТехРед М. Кораине КоРРектоР В, ГиРнЯк