Устройство для контроля двоичного кода на четность

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах для обмена информацией. Цель изобретения - повышение быстродействия устройства. Устройство содержит группу 1 элементов И, элементы ИЛИ 2, 23, узел 3 сравнения, элемент НЕ 4, узлы 7, 22 свертки по модулю два, элемент И 21, элемент задержки 20, коммутатор 6. Информация поступает на один из двух информационных входов 11, 12 устройства. Затем она проходит через коммутатор 6 под воздействием сигналов, возникающих на тактовых входах 8, 9 устройства. Правильность приема информации контролируется с помощью узлов 7, 22 свертки по модулю два, элемента ИЛИ 2 и узла 3 сравнения. При неправильном приеме на выходе 5 ошибки устройства формируется единичный сигнал. При правильном приеме на выходах 13, 15 или 14, 16 устройства появляется информационное слово с контрольным разрядом. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧЕСКИХ

РЕСПУБЛИК (si1s G 06 F 11/10

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4657526/24-24 (22) 28.11.88 (46) 23.12 90. Бюл. ¹47 (72) B.Н.Потанцев, А.И.Фролов, А,Н,Очеретяный и Ю.А.Сысоев (53) 681.3(088.8) (56) Авторское свидетельство СССР № 746530, кл. G 06 F 11/10, 1978.

Авторское свидетеластво СССР № 989558, кл. G 06 F 11/10, 1981. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВОИЧНОГО КОДА НА ЧЕТНОСТЬ (57) Изобретение относится к вычислительной технике и может быть использовано s цифровых устройствах для обмена информацией. Цель изобретения — повышение быстродействия устройства. Устройство.... Ы, „1615724 А1 содержит группу 1 элементов И, элементы

ИЛИ 2 и 23, узел 3 сравнения, элемент НЕ

4, узлы 7 и 22 свертки по модулю два, элемент N 2211,, э л еем еенНт Т 220 0 з3а д еер ж кКи, коммутатор б, Информация поступает на один из двух информационных входов 11 и 12 устройства. Затем она проходит через коммутатор б под воздействием сигналов„ возникающих на тактовых входах 8 и 9 устройства, Правильность приема информации контролируется с помощью узлов 7 и 22 свертки по модулю два, элемента ИЛИ 2 и узла 3 сравнения. При неправильном приеме на выходе 5 ошибки устройства формируется единичный сигнал. При правильном приеме на выходах 13, 15 или 14, 1l6 устройства появляется информационное слово с контрольным разрядом. 3 ил.

1615724

Изобретение относится к вычислительной технике и можег быть использовано в цифровых устройствах для обмена информацией, Цель изобретения — повышение быстродействия устройства.

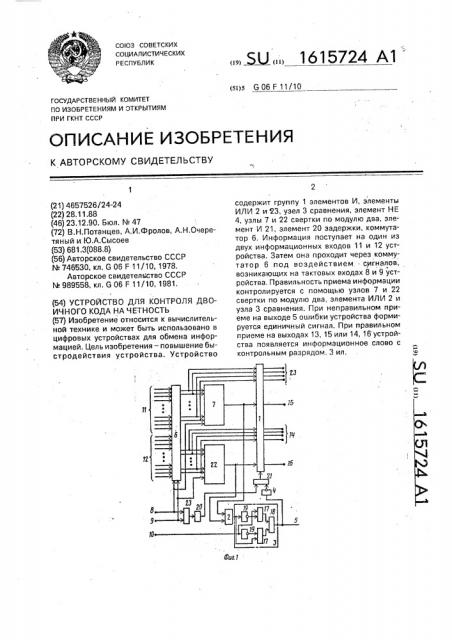

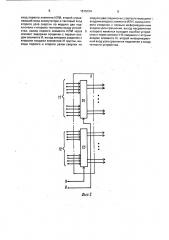

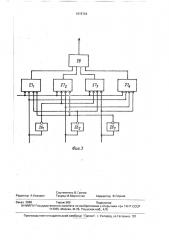

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 и 3 — функциональные схемы коммутатора и узла свертки по модулю два на три входа соответственно.

Устройство (фиг. 1) содержит группу 1 элементов И, второй элемент ИЛИ 2, узел 3 сравнения,, элемент HE 4, выход 5 ошибки устройства, коммутатор 6, первый узел 7 свертки по модулю два, первый 8 и второй 9 тактовые входы устройства, вход 10 четности устройства, первый 11 и второй 12 информационные входы устройства, первый

13 и второй 14 информационные выходы устройства, первый 15 и второй 16 выходы четности устройства, группу 17 элементов И узла 3 сравнения, элемент ИЛИ 18 узла3 сравнения, группу 19 элементов HE узла 3 сравнения, элемент 20 задержки, элемент И

21, второй узел 22 свертки по модулю два и первый элемент ИЛИ 23.

Коммутатор 6 (фиг. 2) содержит две группы 24 и 25 элементов И, а узел 7 (22) свертки по модулю два (фиг. 3) — группу 26 элементов НЕ, группу 27 элементов И и элемент ИЛИ 28, l0

На первый 8 и второй 9 тактовые входы устройства подаются сигналы чтения и записи соответственно при поступлении кода на информационные входы 11 и 12 устройства, Устройство может работать в одном из двух режимов обмена данными с микропроцессором; в режиме "Запись" или в режиме

"Чтение", В этих режимах устройство производит как контроль передаваемой (принимаемой) информации на четность, так и повторное ее кодирование после контроля, Устройство работает следующим образом.

В режиме "Запись" на второй тактовый вход 9 устройства поступает синхронизирующий импульс, на вход 10 четности устройства — контрольный разряд, на первый информационный вход 11 устройства — параллельный двоичный код. Сигнал с входа 9 устройства поступает на второй управляющий вход коммутатора 6 и разрешает прохождение информации с первого информационного входа коммутатора 6 на его первый выход. Отсюда информация попадает на информационный вход первого узла 7 свертки по модулю два и первые входы соответствующих элементов И группы 1. С выхода первого узла 7 свертки по онном выходе 13 и на первом выходе 15 четности устройства.

В режиме "Чтение" информация поступает на второй информационный вход 12

20 устройства, тактовый сигнал — на вход 8 устройства и контрольный разряд — на вход

1О четности устройства. Устройство работает аналогичным образом: второй узел 22 свертки по модулю два формирует сигнал четности информационного слова, поступающего с второго выхода коммутатора 6. При соответствии сигналов на выходе узла 22 и входе 10 четности устройства сигналы с второго выхода коммутатора 6 и выхода узла 22 через соответствующие элементы И группы

1 проходят на выходы 14 и 16 устройства соответственно, 30

Формула изобретения

Устройство для контроля двоичного кода на четность, содержащее коммутатор, два узла свертки по модулю два, группу элементов И и элемент И, причем первый и второй информационные входы коммутатора являются первым и вторым входами кон35

40 тролируемого кода устройства, первый и второй выходы коммутатора соединены с информационными входами первого и вто45 рого узлов свертки по модулю два, первый и второй выходы коммутатора и выходы первого и второго узлов свертки по модулю два соединены с первыми входами соответствующих элементов И группы, выходы которых

50 образуют две группы информационных выходов устройства и два выхода четности устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия устрой-. ства, в него введены два элемента ИЛИ, элемент НЕ, элемент задержки и узел сравнения, причем первый вход первого элемента ИЛИ, первый управляющий вход коммутатора и тактовый вход первого узла

55 свертки по модулю два подключены к первому тактовому входу устройства, второй модулю два сигнал дополнения до четности поступает на первый вход соответствующего элемента И группы 1.

При несравнении сигналов на выходе

5 узла 7 и входе 10 четности устройства узел .3 сравнения формирует единичный сигнал на выходе 5 ошибки устройства и запрещает прохождение сигHBlloB с выходов коммутатора 6 и узла 7 через элементы И группы 1

10 на выходы 13 и 15 устройства, Если сигналы . на выходе узла 7 и на входе 10 четности уСтройства одинаковы, то тактовый сигнал с входа 9 устройства через элемент ИЛИ 23, элемент 20 задержки и элемент И 21 поступа15 ет на вторые входы элементов И группы 1, и сигналы появляются на первом информаци1615724

Фиг. 2 вход первого элемента ИЛИ, второй управляющий вход коммутатора и тактовый вход второго узла свертки по модулю два подключены к второму тактовому входу устрой-. ства, выход первого элемента ИЛИ через 5 элемент задержки соединен с первым входом элемента И, выход которого соединен с вторыми входами элементов И группы, выходы первого и второго узлов свертки по модулю два соединены с соответствующими:= входами второго элемента ИЛИ, выход которого соединен с первым информационным входом узла сравнения, выход несравнения которого является выходом ошибки устройства и через элемент НЕ соединен с вторым входом элемента И, второй информационный вход узла сравнения подключен к входу четности устройства.

1615724

Составитель В.Грачев

Редактор А.Козориз Техред M.Ìîðãåíòàë Корректор В.Гирняк

Заказ 3988 Тираж 569 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101