Устройство для контроля хода программы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах отладки программ, устройствах контроля правильности выполнения программ ЦВМ. Целью изобретения является упрощение устройства. Цель достигается за счет того, что в устройство, содержащее элементы И 3 и И 9, элементы задержки 4 и 6, счетчик 5, триггер 7, схему 8 сравнения, элементы ИЛИ 10 и 11, регистры 14 и 15, введены две группы схем сравнения 12 и 13. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 F 11/28

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4630116/24-24 (22) 02.01.89 (46) 23.12.90. Бюл. ¹ 47 (72) В.Л.Лясковский, С.Б.Кучин, B.С,ГЛоба и А.А.Поляков (53) 681.3(088.8) (56) Авторское свидетельство СССР №.63611, кл. G 06 F 11/00, 1977.

Авторское свидетельство СССР № 114269, кл. G 06 F 11/28, 1985.

».ЯХ, 1615725А1 (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ХОДА

ПРОГРАММЫ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах отладки программ и устройствах контроля правильности выполнения программ ЦВМ, Целью изобретения является упрощение устройства, Цель достигается за счет того, что в устройство, содержащее злементы И 3 и 9, злементы 4 и 6 задержки, счетчик 5, триггер 7, схему 8 сравнения, элементы ИЛИ 10 и 11, регистры 14 и 15, введены две группы 12 и 13 схем сравнения, 1 ил, 1615725

15

Изобретение относится к вычислительной технике и может быть использовано в

:- устройствах отладки программ и устройствах контроля правильности выполнения программ ЦВМ, Цель изобретения — упрощение устройства.

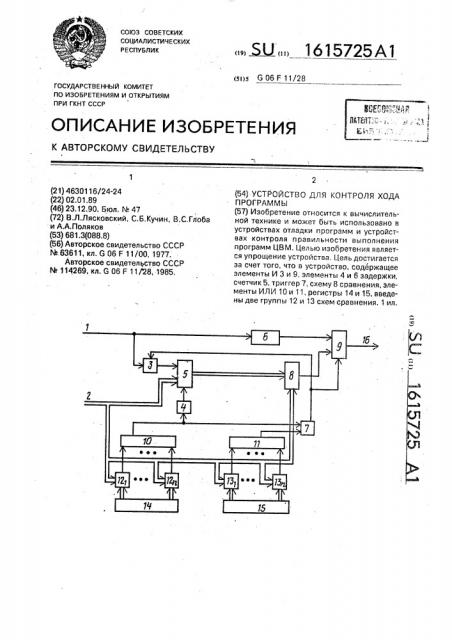

На чертеже показана схема устройства.

Устройство содержит вход 1 признака чтения команды, адресный вход 2, второй элемент И 3, элемент 4 задержки, счетчик 5, элемент 6 задержки, триггер 7, схему 8 сравнения, первый элемент И 9, первый 10 и второй 11 элементы ИЛИ, первую 12 — 12> и вторую 13> — 13л группы схемы сравнения, первый 14 и второй 15 блоки регистров и выход 16.

Устройство работает следующим образом.

В исходном состоянии счетчик 5, обнулен. В i-й регистр блока 14 регистров записан код адреса счетчика команд ЦВМ, соответствующий первой команде i-го линейного участка контролируемой программы. В I-1 ре.гистр блока 15 регистров записан код адреса счетчика команд ЦВМ, соответствующий последней команде I-го линейного, участка контролируемой и рограммы, Входы записи блоков 14 и 15 регистров не показаны.

Код адреса очередной команды со счетчика адреса команд ЭВМ (не показан) по входу 2 устройства поступает на первые входы схем 121 — 12, и 131-13л сравнения. По входу 1 устройства поступает импульс чтения команды из памяти ЭВМ, Если адрес очередной команды соответствует адреса первой команды I-ro линейного участка, то на выходе i-й схемы 12i сравнения появляется импульс, который, проходя через элемент ИЛИ 10, устанавливает триггер 7 в единичное состояние, а также, проходя через элемент 4 задержки, разрешает запись кода с входа 2 устройства на вход установки счетчика 5. Высокий потенциал с единичного выхода триггера O открывает элементы И

3 и 9, Адрес следующей команды поступает на вход схемы 8 сравнения, Импульс чтения этой команды с входа 1 устройства через открытый элемент И 3 поступает на счетный вход счетчика 5, увеличивая его состояние на единицу. Импульс с входа 1 также поступает на вход элемента 6 задержки, который задерживает его на время срабатывания элемента И 3 и счетчика 5. Импульс с выхода элемента 6 задержки поступает, на вход элемента И 9. Сигнал "Не равно" с выхода схемы 8 сравнения поступает на другой вход элемента И 9, и если этот сигнал равен единице, что соответствует наличию различных

55 кодов на входах схемы 8 сравнения, импульс появляется на выходе 16 устройства.

Этот импульс сигнализирует об ошибке при выполнении линейного участка программы.

Если и ри контроле 1-го линейного участка не обнаружено ошибок, то код последней команды I-го линейного участка сравнивается в схеме 13 сравнения с эталонным кодом, записанным в i-м регистре блока 15 регистров, и, проходя через элемент ИЛИ 11, обнуляет триггер 7, устанавливая тем самым устройство в исходное состояние.

Операция контроля любого другого j-ro линейного участка программы 0 < 1) аналогична операции контроля I-ro участка.

Таким образом, предлагаемое устройство позволяет контролировать правильность выполнения линейных участков программ.

Формула изобретения

Устройство для контроля хода программы, содержащее первый и второй блоки регистров, первый и второй элементы задержки, схему сравнения, первый и второй элементы ИЛИ, счетчик, триггер, первый и второй элементы И, причем адресный вход устройства соединен с первым входом схемы сравнения, выход первого элемента задержки соединен с первым входом первого элемента И, выход которого является выходом ошибки устройства, выход первого элемента ИЛИ соединен с единичным входом триггера, прямой выход которого соединен с первым входом второго элемента И, о т л ич а ю щ е е с я тем, что, с целью упрощения, устройство содержит две группы схем сравнения, причем вход признака чтения устройства соединен с входом первого элемента задержки и с вторым входом второго элемента И, выход которого соединен со счетным входом счетчика, адресный вход устройства соединен с первыми входами схем сравнения первой и второй групп и с информационным входом счетчика, информационный выход которого соединен с вторым входом схемы сравнения, выход неравенства которой соединен с вторым входом первого элемента И, выходы первого и второго блоков регистров соединены с вторыми входами схем сравнения соответственно первой и второй групп, выходы равенства каждой схемы сравнения первой группы соединены с соответствующими входами первого элемента ИЛИ, выход которого через второй элемент задержки соединен с входом записи счетчика, выходы равенства схемы сравнения второй группы соединены с соответствующими входами второго элемента

ИЛИ, выход которого соединен с нулевым входом триггера, единичный выход которого соединен с третьим входом первого элемента И,