Устройство для решения систем линейных алгебраических уравнений

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах в качестве спецпроцессора для решения систем линейных алгебраических уравнений. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство для решения систем линейных алгебраических уравнений содержит N блоков 1 вычислений, где N - порядок решаемой системы линейных алгебраических уравнений, сумматор 4, блок 5 анализа, формирователь 6 импульсов и блок 7 синхронизации. Данное устройство предназначено для нахождения решения системы линейных алгебраически: уравнений итерационным методом типа Гаусса-Зейделя. 1 з.п.ф, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„,Я0„. 1615739

А1 (gg)g G 06 F 15/324

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТ0РСНОМУ СВИДЕТЕЛЬСТВУ брод зиачения лажюсл4

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4650074/24-24 (22) 13.02.89 (46) 23.12.90. Бюл. № 47 (71) Физико-механический институт им. Г. В. Карпенко (72) В. В. Грицык, В. Я. Кыхальчишин, P. М. Паленичка и А. K. Батюк (53) 681.325(088.8) (56) Авторское свидетельство СССР № 813445, кл. G Об F f5/324, 1981.

Авторское свидетельство СССР

¹ 1462353, кл. G 06 F 15/324, 06.01.88. (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ

ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах в качестве спецпроцессора для решения систем линейных алгебраических уравнений. Цель изобретения — повыше.ние быстродействия. Поставленная цель достигается тем, что устройство для решения систем линейных алгебраических уравнений содержит и блоков 1 вью" числений, где п — порядок решаемой системы линейных алгебраических урав™ нений, сумматор 4, блок 5 анализа, формирователь 6 импульсов и блок 7 синхронизации. Данное устройство предназначено для нахождения решения системы линейных алгебраических уравнений итерационным методом типа ; ауссаЗейделя. 1 з.п. ф-лы, 2 ил.

1615739

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных систе,.мах в качестве спецпроцессора для ре1 шения систем линейных алгебраических уравнений.

Цель изобретения — повышение быст родействия устройства.

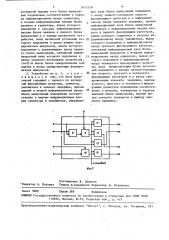

На фиг. 1 представлена схема уст- 1О ройства; на фиг. 2 — схема блока вычислений.

Устройство для решения систем линейных алгебраических уравнений содержит п блоков 1 вычислений, и входов 15

2 элементов матрицы коэффициентов устройства, вход 3 элементов вектора сво» бодных членов устройства, сумматор 4, блок 5 анализа, формирователь 6 им,пульсов и синхронизатор 7. Каждый 20 блок 1 вычислений содержит первый фик сирующий регистр 8, умножитель 9, сумматор 10, с второго по четвертый фиксирующие регистры 11, 12, 14 и элемент

13 задержки. 25

Устройство работает следующим образом.

Формирователь 6 импульсов генерирует управляющие импульсы для блоков

1 вычислений через каждые и тактов. 30

За начальные значения компонент векто-. ра неизвестных принимаются значения, зафиксированные в блоках 1 после вклю чения устройства. Решения системы уравнений (с точностью, которая задается ,пороговым значением) начинается с при ! ходом первого тактового импульса, поступающего из блока 7 синхронизации.

На каждом такте работы устройства в .каждом блоке 1 реализуется операция 40 умножения числа, находящегося на втором информационном входе блока 1> и ,числа, записанного в фиксирующем реги стре 8 блока 1.

Параллельно с операцией умножения 45 выполняется сложение значений, поступающих на первый и четвертый информационные входы блока 1. В каждом текущем такте работы устройства на четвертый информационный вход i-го блока 1 поступает произведение чисел, полученное на предыдущем такте в (i-1)-м блоке 1. На четвертыи информационный вход первого блока 1 всегда поступает логический "0", В каждом элементе 13 задержки происходит задержка на два такта. В качестве элемента задержки можно использовать сдвигающий регистр.

Блок 5 анализа предназначен для покомпонентной проверки точности решения системы линейных алгебраических уравнений и выработки признака получения решения системы. В блоке 5 вычисляется разница х ", — х, (K) (k- 4»

1 значений компонент вектора неизвестных, полученных на k-й и (k-1)-й итерациях, и сравнивается с заданным по . рогом точности. Компоненты текущего вектора решения поступают в блок 5 анализа с выхода сумматора, а компоненты предыдущего вектора решения - с выхода n-ro блока 1. При удовлетворе нии всеми парами х . и х . эадан1 ной точности с выхода результата устройства снимаются значения вектора неизвестных.

Формула изобретения

1. Устройство для решения систем линейных алгебраических уравнений, содержащее с первого по и-й блоки вычислений (где n — порядок решаемой системы линейных алгебраических уравнений), блок анализа и блок синхронизации, причем вход элементов вектора свободных ленов устройства подключен к первому информационному входу первого блока вычислений, первый выход

i-ro блока вычислений (где i = 1,...п-1) подключен к первому информационному входу (i+1)-го блока вычислений, входы с первого по и-й элементов матрицы коэффициентов устройства подключены соответственно к вторым информационным входам блоков вычислений с первого по п-й, вход значения, точности устройства подключен к первому информационному входу блока анализа, выход которого подключен к выходу признака завершения вычислений устройства, вход запуска которого подключен к входу запуска блока синхронизации, выходы с первого по (п+1)-й ко— торого подключены соответственно к входам синхронизации блоков вычислений с первого по и-й и блока анализа, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, оно содержит сумматор и формирователь им пульсов, причем второй, третий и чет вертый выходы i-ro блока вычислений подключены соответственно к третьЕму информационному управляющему и к четвертому информационному входам (i+1)го блока вычислений, первый, второй и

16157

Фиа 2

Составитель В. Смирнов

Редактор А. Козориэ Техред Л.Сердюкова Корректор A.. 0сауленко

Заказ 3989 Тираж 569 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35,. Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 четвертый выходы и-ro блока вычислений подключены соответственно к первому информационному входу сумматора, к вторым информационным входам блока анализа и сумматора, выход которого подключен к третьим информационным входам блока анализа и первого блока вычислений и к выходу результата устройства, вход начальной установки ко- 1р торого подключен к входу режима формирователя импульсов, выход которого подключен к управляющему входу первого блока вычислений, четвертый информационный вход которого подключен к 15 входу нулевого потенциала устройства, (n+2)-й выход блока синхронизации подключен к входу синхронизации формирователя импульсов.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок вычислений содержит с первого по четвертый фиксирующие регистры, сумматор, умножитель и элемент задержки, причем первый и второй информационные входы 25 блока вычислений подключены соответственно к первым ин4юрмационным входам сумматора и умножителя, управляю39 6 щий вход блока вычислений подключен к входу записи-считывания первого фиксирующего регистра и к информаци- . онному входу элемента задержки, третий информационный вход блока вычислений подключен к информационным входам второго и первого фиксирующих регистров, выход которого подключен к второму информационному входу умножителя, выход которого подключен к информационному входу третьего фиксирующего регистра, четвертый информационный вход блока вычислений подключен к второму инфор— мационному входу сумматора, выход которого подключен к информационному входу четвертого фиксирующего регистра, вход синхронизации блока вычислений подключен к входам записи-считыва-. ния второго, третьего и четвертого фиксирующих регистров и к входу синхронизации элемента задержки, выходы второго, третьего и четвертого фиксирующих регистров подключены соответственно к второму, четвертому и первому выходам блока вычислений, третий вы" ход которого подключен к выходу элемента задержки.