Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах преобразования формы информации. Изобретение позволяет повысить точность. Это достигается тем, что в устройство, содержащее блок 6 формирования уровней квантования, квантователь 8, регистр 13, преобразователь 10 напряжение-код, регистр 18, блок 12 управления, генератор 1 парафазных сигналов введены коммутаторы 4, 5, блоки 2, 3 задержки, блок 7 формирования уровней квантования, квантователь 9, преобразователь 11 напряжение - код, регистр 14, блоки элементов И 15, 16, элемент ИЛИ 17. 1 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН (q1) 5 Н 03 М 1/36

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

{21) 4427131/24-24 (22) 16.05.88 (46) 23.12.90. Бил. № 47 (71) Институт кибернетики им. В.М.Глушкова (72) П.С.Клочан и Б.Н.Лаврентьев (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 762170, кл. Н 03 М 1/52, 1976.

Авторское свидетельство. СССР № 892704, кл. Н 03 М 1/52, 1977. (54) АНАЛОГО-ЦИФРОБОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к вычисли2 тельной технике и может быть использовано в системах преобразования формы информации. Изобретение позволяя е т повысить точность. Это д о стигаетсч тем, что в устройство, содеръ..аще блок 6 формирования уровней квантования, квантоват ель 8, регистр

13, преобразователь 10 напряжениекод, регистр 18, блок 12 управления, генератор 1 нарафазньх сигналов введены коммутаторы 4, 5, блоки 2, 3 задержки, блок 7 формирования уровней квантования, квантователь 9, преобразователь 11 напряжение — кОд, регистр 14, блок элементов И 15, 16 элемент ИЛИ 17. 1 з.п. ф«Jihl> 4 ил.

1615885

50

Изобрет-=-;í:í"=- относится к вычислительной технике и может быть использованс :-, системах преобразования формы информации ь

Цель изобр ет ения — повышение точнос" и

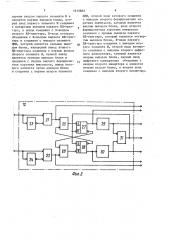

На фиг, 1 приведена функционал:ьная схема преобразователя, на фиг. 2 = функциональная схема блока управления, на фиг. 3 и 4 — временные ,диаграммы работы преобразователя, Пр еобразователь (фиг,1) содержит генератор 1 парафазных сигналов, блоки 2 и 3 задержки, коммутаторы 4

:и 5, блоки 6 и 7 формирования уров .ней квантования„квантователи 8 и 9, : преобразователи 10 и 11 напряжение— код, блок 12 управления, регистры

13 и 14, блоки 15 и 16 элементов И, элемент ИЛИ 17, регистр 18, шину 19 преобразуемого сигнала, выходную шину 20.

Блок управления (фиг. 2) содержит цифровые компараторы 2I и 22, инверторы 23 и 24, элементы И. 25 и 26, RS-триггеры 27 и 28, формирователи

29 и 30 коротких импульсов, элемент ,ИЛИ 31, На диаграммах (фиг. 3 и 4) обознаI чено: q и q+ — уровни квантования 1, :квантователя 8", q, qq — уровни квантования квантователя 9, 1, 1 — па рафазные сигналы генератора 1; 1, Ъ| ! 1 — эти же задержанные сигналы, Аналого-цифровой преобразователь

: работает следующим образом.

В исходном состоянии на выходах генератора 1 сигналы отсутствуют, :на выходах блоков 6 и 7 установлены уровни квантования, которые воздействуют на первые входы соответственно квантователей 8 и 9. На вторые входы квантователей 8 и 9 воздействует преобразуемый сигнал.

Преобразование начинается с появлением сигналов на выходах генератора 1. Сигнал с первого выхода генератора 1 поступает через первый канал коммутатора 4 на вход блока 6 и вход преобразователя 10. Этим сигналом модулируются уровни квантования квантователя 8. Одновременно с этим с второго выхода генератора 1 через первый канал коммутатора 5 на вход блока 7 и вход преобразователя

11 поступает сигнал „парафазный сигналу на первом выходе генератора 1.

Этим сигналом модулируются уровни квантователя 95

25 з0

55

В момент равенства преобразуемого сигнала с одним из модулированных уровней происходит переключение соответствующего компаратора квантователя 8 или квантователя 9, На выходе соответствующего . квантователя, например на выходе квантователя 8, изменяется сигнал. Этот сигнал воздействует на первый вход блока 12. Под воздействием этого сигнала на первом выходе блока 12 появляется импульс, стр обирующий пр еобраз ователь 10 и регистр 13, в результате чего цифровое значение квантованной величины пр еоб раз уемог о сиг нала считывается из квантователя 8 и записывается в регистр 13, где осуществляется также дешифрация унитарного кода в параллельный двоичный код. Одновременно с этим преобразователем 10 определяется цифровое значение вспомогательного сигнала, соответствующее его величине в момент срабатывания компаратора квантователя 8. Под воздействием импульса с третьего выхода блока 1 2 на третий вход блока 1 5 пифровые значения с выхода преобразователя 10 и регистра 13 поступают через блок 15 и элемент ИЛИ t7 на регистр

18. Запись результата аналого-цифрового преобразования в регистр 18 осуществляется при появлении импульса на седьмом выходе блока 12.

Перед появлением импульса на седьмом выходе блока 12 импульсом на пятом выходе этого олока коммутатор 4 переключается на второй канал. Начинается новый цикл аналого-цифрового преобразования, в котором аналогоцифровой преобразователь работает аналогично рассмотренному.

В случае, если в первом цикле аналого-цифрового преобразования пер еключение соответствующего компаратора квантователя 9 происходит раньше, чем переключение соответствующего компаратора квантователя 8, то отличием от рассмотренного в работе аналого-цифрового преобразователя будет лишь то. что управляющие сигналы будут появляться соответственно на втором входе, втором, четвертом и шестом выходах блока 12 и воздействовать на соответствующие входы соответственно преобразователя 11, регистра 14,,блока 16 и коммутатора 5„.

После окончания второго цикла начинается третий цикл аналого-циф5

1 рового преобразователя и т.д. В кон= це каждого цикла осуществляется переключение каналов коммутатора 4 последовательно с первого канала на второй, с второго на третий и т.д. и, наконец, в последнем цикле

a.-ro канала на первый канал после каждого срабатывания компараторов квантователя 8 и аналогичное переключение каналов коммутатора 5 после каждого срабатывания компараторов квантователя 9. За период изменения вспомогательных сигналов генератора 1 на выходе аналого-цифрового преобразователя будет получено и цифровых .отсчетов, где n — число сдвинутых по фазе вспомогательных сигналов или, что то же самое, количество каналов коммутатора 4 или 5.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий первый блок формирования уровней квантования, выход которого соединен с первым входом первого квантователя, второй вход которого является шиной преобразуемого сигнала, а выход соединен с информационным входом первого регистра и первым входом блока управления, первый выход которого соединен со стробирующим входом первого регистра, второй регистр, выходы которого являются выходной пиной, генератор парафазных сигналов, первый преобразователь напряжение — код, о т— личающийсятем,что,сцелью повышения точности, в него введены два секционированных блока за держки, два коммутатора, второи блок формирования уровней квантования, второй квантователь, второй преобразователь напряжение — код, два блока элементов И, элемент ИЛИ и третий регистр, причем первый выход генератора парафазных сигналов соединен с первым информационным входом первого коммутатора и входом первого блока задержки, выходы которого соединены с соответствующими вторыми информационными входами первого коммутатора, второй выход генератора парафазных сигналов соединен с первым информационным входом второго коммутатора и входом второго блока . задержки, выходы которого соединены б 15885 6 с соответствующими вт-ipbIMH информационньпя вхоцамн втопогс коммутатора, выход которого через второй блок

5 формирования уровней квантования соединен с первым входом второго квантователя H непосредственно с информационным входом первого преобразователя напряжение — код, выход первого коммутатора соединен с входом первого формирователя уровней квантования и информационным входом второго преобразователя напряжение— код, стробирующнй вход которого соединен с первым выходом блока управления, а выходы соединены соответственно с первьии входами первого блока элемента И, второй вход блока управлнния объединен с информационным входом третьего регистра и соединен с выходом второго квантователя, второй вход которого объединен с вторым входом первого квантователя, второй выход блока управления соеди нен со стробируемыми входами первогo преобразователя напряжение — код и третьего регистра„выход которого и выходы первого преобразователя напряжение — код соединены соответствен . о с первьпы и вторыми входами второго блока элементов И, выходы первого регистра соединены с соответствующими вторыми входами первого блока элементов И, третьи входы первого и второго блоков элементов И соединены соответственно с третьим и четвертым вькодами блока управления, .пятый и шестой выходы которого соединены соответственно с управляю40 щими входами первого и второго коммутаторов, выходы первого и второго блоков элементов И соединены через элемент ИЛИ с информационным входом второго регистра, стробирующий вход

45 которого соединен с седьмым выходом . блока управления.

2. Преобразователь по п. l о т— л и ч а ю шийся тем, что блок управления выполнен на элементе ИЛИ, gg двух формирователях коротких импульсов, двух RS-триггерах, двух элементах И, двух цифровых компараторах и двух инверторах, первый зход первого инвертора объединен с первым входом первого цифрового компаратора и является первым входом блока, а выход инвертора соединен с вторым входом цифрового компаратора, выход которого соединен г

1615885 первым входом первого элемента И и я:вляется первым выходом блока, второй вход первого элемента И. соединен с инверсным выходом первого RS-. òðèãгера, а выход соединен с S-входом второго RS-триггера, R-вход которого объединен с R-входом первого RS-триггера и соединен с выходом элемента который является седьмым выходом блока, инверсный выход второго

PS-триггера соединен с первым входом второго элемента И, прямой вьиод является третьим выходом блока и соединен с входом первого формирователя коротких импулъсов, выход которого является пятым выходом блока и соединен с первым входом элемента

ИЛИ, второй вход которого соединен с выходом второго формирователя коротких импульсов, который является

5 шестым выходом блока, вход второго формирователя коротких импульсов соединен с прямым выходом первого

RS-триггера, который является четвертым выходом блока, S-вход первого

RS-триггера соединен с выходом вто- рого элемента И, второй вход которого соединен с выходом второго цифрового компаратора, который является вторым выходом блока, первый вход цифрового компаратора . объединен с входом второго инвертора и является вторым входом блока, а второй вход соединен с выходом второго инвертора.

1615885

1615885

Составитепь А,Титов

Техред M,Äèäb!ê

Редактор Н. Тупица

Корр ектор Л, Бескид

Заказ 3996 Тираж 666 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101