Устройство для преобразования последовательного кода в параллельный

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к внешним периферийным устройствам ЭВМ, работающим в биполярном коде с использованием преобразования биполярного кода в параллельный, и может быть использовано для вывода информации с ЭВМ непосредственно на цифропечатающее или графопостроительное устройства. Изобретение позволяет упростить конструкцию устройства для преобразования последнего кода в параллельный. Устройство содержит формирователи 1 и 16 импульсов, сдвигающий регистр 2, преобразователь 3 биполярного кода в униполярный, триггеры 4 и 5, элементы И 6, 7 и 8, элемент ИЛИ 9, выходной регистр 10, генератор 11 импульсов, инверторы 12, 13 и 14, клавишный регистр 15, передатчики 17 и 18. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (gi)5 Н 03 М 9/00 ей О(!3 ). ;6

)ATE8T . 3," ."

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

r10 ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

0РК ГКНТ СССР (21) 4466771/24-24 (22) 20.06.88 (46) 23.12.90. Бюл. ¹ 47 (72) В.И.Ковнир и В.А.Ходжаев (53) 621.314(088.8) (56) Авторское свидетельство СССР

Ф 1231613 кл. Н 03 М 9/00, 1984.

Авторское свидетельство СССР

9 1418911, кл. Н 03 М 9/00, 1987.

{54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНцй (57) Изобретение относится к вычислительной технике, а именно к внешним периферийным устройствам 3BN, работающим в биполярном коде с использоÄÄSUÄÄ 1615893 А 1 ванием преобразования биполярного кода в параллельный, и может быть использовано для вывода информации с

ЭВМ непосредственно на цифропечатающее или графопостроительное устройства. Изобре ение позволяет упростить конструкцию устройства ппя преобразования последовательного к.да в параллельный. Устройство содержит формирователи 1 и 16 импульсов, сдвигающий регистр 2, преобразователь 3 биполярного кода в униполярный, триггеры 4 и 5, элементы И 6, 7 и 8, элемент ИЛИ 9, выходной регистр 10, генератор. 11 импульсов, инверторы 12, 13 и 14, клавишный регистр 15, передат- с чики 17 и 18, 1 ил.

1615893

Изобретение относится к вычислительной технике, а именно к внешним периферийным устройствам ЭВМ, работающим в биполярном коде с использованием преобразования биполярного кода в параллельный, и может быть использовано для вывода информации с ЭВМ непосредственно на цифропечатающие нли графо.построительные устройства. 10

Целью изобретения является упрощение устройства.

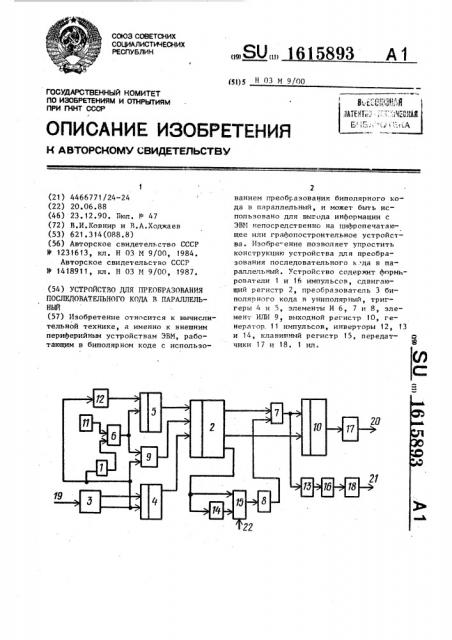

На чертеже представлена функцио1 нальная схема устройства.

Устройство содержит первый формирователь 1 импульсов, сдвиговый ре1 ,гистр 2, преобразователь 3 биполярного кода в униполярный первый 4 и

:второй 5 триггеры, первый 6, второй

7 и третий 8 элементы И, элемент ИЛИ Що

9, выходной регистр 10, генератор 11 импульсов, первый 12, второй 13 и третий 14 инверторы, клавишный регистр

15, второй формирователь 16 импульсов, первый 17 и второй 18 передат- 25 чики, информационный вход 19, инфор мационный выход 20, синхронизирующий выход 21 и задающий вход 22.

Устройство работает следующим об- разом. ЗО

При включении питания запускается, генератор 11 и импульсы начинают по- ступать на вход элемента И 6. В начальный момент при отсутствии биполярного кода на вход 19 преобразова3 tt теля 3 биполярного кода в униполярный на выходе синхронизации и на выходе данных устанавливаются нулевые потенциалы. С первого выхода синхронизации преобразователя 3, нулевой потенциал поступает на вход элемента ИЛИ 9, на вход инвертора 12, с выхода которого потенциал„ соответст-, вующий логической "1", устанавливается на входе установки триггера 5. В д5 случае отсутствия частоты с выхода синхронизации преобразователя 3 на входе формирователя 1 импульсов устанавливается нулевой потенциал, а с выхода формирователя 1 импульсов потенциал, равный логической "1", поступает на вход элемента 6, являясь при этом разрешающим для частоты, поступающей на вход элемента И 6 с генератора 11. Таким бразом, импульсы поступают с выхода элемента

И 6 на счетный вход триггера 5, при этом на выход триггера 5 перезаписывается потенциал логического "Ott, тановленного на входе данных триггера 5. Указанный потенциал устанавливается на входе регистра 2.

Частота с выхода элемента И 6 через элемент ИЛИ 9 поступает на счетный вход регистра 2. Однако записи информации в регистр 2 не происходит, так как на входе выбора режима все время установлен нулевой потенциал.

При поступлении биполярного кода на вход преобразователя 3 биполярного кода с его выхода синхронизации на- чинают поступать импульсы пачкой по

32 штуки. Каждому импульсу соответствует один бит информации — логический "0" или логическая"1". Первым пришедшим импульсом синхронизации, поступающим на вход триггера 5 с выхода инвертора 12 на выходе триггера

5 устанавливается уровень логической

tt tt

1, которыи поступает на вход регистра ?.

Этот импульс запускает формирователь f импульсов, на выходе которого устанавливается потенциал логического "0", запрещающий прохождение частоты с первого входа элемента И 6 на его выход. На входе элемента ИЛИ 9, подключенном к выходу элемента И б, устанавливает;я уровень логическоF t10tt

С другого входа эле:1ента ИЛИ 9 на его выход проходит первый импульс синхронизации с выхода преобразователя 3 и поступает на счетный вход регистра 2. Таким образом, по переднему фронту первого импульса синхронизации на входе регистра 2 устанавливается логическая "1", и по мере поступления этого фронта на счетный вход регистра 2 первый выходной разряд регистра 2 устанавливается в

"0", остальные тридцать один разрядв состояние логической "1".

По заднему фронту первого импульса синхронизации первый бит информации с информационного выхода преоб" разователя 2 на вход данных триггера

4 перезаписывается íà его выход. Ta" ким образом, первым импульсом синхронизации первый бит информации записывается в триггер 4 и устанавливается в исходное состояние регистр 2.

Положительным передним фронтом второго импульса синхронизации, поступающим на вход формирователя 1 им пульсов, последний перезапускается и на его выходе продолжает поддержи5 16158 ваться уровень логического "0", запре. щающего прохождение частоты с входа элемента И 6 на его выход.

Этим положительным (передним) франс том первый бит инАармации, записанный в триггере 4 и установленный на входе данных регистра 2 предыдущим импульсом синхронизации записывается в первый разряд регистра 2. На втором выходном разряде регистра 2 при этом устанавливается логический "0".

По отрицательному Аранту второго импульса второй бит информации записывается в триггер 4 и устанавливается на входе данных регистра 2.

Подобным .. образом третьим импульсом синхронизации запускается формирователь 1. Положительным Аронтом третьего импульса в регистр 2 20 записывается второй бит информации, а отрицательным Аронтом в триггер 4— третий бит инАармации. Тридцать ВТо ,рым импульсом в тридцать первом разряде регистра 2 устанавливается тридцать первый бит инАормации и в триггер 4 записывается тридцать второй, последний бит. Далее следует пауза.

На входе формирователя 1 импульсов устанавливается нулевой потенциал, а с его выхода ня вход элемента И 6 поступает потенциал логической "1", разрешающей прохождение частоты с входа элемента И 6 на выход. Положительным фронтом первого импульса частоты, поступающей с выхода элемента И 6 на вход элемента ИЛИ 9 и с его выхода,на счетный вход регистра 2 тридцать второй бит информации, записанный в триггере 4, перезаписывает- 4 ся в регистр 2 и устанавливается на тридцать втором входе регистра 2.

Тридцать третий. разряд регистра 2 устанавливается в "0". Отрицательным фронтом первого импульса, поступив- 45 шего с выхода элемента И 6 на счетный вход триггера 5, на выходе последнего устанавливается нулевой потенциал, записанный на входе триггера 5 °

Нулевой потенциал с выхода триггера 5 поступает на вход регистра 2.

Процесс преобразования закончен.

Непременное условие работы устройства состоит в том, что частота генератора 11 должна быть соизмерима с о,-периодом частоты синхронизации.Кроме того, длительность импульсов, Аормируемых Аормирователем 1, должна быть больше или равна с . Таким.обрал зам, чтобы ня выходе Аарииранателя 1 при наличии частоты синхронизации все время был установлен потенциал, запрещающий в момент прохождения частоты синхронизации прохождение частоты генератора 11 с входа элемента Й 6 на ее выход. Такимсбрязом, каждое информационное тридцятидвухразрялнае слова, пг ступающеее ня информационный вход 19, выставляется на выходе регистра 2 °ИнАармяцианняя часть этого слова устанавливается на входах данных выходного регистра 10. При этом каждое слово сопровождается импульсам синхронизации, который поступает с тридцать третьего выхода регистра ?.Передний франт указанного импульса формируется после установки тридцать второго бита инАормации, а задний франт Аармируется после сброса регистра 2 па приходе второго импульса с генератора 11 на счетный вход регистра 2.

Первые восемь разрядов инАармацианного слова дешиАрируются с помощью двоична-десятичного дешиАрятора, собряннага на клавишном регистре 15, элемент И 8 схемы, который предстазляет собой расширители„ и инвертаре 14. Перед началом работы на клавишном регистре 15 устанавливается выбранный адрес слова, предстявленнога биполярным кодам.

Ня инАормационный вход 19 устройства поступают биполярные коды с различными адресами, так как характер этой инАармации различный и каждый параметр имеет свой адрес.

ИнАармация, которую необходимо выделить, имеет свой заранее опредеI ленный адрес. Именно этот адрес и устанавливается на клавишном регистре 15. Представляя собой набор независимых тумблеров, клавишный регистр

15 замыкает выходы регистра 2 на входы элемента И 8 либо няпрямую,либо через инвертор 14, таким образом, чтобы на входах элемента И 8 при появлении выбранного адреса устанавливались уровни логических "1". В этом случает на выходе элемента И 8 Аормируется потенциал, который поступает на вход элемента И 7, последний разрешает прохождение с ега второго входа импульса синхронизации на выход элемента И 7 и далее ня счетньп вход выходного регистра 10. Е этому

1615893

Составитель Б.Ходов

Редактор М.Бланар Техред М,Дидык .

КоРРектоР В.Гирняк

Заказ 3997 Тираж 656 Подписное

ВНЯИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101 моменту на входах данных регистра 10 установлена информационная часть бишолярного кода, которая и записывается поступающим с выхода элемента

И 7 одиночным импульсом.

С выхода регистра 10 информация через передатчик 17 устанавливается на информационном выходе 20 устройства.

,Одновременно с этим импульс синхр низации с выхода элемента И 7 пост пает на вход инвертора 14 и с его вы ода на вход формирователя 16 импу ьсов, который выделяет задний фр нт импульса синхронизации и формиру т второй иммпульс синхронизации, поступающий через передатчик 18 на вы од 21 синхронизации устройства.

ФОрмула изобретения, Устройство для преобразования последовательного кода в параллельный, содержащее первый формирователь им- 25 пульсов, сдвиговый регистр, преобразователь биполярного кода в униполярный, вход которого является инфо мационным входом устройства, триггеры, элементы И, элемент ИЛИ, выход- ур нок регистр и генератор импульсов, выкод которого соединен с первым входом первого элемента И, о т л и ч аю щ е е с я тем, что, с целью упрощения устройства, в него введены инве5 торы, клавишный регистр, второй формирователь импульсов и передатчики первый выход преобразователя бипоЛярного кода в униполярный соединей.с входом данных первого тригге- @> ра, выход которого соединен с входом

4 данных сдвигового регистра, первый выход которого соединен с входом данных выходного регистра, выход которого соединен с входом первого передатчика, второй выход преобразователя биполярного кода в униполярный соединен со счетным входом первого триггера, с первым входом элемента

ИЛИ, с входом первого формирователя импульсов И, через первый инвертор с входом установки второго триггера, выход которого соединен с входом установки сдвигового регистра, второй выход которого соединен с первым вхо дом второго элемента И, выход которого соединен непосредственно со счетным входом выходного регистра и через второй инвертор с входом второго формирователя импульсов, выход которого соединен с входом второго передатчика, выход первого формирователя импульсов соединен с вторым входом первого элемета И, выход которого соединен со счетным входом второго триггера и с вторым входом элемента ИЛИ, выход которого соединен со счетным входом сдвигового регистра, третьи выходы которого соединены непосредственно с первыми входами клавишного регистра и через третий инвертор с вторыми входами клавишного регистра, третий вход которого является задающим входом устройства, выходы кла" вишного регистра соединены с входами третьего элемента И, выход которого соединен с вторым входом второго элемента И, выходы первого и второго передатчиков являются соответственно информационным и синхронизирующим выходами устройства.