Многоканальное измерительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может применяться в информационно-измерительных системах, системах автоматического регулирования и управления для измерения амплитудного значения и фазового сдвига периодических сигналов. Целью изобретения является упрощение устройства, повышение помехозащищенности устройства путем полного подавления высших гармонических составляющих входных сигналов, причем это подавление не зависит от входных сигналов по отношению к периоду интегрирования. Многоканальное измерительное устройство содержит аналоговый коммутатор 3, аналого-цифровой преобразователь 4, блок 9 управления, формирователь 11 опорных напряжений, генератор 12 импульсов, делитель 13 частоты, группу коммутаторов 1, каждый из которых содержит два р-входовых мультиплексора 2, преобразователи напряжения 6, каждый из которых содержит два аналоговых перемножителя 7 и два интегратора 8, буферный регистр 5, счетчик 10 с входами предварительной установки. В устройстве обеспечивается возможность анализа фазового сдвига входных сигналов относительно опорного напряжения. 8 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 3/05

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4618786/24 (22) 09.12.88 (46) 30 ° 12.90. Бюп. N - 48 (71) Московский институт электронной техники (72) lO.Â.Ñàâ÷åíêî, А.С.Глущенко, А.Н.Чуняев, В.Б, Кудряшов и В.А.Маркин (53) 681.327.12 (088.8) (56) Авторское свидетельство СССР

N - 1403057, кл. G 06 F 3/05, 1986.

Авторское свидетельство СССР

У 1170444, кл. С 06 F 3/02, 1983. (54) МНОГОКАНАЛЬНОЕ ИЗМЕРИТЕЛЬНОЕ

УСТРОЙСТВО (57) Изобретение относится к измерительной технике и может применяться в информационно-измерительных системах, системах автоматического регулирования и управления для измерения амплитудного значения и фазового сдвига периодических сигналов. Целью изобретения является упрощение устЖ 1

„„SU„„1617430 я1

2 ройства, повышение помехозащищенности устройства путем полного подавления высших гармонических составляющих входных сигналов, причем э;о подавление нс зависит от входных сигналов по отношению к периоду интегрирования. Многоканальное измерительное устройство содержит аналоговый коммутатор 3, аналого-цифровой преобразователь 4, блок 9 управления, формирователь 11 опорных напряжений, генератор 12 импульсов, делитель 13 частоты, группу коммутаторов I каждый из которых содержит два р-входавых мультиплексора 2, преобразователи чапряжения 6 каждый их которых содержит

Р два аналоговых перемножителя. 7 и два интегратора 8, буферный регистр 5, счетчики 10 с входами предварительной установки. В устройстве обеспечивается воэможность анализа фаэового сдвига входных сигналов относительно опорного напряжения. 8 ил.

16 Я430

Изобретение относится к измерительной технике и может быть применено в информационно-измерительных системах, системах автоматического регулирования и управления для измерения амплитудного значения и фазового сдвига периодических сигналов.

Цель изобретения — упрощение и повышение помехозащищенности устройства.

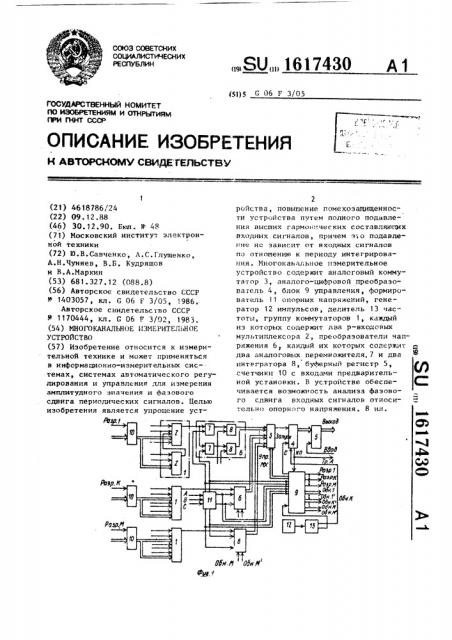

На фиг.1 представлена структурная". схема многоканального измерительного устройства; на фиг.2 — схема интегратора; на фиг.3 — схема блока управления; на фиг.4 — 8 — временные диаграммы, иллюстрирующие работу устройства.

Многоканальное измерительное устройство состоит из группы аналоговых коммутаторов 1, каждый из которых содержит два р-входовых муЛьтиплексоров 2, (р-1) входов первого и р входов второго мультиплексоров являются входами устройства, р-й вход первого мультиплексора соединен с выходом второго аналогового коммутатора 3, аналого-цифрового преобразователя (АЦП) 4, буферного регистра 5, преобразователей 6 напряжения, каждый из которых содержит два аналоговых перемножителя 7 и два интегратора 8, блока 9 управления, счетчиков 10, формирователя 1! опорных напряжений, генератора 12 импульсов и делителя 13 частоты.

Интегратор 7 (фиг. 2) содержит первый резистор 14. операционный усилитель 15, конденсатор 16, электронный ключ 17 и второй резистор 18.

На фиг,2 обозначен также вход 19 электронного ключа.

Аналого-цифровой преобразователь выполнен по схеме АЦП поразрядного уравновешивания.

Блок 9 управления содержит шесть компараторов 20, три элемента ИСКЛЮЧАОЩЕЕ ИЛИ 2 1, четвертый 22 и пятый

23 ИЛИ 22, пятый элемент . ИСКПЮЧАЮIIIEE NJIH, дешифратор 24, делитель 25 частоты на 13, первую группу выходов

26 блока управления, блок элементов

ИСКЖОЧАЮЩЕЕ ИЛИ 27, первый триггер

28, первый элемент HE 29, счетчик 30, второй элемент НЕ 31, второй триггер ,32, первую группу элементов 2И-HE 33, вторую группу выходов 34 блока управления, группу элементов HE 35> элемент 2И-НЕ 36, первый вход 37 блока управления, шестой элемент ИСКПОЧАЮЦ ЕЕ ИЛИ 38, выход 39 блока управления, третий элемент НЕ 40, вторую группу элементов 2И-НЕ 41, третью группу выходов 42 блока управления, группу элементов НЕ 43, второй вход

44 блока управления, узел 45 управления и четвертую группу выходов 46 блока управления.

Блок 27 и узел 45 управления разрабатываются с использованием известных методов синтеза цифровых автоматов на основе временной диаграммы работы устройства.

Формирователь 11 опорных напряжений содержит шесть формирователей опорных напряжений. Первый, третий и пятый формирователи выполнены по схеме инвертирующего усилителя, а второй, четвертый и шестой формирователи - по схеме двухвходового инвертирующего сумматора. Вход перного, первый вход второго, второй вход

25 шестого формирователей объединены с входом напряжения первой фазы. Второй вход второго, вход третьего, первый вход четвертого формировате-. лей обьединены с входом напряжения второй фазы. Второй вход четвертого вход пятого, первый вход шестого формирователей объединены с входом напряжения третьей фазы.

Устройство работает следующим образом.

Измеряемые сигналы U U подаются на входы устройства.

Входные сигналы можно представить. в виде:

Ц,= +Uqsin(kQt + P ), к= где k — номер гармонической составляющей входного сигнала, 45 k = 1,2... °, Я вЂ” угловая частота основной гармонической составлякицей;

f — фазовый сдвиг относительно опорного напряжения.

Формирователь 11 вырабатывает шесть сигналов опорных напряаений

Uoni Н (фиг.4 а,б), представляющих собой синусные и косинусные сигналы трехфазных напряжений А, В и С, которые поступают на его

55,„од.

Рассмотрим обработку входного сигнала на примере одного канала об. работки.

1617430

6 (н iIT> nhk а

«K Uo л

П (т+ь ) U совцг dt

U0 s Lngt э

"< = Кп Uî U()»«t1

arctg — т2

110 — 00 соарес .

Ul = К„U „U cosset (ni l) t i ft ht

s U„ sinQt dt п(т. 4С) К о

Ug

Ас

Коммутатор 1 поочередно подключает (р-1) входных сигналов первого мультиплексора 2, а затем один из р сигналов второго мультиплексора 2 к входу преобразователя 6 напряжений на время, равное периоду опорного напряжения через интервал времени

Дй.При этом три младших разряда счетчика 10 соединяются соответствующими адресными входами первого мультиплексора 2> а три пос.ледующих — с адресными входами второго мультиплексора. Затем этот цикл повторяется.

Первый мультиплексор предназначен для коммутирования быстро меняющихся сигналов, а второй — для медленно меняющихся сигналов. В первом леремно жителе 7 происходит умножение входного сигнала на сигнал опорного напряжения, которое можно представить в виде: где Uo — амплитудное значение опорного напряжения.

Выходной сигнал первого перемножителя можно представить в виде: где Kt, — коэффициент передачи перемножителя.

Во втором перемножителе 7 происходит умножение входного сигнала на сигнал опорного напряжения, которое можно представить в виде:

Выходной сигнал второго перемножителя можно представить в виде:

Сигналы U<, U поступают на входы двух интеграторов 8 соогветственно и интегрируются в интервалах времени от и (Т+ Дг) до (n+ 1) Т+

+ n Qt где n — 0,1,2,...

Выходные сигналы первого и второго интеграторов Я можно представить в виде: л где ь — постоянная времени интегратора, Сигналы Ug H U поступают на

I вход АЦП 4 через коммутатор 3 и пре10 образуются в цифровой код в интервалах от to до t и от t< до Сз соответственно (фиг.5). Обнуление первого и второго интеграторов 8 происхг .ит в интервалах от t до !

5 и о t q до t y соответственно (фиг.5), 1 „ля формирования этих интервалов используются поступающие в узел 45 управления сигналы = Обн.1,..., Обн.М, Обн. 1,...,Обн.M . Сигналы

Разр.1.. .,Pa",ð.М используются для стробирования cèãíàëîâ требуемого канала. Сигнал КП АЦП 4 при этом используется для запрета прохождения сигнала на АЦП 4.

Амплитудное значение сигнала определяется в ЦВМ по формуле:

30 Фазовый сдвиг сигнала относительно опорвого напряжения определяется по формуле:

Блок 9 управления вырабатывает сигналы разрешения Разр.1,..., 40 Разр.М (фиг.4в, r, д), которые подав ются с выходов 26 на входы разрешения соответствующих аналоговых коммутаторов I,ñèãíàëû обнуления Обн.1,...,Обн.М, Обн.i ... Обн.М (фиг.4е — л), кото4 рые подаются с выходов 34, 42 на входы 19 обнуления первых и вторых интеграторов преобразователей б соответ— ственно, сигнал "Запуск", который подается с выхода 39 на соответствующий вход АЦП 4 и сигналы управления

Упр.МХ, которые подаются с выходов 46 на входы управления аналогового коммутатора 3.

Рассмотрим формирование сигналов

Упр.MX для трехканального измерительного устройства, В этом случае в качестве аналогового коммутатора 3 может быгь использован мультиплексор

590КНб,имеюг ий восемь аналоговых

1617430

А2 = Разр.2

А4 = Разр.3 входов, Пусть на первый и второй входы мультиплексора поступают сигна" лы U< и П с первого канала на третий и четвертый - со второго канала, на пятый и шестой — с третьего канала. На фиг.8а приведена последовательность импульсов с выхода блока

27 для трех каналов. В интервале времени первого импульса происходит мультиплексирование и преобразование

f в цифровой код двух сигналов U и U< второго канала, в интервале времени

A1 = Раэр. 1 Q+ Разр. 2 9 Ра зр. 3

На вход разрешения мультиплексора может быть подан сигнал "Конец пре-,;, образования" (КП) с выхода АЦП 4.Функции А1, А2, А4 реализуются с, помощью известных логических

I элементОв инверсии и сложения по модулю 2 либо с помощью эашивки в ПЗУ.

После завершения преобразования в. цифровой код сигнала интегратора 8

AIUI 4 выдает сигнал низкого уровня

КП, который поступает на вход 44 блока управления и является выходным сигналом устройства требования прерывания "Тр.А". Генератор 12 импульсов вырабатывает сигнал тактовой

35 частоты, которая поступает на вход делителя частоты 13, с первого выхода которого сигнал синхронизации поступает на соответствующий вход АЦП 4, а со второго выхода делителя частоты 13 0 сигнал поступает на вход 37 блока управления. Ввод данных в ЦВМ осущест-1! вляется при наличии сигнала Ввод на управляющем входе буферного регистра 5.Входы предварительной установки счетчиков 10, выходы и вход управления регистра 5 и выход устройства

"Тр.А" соединяются с соответствующими разрядами шины ПВМ. Путем программного эаднния кода на входах предва5О рительной установки счетчиков 10 можно начинать опрос входных сигналов а какого угодно входа.

Блок 9 управления работает следующим образом.

Компараторы 20 из входных гармонических сигналов формируют прямоугольные импульсы (фиг.6 а — е)..

На выходе элемента 23 формируется второго импульса — двух сигналов третьего канала, в интервале времени третьего импульса — двух сигналов первого канала и т.д. В соответствии с этим и с таблицей истинности мультиплексора 590КН6 на адресные входы мультиплексора должны подавать" ся управляющие сигналы А1, А2, А4

/ (фиг.8б — r) . Сравнивая временные диаграммы фиг.4в — л и фиг.8б — г, мо>>-!!о записать:

У Обн ° i C) ",бч.". О+ Обн. 3 сигнал в виде меандра с длитель.— ностью импульсоз 30 он скваъностью, равной двум (фиг.б ж). Делитель 25 частоты делит частоту импул! "ов на

2. 4, 8 и считает цо 13. Де>пифратор

24 форм!руе! на своих выходах сигналы Разр.1,...,Разр.M (фиг.4 в — д) °

Эти сиг>!лг-а! суммируются н блоке 27 пс: моду>д 2 (фиг,(> з) .

Рассмотрим формирование сиг. алов

Обч.1...0бн.М, Обн.1,..., Г"н.М

Эапуск на примере одного интервала времени gt (см.фиг,.5).

На вход об»>уления счетчика 30 поступает разре!чающий счет сигнал низкого уровня с д!!ительностью, соответствующей интервалу времени ttt (фиг.7 а), На выходе ".÷åò÷èêà формиууетсл сигнал, показанный на фиг.7б.

Интервал ст до определяется произведением весового коэффициента выходнс .I разряда счетчика на период так",овой частоты, поступающей на вход 37 блока управления. Элементы

35 и 33 формируют один из сигналов

Обн. >,...,Îáí.М в зависимости от состояния дешифратора 24 (фиг,5е,7в).

По переднему фронту выходного сигнал«. блока 27 происходит формирование первого сигнала запуска с помощью триггера 28 и элемента 38. По переднему фронту сигнала синхронизации С (фиг.7r) и при наличии сигнала запуска нулевого уровня происходит запуск АЦП 4 и выход КП АЦП переходит в состояние высокого уровня, а через l2 тактов HG выходе АЦП (JopMH

l руется цифровой код, о чем свидетельствует переход выхода КП в состояние

1617430

10 низкого уровня (фиг, 7е) . При этом сигнал запуска снимается. По переднему фронту сигнала с выхода счетчика 30 происходит формирование второго сигнала запуска с помощью тригге5 ра 32 и элемента 38. Таким образом, на выходе элемента 38 за время Формируются два сигнала запуска АЦП (фиг.7д) и происходит преобразование в цифровой код двух сигналов преобразователя 6 ° Элементы 43 и 41 формируют сигналы обнуления Обн.1,..., Обн.M (фиг.7ж).

Таким образом, устройство позво- 1с ляет уменьшить аппаратурные затраты за счет уменьшения качества каналов обработки при одинаковом количестве входных сигналов. Кроме того, устройство позволяет повысить точность измерения за счет полного подавления высших гармонических оставляющих,. причем это подавление не зависит от фазового сдвига входных сигналов по отношению к периоду интегрирования. 25

Дополнительно становится возможным анализ фаэоього сдвига входных сигналов относительно опорного напряжения, что расширяет область применения устройства. 30

Формул а изобретения

Многоканальное измерительное устройство, содеРжащее коммутатор, аналого-цифровой преобразователь, блок управления, формирователь опорных напряжений, генератор импульсов, делитель частоты, выход коммутатора соединен с информационным входом àíà- 4р лого-цифрового преобразователя, выход блока управления соединен с входом запуска аналого-цифрового преобразователя, выход генератора импульсов соединен с входом делителя частоты, о т л и ч а ю щ е е с я тем, что, с целью упрощения и повьппения помехозащищенности устройства, в не— го введены группа коммутаторов, каждый из которых содержит два мультиплексора, информационные входы группы первого мультиплексора и информаци энные входы второго мультиплексора являются информационными входами устройства, выход второго мультиплексора соединен с информационным входом первого мультиплексора, счетчики, буферный регистр, преобразователи напряжения, каждый из которых содержит два перемножителя и два интегратора, первые входы перемножителей соединены с выходом первого мультиплексора соответствующего коммутатора группы, вторые входы перемножителей соединены с выходами формирователя опорных напряжений, выходы первог и второго перемножителей соединены с информационными входами соответственно первого и второго интеграторов, входы сброса которых соединены с соответствующими выходами первой группы блока управления, выходы интеграторов соединены с информационными входами коммутатоРа, адресные входы которого соедине— ны с выходами т< рой группы блока управления, тактовый вход которого соединен с первым выходом делителя частоты, второй выход которого сое— дпнен с синхрониэирующим входом аналого-цифрового преобразователя, выход; которого соединены с информационными входами буферн го регистра, выходы которого являют. я информационнымп выходами устройства, входы формирователя опорных напряжений подключены к шинам питания трехфазной сети, выходы формирователя опорных напряжений соединены с информационными входами блока управления, управляющий вход которого соединен с выходом конца преобразования аналогоцифрового преобразователя и является выходом требования прерывания устройства, управляющий вход буферного регистра является управляющим вхо— дом устройства, входы предварительной установки счетчиков являются адресными входами устройства, счетные входы счетчиков соединены с соответствующими выходами третьей группы бло" ка управления, выходы счетчиков соединены с адресными входами первого и второго мультиплексоров соответствующих коммутаторов группы, стробирующий вход первого мультиплексора каждого коммутатора группы соединен с соответствующим выходом третьей группы блока управления.

1Ы 7430

Фиг. 2 ЮЩ э д/33

00/ U

Рагр.

3 ри.";/7.к

0ар tf

1 Ь! 7430

= LJ

Аоод лврЮаео юма 20 а

Юяас7

3тараго кама 20 и . ад лрелье20каип.2

Фаад четВерп гака пг

Выд7У

Пгн1аа д ал.20

Ьиад

ШеСР)020 ка 20

Rind ц зл м 23 дьюаУ длака27

Фиг.6

Запуск

IN

Ин (Ожет

Яь O о О «Ю

Составитель И. Карнова

Редактор Л.Пчолинская Техред M.Äèäûê Корректор Л. Пилипенко

Заказ 4118 Тирам 575 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101