Трехфазный преобразователь частоты с непосредственной связью

Иллюстрации

Показать всеРеферат

Изобретение относится к области силовой преобразовательной техники и может быть использовано в электроприводах переменного тока. Целью его является улучшение качества тока в нагрузке за счет устранения бестоковых пауз. Преобразователь содержит регулирующие 2 - 7 и шунтирующие 33 - 38 тиристоры. Предлагаемый алгоритм управления реализуется системой управления 12 - 14, 39, 48, 49. 7 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

П9) (11) (я)з Н 02 М 5/27

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4379258/24-07 (22) 17.02.88 (46) 30.12.90. Бюл. М 48 (71) Ленинградский институт точной механики и оптики (72) П.С.Епифанов, А.А.Усольцев и В.И.Хрисанов (53) 621.314.27(088,8) (56) Авторское свидетельство СССР

N 780145, кл. Н 02 P 13/16, 1978.

Авторское свидетельство СССР

М 886180, кл. Н 02 P 7/42, 1980. (54) ТРЕХФАЗНЫЙ ПРЕОБРАЗОВАТЕЛЬ

ЧАСТОТЫ С НЕПОСРЕДСТВЕННОЙ

СВЯЗЬЮ (57) Изобретение относится к области силовой преобразовательной техники и может быть использовано в злектроприводах переменного тока. Целью его является улучшение качества тока в нагрузке за счет устране .ия бестоковых пауз. Преобразователь содержит регулирующие 2-7 и шунтирующие 33-38 тиристоры. Предлагаемый алгоритм управления реализуется системой управления 12 — 14, 39, 48, 49. 7 ил, 1617573

10

Изобретение относится к силовой преобразовательной технике и служит для регулирования частоты ocHQBHQA гармонической составляющей в трехфазной активно-индуктивной нагрузке, в частности может быть использовано в электроприеоде переменного тока для регулирования скорости вращения двигателя.

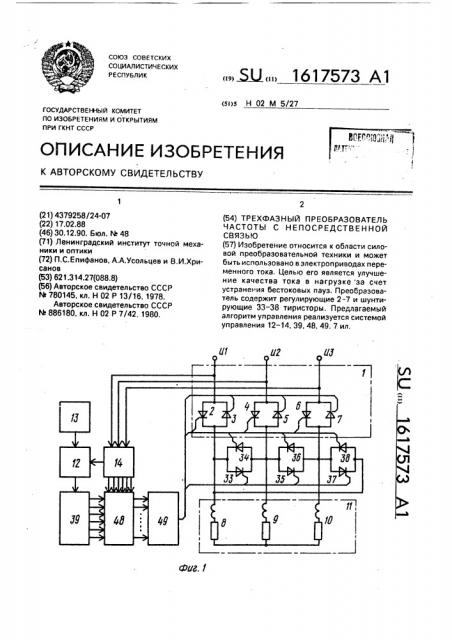

Цель изобретения — улучшение энергетических показателей за счет устранения бестоковых пауз и увеличения пульсности выходных токов и напряжений в трехфазной активно-индуктивной нагрузке, соединенной звездой без нулевого провода, На фиг. 1 изображена структурная схема трехфазного преобразователя частоты с непосредственной связью; на фиг. 2- то же, блока синхронизации; на фиг. 3 — то же, кольцевого сдвигового регистра; на фиг. 4— временные диаграммы работы блока синхронизации и кольцевого сдвигового регистра; на фиг. 5 — временные диаграммы напряжений и токов на выходе преобразоватЕля и сигналов управления тиристорами; на фиг. 6 — временные диаграммы напряжений и токов для случая соотношения частот питающей сети и частоты сигнала модуляции, равного 13; на фиг. 7 — пример реализации блока управления и делителя частоты.

Трехфазный преобразователь частоты с непосредственной связью (ПЧНС) включает в себя (фиг. 1) тиристорный коммутатор 1, содержащий шесть регулирующих тиристоров 2-7, соединенных попарно встречно-параллельно между собой и вклю енных о разрывы линейных проводов фаз 8-10 активно-индуктивной нагрузки 11, соединенной звездой беэ нулевого провода, делителя 12 частоты с переменным коэффициентом деления, управляющий вход которого соединен с выходом блока 13 управления, и лок 14 синхронизации, сетевыми входами соединенный с исто ievvou питания.

Блок 14 синхронизации (фиг. 2) содержит трансформаторы 15 — 17, первичные обмотки которых подключены треугольником к линейным проводам питающей сети, а вторичные обмотки через резисторы 18 подключены соответственно к одному из входов компараторов 19-21. Вторые входы компараторов через резисторы 22 подключены к точке нулевого потенциала. а еыходы— к входам элементов НЕ 23-25 и к входам дифференцирующих цепей 26. Выходы элементов НЕ 23-25 также присоединены к входам соответствующих дифференцирующих цепей 26, Выходы всех дифференцирующих цепей 26 объединены на элемент

ИЛИ 27, а его выход подключен к входу элемента 2 — И 28, другой вход которого подключен к выходу RS-триггера 29. Вход S триггера 29 через линию 30 задержки подключен к выходу элемента HE 25. Вход R триггера 29 через резистор 31 подключен к точке нулевого потенциала, а через конденсатор 32 — к источнику питания постоянного тока. Выход элемента 2-И 28 является тактовым выходом блока синхронизации и подключен к тактовому входу делителя 12 частоты (фиг. 1). Выходы компараторов 1921 и элементов HE 23 — 25 являются синхронизирующими оыходами блока 14 синхронизации.

Преобразователь содержит также шесть шунтирующих тиристоров 33-38, соединенных попарно встречно-параллельно между собой и подключеннь х треугольником к линейным проводам всех фаз нагрузки 11, Выход делителя 12 частоты (фиг. 1) подключен K входу кольцевого сдеигового регистра 39. В состав кольцевого сдвигового регистра входят (фиг. 3) шесть соединенных последовательно 0-триггеров 40-45, тактовые входы которых подключены к выходу делителя 12 частоты (фиг. 1). Входы S триггеров 40,44, 45 и входы R триггеров 41 — 43 через конденсатор 46 подключень; к источнику питания постоянного тока, а через резистор 47 — к точке нулевого потенциала.

Выходы триггеров 40-45 подключены к соответствующим управляющим входам логического блока 48, шесть синхронизирующих входое которого соединены с шестью соответствующими находами блока l4 синхронизации (фиг. 1).

Выходы логического блока 48 соединены с двенадцатью соответствующими входами блока 49 выходных формирователей, двенадцать выходов которого подключены к управляющим электродам, соответствующих регулируюгцих и шунтирующих тиристо ров.

Трехфазный преобразователь частоты с непосредственной связью работает следующим образом.

Блок 13 управления (фиг. 1) вырабатывает цифровой код N, соответствующий отношению и частоты питающей сети к частоте основной гармонической составляющей напряжения на выходе ПЧНС, определяемому выражением

n =- .Л1 = 6k+1 при k =1,2,3..., (1) где f — частота сетевого напряжения;

f> — частота основной гармонической составляющей выходного напряжения преобразователя.

Выбор кратности частот и, определяемый выражением (1) объясняется тем, что 61 573

50

55 при таких отнощениях в спектре гармоник отсутствуют составляющие, образующие обратную последовательность, С блока 13 управления ци- вовой код И поступает на управляющий вход делителя

12 частоты, осуществляющего деление в и раз частоты сигнала, поступающего на его тактовый вход с тактового выхода блока 14 синхронизации, Пример реализации блоков 12 и 13 приведен на фиг. 7, Делитель 12 частоты является известным устройством. На фиг. 7 он приведен в варианте, когда требуются преобразования управляющего двоичного кода

N в дополнительный код К = 2" — N, где К— число разрядов счетчика делителя, Блок 13 управления для приведенного делителя частоты может быть, например, переключа елем, имеющим число направлений, равное числу разрядов счетчика делителя частоты

12 и число положений, равное числу ступеней регулирования выходной частоты преобразователя. С его помощьго формируется дополнительный двоичный код числа N, соответствующего выражению (1). На фиг. 7 приведена схема устройства для двухступенчатого регулирования частоты с N> = 7 и

N2 = 13.

Блок 14 синхронизации (фиг. 2), на входы которого подается трехфазное напряжение питающей сети, вырабатывает импульсы при переходе линейных напряжений сети через нулевое значение, а также формируетлогические сигналы $гз. $2ч, $2з, Язг, Sat, Sta, единичное состояние которых соответствует положительной полуволне линейных напряжений 0ч2, 021, 02э, 0э2, 0зч, 01з питающей сети, т.е, 1

$ц = (1 + 0ц/ l Uki l) = Sit () где R = 1, 2, 3; I = 1, 2, 3; R e I.

Для этого линейные сетевые напряжения Uч2, 02з, 031 через трансформаторы 15, 16, 17, предназначенные для понижения сетевых напряжений до уровня, допускаемого входными цепями компараторов 19-21 и для гальванической развязки с питающей сетью, подаются на входы компараторов

19 — 21, На выходах компараторов 19-21 формируются логические сигналы $12, $2э.

$э1, единичное состояние которых соответствует положительной полуволне сетевых линейных напряжений: 012, 02з. 031. Эти сигналы инвертируются с помощью элементов НЕ 23-25, на выходах которых в соответствии с выражением (2) формируются логические сигналы S2t, $з2, $чз, единичное состояние которых соответствует отрицательной полуволне сетевых линейных напряжений 012, 02з. 0зч.

Логические сигналы ".2, $21, $23, $32, $з;, $ э являются выходными сигналами блока 14 синхронизации, Кроме того, они в утри блока 14 поступают нэ входы дифференцируюших цепей 26, выходы которых подключены к входам элемента ИЛИ 27. Выходным сигналом элемента ИЛИ 27 является последовательность импульсов Сщ, отстоящих один относительно другого на

60 эл.град. ь следу ощих с частотой 61,, где fc— частота сети, Каждый импульс последовательностии CQ) совпадает по времени с моментом перехода через нуль какого-либо линейного напряжения питающей сети.

8 целях обеспечения оптимального гармонического состава выходных напряжений и токсв ПЧНС необходимо синхронизировать управля ощ е си наль: с линейными напряжениями п гающей сети. В соответствии с выбранным алгоритмом работы логического блока си <хрсниэация производится по фронту сигнала 313 с помощью элемента И 28, RS-триггера 29 и линии 30 задержки.

Непосредственно после включения источника питания постоянного тска в момент о (фиг. 4) триггер 29 с помощью дифференцирующей RC-цечи 31. 32 (фиг. 3) устанавлиr ается s нулевое состояние и сигнал $Т на его выходе, имеющий нулевое значение, поступает на один из входов элемента И 28, блокируя подачу импульсов Сгч на тактовый вход делителя 12 частоты, В момент t> (фиг. - ) происходит переход сигнала $ э из нуле ого в единичное состояние, т.е. начинается первая положительная полуволна сетевого линейного напряжения 0 э с момента включения источника питания постоянного тока.

Так как триггеры кольцевого сдвигового регистра 39 в момент включения источника питания постоянного тока с помо цью RCцепи 46, 47 устанавливаются в состояние, соответствующее моменту t> (фиг. 4) в алгоритме работы устройства, то импульс Cso, соответствующий переходу в единичное со=тояние сигнала $чэ, необходимо исключить и начать подачу тактовых импульсов на кольцевой сдвиговый регисто с момента t3 !

ôèг. 4). Для этого выход элемента Н Е 25(фиг.

2) чодключен к S-входу триггера 29 ерез линию 30 задержки, рассчитанную на время задержки т ) ego, где trgp — длительность импульса последовательности Cv В результа.re триггер 29 переходит в единичное состояние в момент т2 (фиг. 5), сигнал ST принимает единичное значение и госледовательность импульсов Сбо подается на тактовый входделителя 12 частоты, начиная с импульса, соответствующего моменту тз (фиг, 4).

Выходной сигнал Сбо/и делителя частоты поступает на вход кольцевого сдвигов га регистра 39 (фиг. 1), формирующего модул.1рующие сигналы М1, Мг, Мз и их инверсии с частотой равной fc/è. Эти сигналы поступают на управляющие входы логического блока 48 (фиг. 1), для функционирования которого в соответствии с выбранным алгоритмом необходимо, чтобы момент перехода сигнала М1 из нулевого в единичное состояние совпадал с началом положительной полуволны линейного сетевогс напряжения UI3. С этой целью момент,о, фиг. 4) включения источника питания постоянного тока триггеры 40, 44 и 45 (фиг. 3) устанавливаются в единичное состояние, а триггеры

41-43 — в нулевое с помощью RS-цепочки

46, 47. Это состояние на выходах триггеров

40 — 45 сохраняется до момента t3 (фиг. 4)., когда на тактовые входы триггеров начинают поступать импульсы с выхода делителя

12 частоты. При этом каждым импульсом осуществляется кольцевой сдвиг состояний триггеров регистра, половина из которых в каждый момент времени находи ся в единичном, а другая половина в нулевом состоянии, Таким образом, с помощью кольцевого сдвигoool регистра формируется трехфазная система модулирующих сигналов Mz, MI, M3 и их инверсий. синхронизированная с линейными напряжениями питаю .: и сети.

Логический блок 48 (фиг. И с помощью модулирующих сигналов МI, Mz, МЗ и их инверсий M1, Mz, Мз, а также с помощью сигналов синхронизации S12, S21, Sz3, 532, 813, S31фосмирует сигнал Yz-Y7 управления регулирующими тиристорами 2--8 в соответствии с логическими выражениями:

Уг = М12 S12 "Лзг 5л+ М13 S13 М1г 812;

Ya=IVbi 521 М21 "-. ç Мз1 $э: Ь г Б р1:

У4=Мгз Я23 %зЗ13+М21 S21 Ь гз Яз:

Y5= Mz. 32 М31 ° с 11 I- MI2 S12 М32 Sz.; (3)

Чб= МЗI - О1 M21 % + M 32. S32 M31".>31;

Y7=M13 $13.М12 512- Мгз Ьз М13 &3, где М12, М21 Мгз, М32, М31, M13 — линейные модулирующие сигналы, формируемые в логическом устройстге в соответствии с вьIpaжениями:

М1г =(M1®М2) .M1:

М21 = (M19M2) Mzf

Мгз = (М2 9M3) Мг; (4)

M32 = (гЛ29 МЗ) МЗ:

М31 = (Мз ®М 1) . Мз;

M13 = (M3O+M,ð M1

Логический блок вырабатывает также сигналы Узз-Уза управления шунтирующими тиристорами 33-38 в соответствии с выражениями:

2Г

Узз = Уг M2 + У5 М1 " В "(М1 + Мг);

734 = Y3 )7z + У4 M1 + В "(MI + гЛ2);

У35 =- 1 4 M3 + У7 Q2 + В (Л2 + MÇ);

Узб= У5 цэ+ Уб Мг+ В (Mz+Q3); (5)

Y37 = Уб М1+ Чз 93+ В (93+ М1);

Уза У7 лл!+ У2 МЗ+ В (МЗ+91), где сигнал В соответствует интервалам, в которых ни на один регулирующий тиристор не подается сигнал управления и который определяется выражением

В = Yz ЧЗ У4 У5 -Y6 Y-.. (6)

Единичное состояние сигналов Уг- У7 и

УЗЗ вЂ” Уза, формируемых логическим устройством 48, соответствует наличию сигнала управления тиристором, номер которого соответствует цифровому индексу сигнала Y.

Сигналы управления У;-Ч7 и Y33 — Y35 через блок 49 выходных формирователей, обеспечивающих их усиление и гальваническую развязку, поступают на управляю,цие электроды соответствующих тиристоров.

Блок 49 выходных формирователей является известным устройством, представляюгцим собой совокупность двенадцати одноканальных усилителей-формирователей, Формирование сигналов управления тиристорами в соответствж с выражениями (3) и (5) обеспечивает такой алгоритм работы преобразователя, при котором нагрузка подключается на линейное напря>".ение питающей сети. полярность которого совпадает пс знаку с полярностью соответствующего линейного модулирующега сигнала, причем в пределах интервала, в котором они совпадают, запрещается включение нагрузки на линейное напряжение сети относительно первого на 60 эл.град в сторону

:;апазд иа" ия. Под линейными модулирующими сигналами понимаются логические сигналы формируемые в логическом устройстве 48 по выражениям (4) и соответствующие интервалам, в пределах которых фазные модулирующие сигналы С ÌI-М3 различаются по знаку один относительно другого. Полярность линейных модулирующих сигналов учитывается индексом в соответствии с выражениями:

AI;I - (Мк QMI ) MI;;

MIk = (Мк ЕМ ) MI, (7) где) =1,2,3; f=1,2,3, Таким образом, выделяются три парь1 линейных модулирующих сигналов с попарно противоположной индексацией, соответствующей направлению различия знаков фазных модулирующих сигналов.

Регулирующие тиристоры включаются попарно. обеспечивал подключение к сети

1б 17573 двух соединенных последовательно фаз нагрузки, Одновременно третья фаза нагрузки с помощью одного из шунтирую ци: тиристоров подключается параллельно той va двух фаз, которая в данный момент времени имеет полярность фазного модулирующего сигнала, совпадающую с полярностью фазного модулирующего сигнала подключаемой фазы. г1априме1.. при совпадении полярности сетевого линейного напряжения 012 "",. соответствующим линейным модулирующим сигналом М12 фазы 8 и 9 нагрузки (ф1ã. 1), соединенные последовательно, подключаются к этому линейному напряжению и в них протекает ток, направление которого э фазе 8 соответствует полярности сигнала

М1, а в фазе 9 — сигнала М2. Одновременно включают шунтирующий тиристор 38 и фаза

10 нагрузки подключается параллельно фазе 8, так как такое включение обеспечивает протекание тока в ней в направлении, соответствующем полярности сигнала Мз. Описанный алгоритм подключения параллельных фаз нагрузки реализуется двучленными слагаемыми в выражениях (5) для сигналов Узз-Уза управления шунтирующими тиристорами.

Для формирования непрерывного тока в нагрузке в интервалах, когда невозможно включение регулирующих тиристоров (Y2:=

=Уз = Y4 - Ys = Y6 = Ут = О), цепь нагрузки замыкают включением двух шунтирующих тиристоров, обеспечивающих протекание токов в тех же направлениях, в каком они протекали в интервале подключения нагрузки в сети. Для этого в указанных интеовалах

I времени включаются два шунтирующих тиристора. подключенных анодами. или два шунтирующих тиристора, подключенных катодами, к той фазе нагрузки, в которой протекает суммарный ток двух других фаз.

Выбор включаемой паоы тиристоров зависит от полярности сигнала модуляции этой фазы и соответствует слагаемому, содержащему сигнал В в выражениях (5).

Рассмотрим, например, формирование напряжений и TGKQB в трехфаэной активноиндуктивной нагрузке на интервале 1о-тз . (фиг. 5). В момент to линейное напряжение питающей сети 0з2 имеет положительное значение и его полярность совпадает с полярностью линейного модулирующего сигнала Мз2, Соединенные последовательно фазы 9 и 10 нагрузки подключены на напряжение 0з2 с помощью тиристоров 5 и 6, на которые поданы сигналы управления. Кроме того, включен шунтирующий тиристор

37, подключающий фазу 8 нагрузки паparлельно фазе 10 v обеспечивающий протекание тока в этой фазе в направлении, соответствующем полярности сигнала М1, Ток в нагрузке протекает псд действием напряженил 0э2 до момента t1 перехода его через

5 нуль и хотя на интервале to — t1 полярность сетевого линейного напряжения 02 также совпадает с полярностью соответствующего линейного модулирующего сигнала М12, Но поскольку 032 опережает по фазе U12, то

10 подключение нагрузки на напряжение 012 до момента 11 запрещается. В момент t1 напряжение 0э2 переходит через нулевое значение и фазы 8 и 9 нагрузки, соединенные последовательно, подключаются на на15 пряжение U12 включением регулирующего тиристара 2, при этом регулирующий Tv ðèсто,. Остае ся включенным.; ретья фаза 10 наг:,:„зкч подключается параллельно фазе 8 включением шунтирующего тиристора 38.

20 R момент t2 напряжение U12 питающей сети переходит через нулевое значение и в интервале t2-t2 не существует условий для включения регулирующих тиристоров. Поэтому разрешается включение шунтирующих

25 тиристсров 34 и 35, по которым замыкается це-:ь тока нагрузки, обеспечивая протекание его в том же направлении, в каком он протекал в каждой фазе нагрузки на интервале to — t2. Значение токов нагрузки на ин30 тервале t -тэ определяется энергией, =--песенной в активно-индуктианой нагрузке ча ин-ервале подключения ее к сети, а также ее параметрами.

В момент тз нагрузка вновь подключает35 ся к линейному напряжению 032 с помощью тиристо ров 5 и 6 и шунтирующего тиристора

37.; тири торы 34 и 35 запираются под действием сетевого напряжения, приложенногэ к ним в обратном направлении. В даль40 нейшем все процессы носят аналогичный циклический характер.

Таким образом, предложенное устройство позволяет улучшить энергетические показатели за счет улучшения гармониче45 ского состава токов и напряжений Hà Bblxo де ",påaáðàçoâàòåëÿ, получаемого путем устранения бестоковых пауз и увеличения пул ьснс...ти в трехфазной активно-индуктивной нагрузке, соединенной звездой беэ ну50 левого провода. Зто позволяет при использовании описанного преобразователя в составе регулируемого электропривода сушесгвенно снизить пульсации электромагнитного момента двигателя

55 Формула изобретения

Трехфазный преобразователь частоты с непосредственной связью, содержаигий тирис.срный кс.1мутатср с шестью регулируIc ;.;:и т,,эисторамк, ссединенными пг", р.- о встреч о-парэ -.ле,ь го между со1617573

12 бой и включаемыми в разрывы линейных проводов всех фаэ активно-индуктивной нагрузки, блок управления, выполненный формирующим цифровой код N, соответствующий отношению и частоты питающей сети к частоте основной гармонической составляющей на выходе преобразователя, выход которого соединен с управляющим входом делителя частоты с переменным коэффициентом деления, тактовый вход которого подключен к тактовому выходу блока синхронизации, тремя входами подключенного к питающей сети, о т л ич а ю шийся тем, что, с целью улучшения энергетических показателей за счет устранения бестоковых пауз и увеличения пульсности напряжения и токов в трехфаэной активно-индуктивной нагрузке, соединенной звездой беэ нулевого провода, в преобразователь введены шесть шунтирующих тиристоров, соединенных попарно встречно-параллельно между собой и подключаемых треугольником к линейным проводам трехфазной активно-индуктивной нагрузки, в блок синхронизации введены формирователи логических сигналов S12, $21 $23, $32, S31, $1з. единичное состояние которых соответствует положительной полуволне линейных напряжений 012, 021, 023, U32, 031. 013 питающей сети, формируемых по логическим выражениям

Slk-(1+ )

0а 1

0ис 2

I .1,2,3;

k 1,2,3; ! ФК кольцевой сдвиговый регистр с парафазными выходами: М1, М1, М2, М2, МЗ, Мз, вход которого соединен с выходом делителя частоты, логический блок, шесть управляющих

5 входов которого соединены с соответствующими выходами кольцевого сдвигового регистра, шесть синхрониэирующих входов— с шестью соответствующими выходами блока синхронизации, а двенадцать выходов

10 Ч2-Ч7, У33-У36 через блок усилителей-формирователей подключены к соответствующим управляющим электродам регулирующих и шунтирующих тиристоров, причем аппаратурная реализация указанно15 го логического блока и связи между его входами и выходами определяются следующими выражениями:

Y2 = M12 $12 МЗ2 $32 1 М13 S13 912 $12;

Y3 = М21 $21 М23 323+ М31 S31 М21 731, 20 Уз = Мгз $33 M13 S13+ М31 $31 Мгз S33,;

Ys - Ì3z S3z Мзг $31 1- М1г Szz Мзг $зг, У6 М31 $31 М21 S21+ М32 $32 М31 S31;

У7 М13 $13 М13 Slz+Мгз S23 М13 Б13, где

М12 - (М1®М2 ) M1;

M21- (M1®Ì2) М2:

М23=(М29М3) М2;

M32 = (М2 9 МЗ ) Мз;

M31 = (МЗ 6) М1 ) МЗ, М13 = (М34)М1) М1;

Y33 = У2 М2+ У5 M1+ В (M1+ M7 );

У34 = YÇ М2+ У4 М1+ В (М1+ М2);

У35= У4 МЗ+ Ут М2+ В (М2+ M3);

Y36 = У5 Мз + У6 М2 + В (М2 + Мз );

35 Узч У6 М1+ Уз Мз+ В (M3+ M1);

Y36=Y1 M1+У2 МЗ+ В (МЗ+ М1), где В = У2 .Уз У4 У5 У6 Ут.

1617573

813

8Т

С60

ceo/ж

iMZ

М1 а айаг з

1617573

10 о

PLlZ.5

УГ

Уб

ЮФ

Ю

УЛ7

УЯ

011 ЮХ 021 О1 И72 NZ

Составитель Г, Мь:арык

Редактор М, Келемеш Техред М.Моргент;-л Корректор Л. Пилипенко

Заказ 4126 Тираж 496 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Рауиская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101