Устройство автоматической регулировки усиления

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение устойчивости работы при дискретном управлении с одновременным увеличением быстродействия. Устройство автоматической регулировки усиления содержит многокаскадный усилитель 1, амплитудный детектор 2, компаратор 3 с постоянным пороговым уровнем, элемент 4 сравнения кодов, эллемент ИЛИ 5, управляемый генератор 6 тактовых импульсов, счетчик 7, блок 8 определения числа включаемых каскадов, блок 10 аналогово-цифрового преобразования огибающей, коммутаторы 11, ключи 12. Для повышения устойчивости работы введены управляемый параллельный регистр 9, элемент 13 дифференцирования и одновибратор 14. Управляемый параллельный регистр 9 содержит N D-V-триггеров, N первых элементов ИЛИ, N элементов И, N-1 вторых элементов ИЛИ, конденсатор и резистор. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з Н 03 С 3/20

i

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4471846/24-09 (22) 01,08.88 (46) 30.12,90, Бюл. N 48 (72) С.К.Горев, B,È.Êè÷àòoB, П.M.Êîìîðíèков, А,M.Ëèõà÷åâ и С.И.Юшников (53) 621.396.662 (088.8) (56) Авторское свидетельство СССР

М 1282310, кл. Н 03 G 3/20, 1985,.

Авторское свидетельство СССР

N. 1374403, кл. Н 03 G 3/20, 1986. (54) УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ (57) Изобретение относится к радиотехнике.

Цель изобретения — повышение устойчивости работы при дискретном управлении с одновременным увеличением быстродейст-, вия, Устройство автоматической регулиров„„5Ц „„1617622 А1 ки усиления содержит многокаскадный усилитель 1, амплитудный детектор 2, компаратор 3 с постоянным пороговым уровнем, элемент 4 сравнения кодов, элемент ИЛИ 5, управляемый генератор б тактовых импульсов, счетчик 7, блок 8 определения числа включаемых каскадов, блок 10 аналоговоцифрового преобразования огибающей, коммутаторы 11 и ключи 12. Для повышения устойчивости работы введены управляемый параллельный регистр 9, элемент 13 дифференцирования и одновибратор 14.

Управляемый параллельный регистр 9 содержит N 0V-триггеров, N первых элементов ИЛИ, Nэлементов И,,N-1 вторых элементов ИЛИ, конденсатор и резистор.

2 ил.

1617622

Изобретение о носится к радиотехнике и может быть использовано в аппаратуре проводной, тропосферной и радиорелейной связи.

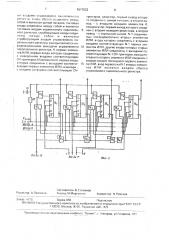

Цель изобретения — повышение устой- 5 чивости работы, На фиг.1 представлена структурная электрическая схема устройства автоматической регулировки усиления; на фиг.2—, структурная электрическая схема управляе- 10 мого параллельного регистра.

Устройство автоматической регулировки усиления (фиг.1) содержит многокаскадный усилитель 1, амплитудный детектор 2, компаратор 3 с постоянным пороговым 15 уровнем, элемент 4 сравнения кодов (ЭСК), элемент ИЛИ 5, управляемый генератор 6 тактовых импульсов (ГТИ), счетчик 7, блок 8 определения числа включаемых каскадов, управляемый параллельный регистр 9, блок 20

10 аналого-цифрового преобразования (АЦП) огибающей, коммутат.оры 11, ключи

12, элемент 13 дифференцирования и одновибратор 14, Управляемый параллельный регистр 9 25 (фиг.2) содержит N DV-триггеров 15, ..., 15к, N первых элементов ИЛИ 161, ..., 16м, N элементов И 17>, ..., 17 ц, N-1 вторых элементов ИЛИ 181, ..., 18 -1, конденсатор 19 и резистор 20. 30

Устройство работает следующим образом, Элементы 9, 13 и 14 предназначены для включения строго заданного числа каскадов в многокаскадном усилителе и исключения 35 перегрузки каскадов при переборе различных вариантов их включения.

Блок 10 АЦП формирует требуемое число активных каскадов в двоичном коде, обеспечивающее усиления входного сигна- 40 ла до заданного уровня и поступающее на первый вход ЭСК 4.

При включении устройства счетчик 7 может находиться в одном из 2 состояний, при этом на его выходах формируется ком- 45 бинация единиц и нулей, После суммирования единиц блоком 8 и определения числа включаемых каскадов число единиц в двоичном коде поступает на второй вход ЭСК 4.

Если коды на входах ЭСК 4 совпадают, то 50 сигналы рассогласования на его выходах отсутствуют при одновременном формировании "1" на входе ЭСК "Равно", которая поступает на стробирующий вход управления параллельного регистра и разрешает 55 прохождение "1" с выходов счетчика 7 на входы управления коммутаторов 11 и ключей 12 каскадов многокаскадного усилителя

1, Если по сигналу "1" ключ 12 включает цепь питания каскада, а коммутатор 11 соединяет вход усилительного каскада с выходом предыдущего, то в это «в тракт усиления включается исло каскадов, равное J, сформированному на выходе блока 10

АЦП (1 j N-К, где N — число коммутирующих усилительных каскадов, К вЂ” число резервных каскадов), С учетом изменения коэффициента усиления тракта по цепи плавной регулировки последнего каскада на выходе устройства появляется сигнал данного уровня. При этом напряжение на выходе амплитудного детектора 2 превышает напряжение U«p на первом входе компаратора 3 с постоянным пороговым уровнем, что приводит к формированию на его выходе сигнала "0". При наличии на всех входах элемента ИЛИ 5 "0" запуска ГТИ б не происходит и счетчик 7 не меняет своего состояния, Таким образом, в тракт усиления включается заданное число усилительных каскадов.

Если же при включении устройства число единиц на выходе счетчика больше или меньше заданного числа каскадов, сформированного блоком 10 АЦП, то на одном из выходов рассогласования ЭСК 4 появляется сигнал "1", который через элемент ИЛИ 5 запускает ГТИ 6, очередной импульс которого изменяет состояние счетчика 7 до тех пор, пока на входах ЭСК 4 коды с выхода блока

10 АЦП не совпадут. При совпадении кодов

"1" с выхода "Равно" ЭСК 4 поступает на стробирующий вход управляемого параллельного регистра и разрешает прохождение "1" с выходов счетчика 7 на входы управления коммутаторов 11 и ключей 12 каскадов многокаскадного усилителя 1. Таким образом, в тракт усиления включается количество каскадов, выработанное блоком

10 АЦП. При этом при изменении величины входного сигнала в усилительном тракте остается включенным то количество каскадов, которое соответствует предыдущей комбинации на выходе управляемого параллельного регистра, т.е. в случае появления сигнала рассогласования на одном из выходов "Больше" и "Меньше" ЭСК 4 сигнал "0" подается на стробирующий вход управляемого параллельного регистра 9 и удер>кивает его в предыдущем состоянии до тех пор, пока на входе счетчика 7 не сформируется одна из разрешенных кодовых комбинаций включения каскадов. "1" с выхода "Меньше"

ЭСК4одновременнос запуском ГТИ бчерез элемент ИЛИ 5 подается на вход элемента

13 дифференцирования, формируются импульсы необходимой амплитуды и длительности для срабатывания одновибратора 14. выход которого соединен с входом сброса управляемого параллельного регистра, и от"617622 ключается необхо имое чи д число усилитель- гер 15z, остальные триггеры остан тся в исных каска ов ля и д в для исключения перегрузки ходном состоянии. При необходимости отут явисусилителей по входам. ключения двух усилительных каскадов

Если в процессе работы отказывает задача решается выбором длительности имодин из усилителей тракта, то напряжение 5 пульса на выходе блока 14. на выходе амплитудного детектора 2 меньше опорного напряжения на пе в ер ом входе Устройство автоматической регулировкомпаратора и "1" с его выхода через эле- ки усиления, содержащее соединенные по, под воздейст- следовательно многокаскадный усилитель, вием которого счетчик 7 изменя яет свое 10 вход и выход которого являются соответстсостояние до включения з аданного числа венно входом и выходом. устройства, амплиисправных каскадов. тудный детектор, выход которого соединен

Управляемый параллельный регистр 9 с входом регулировки усиления последнего ду щ б разом, каскада многокаскадного усилителя, компаПри подаче питающего напряжения на 15 ратор с постоянным пороговым уровнем, R-входы DV-триггеров подается сигнал "1", элемент ИЛИ, управляемый генератор так— р р "О" (при этом товых импульсов и счетчик, к информационс выхода блока 14 поступает сигнал "1"). В ным выходам которого подключен блок результате Вср. элементы памяти устанавли- определения числа чи ла включаемых каскадов, ваются в нулевое состояние. По мере заряда 20 элемент сравнения кодов, первый цифровой конденсатора 19 на S-вхо ах ф м д фор ируется вход которого соединен с цифровым выхосигнал "1" и тригге ы готовы к и р у равлению дом блока определения числа включаемых по О-входам, Если с выхода "Равно" ЭСК 4 каскадов, блок аналого-цифрового преобрапоступает сигнал "1", то на V-вхо — ходах эле-. зования огибающей, вход и выход которого ментов памяти — "1" и и у равляемый парал- 25 соединены соответс венно с входом устройлельный регистр трансли ет и ру т сигнал с ства и вторым цифровым входом элемента выходов счетчика 7 на и авля у р ющие входы сравнения кодов, выходы рассогласования многокаскадного усилителя 1, I

"Больше" и Меньше" элемента сравнения

При появлении на выхо е ЭС д СК 4 сигна- кодов соединены с другими входами элелов рассогласования с его выхода "Равно" 30 мента ИЛИ,, на входе каждого из каскадов на Ч-входы пост пает "О" и т игг ь

V- у " " р ер i сохра- многокаскадного усилителя, кроме последняют свое состояние о тех по, п д ор, пока на него, включен коммутатор, второй выход ковыходах счетчика 7 не об аз ет р у ся требуе- торого соединен с выходом того же каскада, мая разрешенная комбинация. Для защиты в цепи питания всех каскадов, кроме помногокаскадного усилителя от перегрузок 35 следнего, включены ключи, входы управлепо сигналу "О" с выхода одновибратора 14 ния которых соединены с входами осуществляется сброс требуемого;исла управления соответствующих коммутатоединиц на выходе элементов памяти с по- ров, о тл и а т л и ч а ю щ е е с я тем, что, с целью н я устойчивости ра оты, в него мощью элементов ИЛИ 16i, ..., 16л и 181... повышения устойчи о б

18и-1. Пусть для определенности необходи- 40 введены управляемый параллельный ремо уменьшить число е ини н 1 д ц на 1 и на выхо- гистр, информационные входы которого соде параллельного регистра сформирована единены с выходами счетчика, а комбинация 01|...0. Тог а необхолимо да необх .. o информационные выходы — с соответствуюсбросить 2-й т игге в н л в р р у е ое состояние. щими входами управления ключей и комм—

По сигналу на выходе "Меньше" ЭСК 4 на 45 таторов, тактовый вход и стробирующий выходе одновибратора 14 появится сигнал вход управляемого параллельного егист а де элемента ИЛИ 161 останется соединены соответственно с выходом уп-, сигнал "1" с инверсного выхода триггера 151 равляемого генератора тактовых импульсов и он останется в и ежнем т р сос оянии, на и выходом совпадения элемента сравнения выходе элемента ИЛИ 181 появится "0", на 50 кодов, и соединенные последовательно элеинверсном выходе триггера 15z "О", следо- мент дифференцирования и одновибратор, вательно, на выходе элемента ИЛИ 16 "0", е та ИЛИ 162 "О, выход которого соединен с входом сброса который через элемент И 17z поступит на. управляемого параллельного регистра, вход

S-вход триггера 152 и сбросит его в нулевое элемента дифференцирования соединен с состояние. 55 выходом рассогласования "Больше" элеТак как длительность импульса на выхо- мента сравчния ко я кодов, при этом управляеде одновибратора 14 равна времени пере- мый параллел нь л льный регистр выполнен в виде ходных процессов в триггерах 151, ..., 15и, N-разряднОго параллельного регистра и со -т иггеров, инц ормационные на выходе элемента ИЛИ 18z сигнал "0" не держит N DV-триггеров, инф появится и сброшен будет только один триг- входы которых являются информационны1617622

Р гк

Р.

0m блт и

Фиг. г

Составитель В.Степанов

Гехред Ч.Моргентал Корректор Н.Ревская

Редактор А.Лежнина

Заказ -I 8 Гираж 658 Подписное

ВНИИПИ Гос,-дарственного комитета по изобретениям и открытиям при ГКНТ СССР

1130;!5, москва, Ж-35, Раушская наб., 4/5

Произв дственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 101 ми входами управляемого параллелы ого регист.;а, зходы сброса cc:.динены межд собой и являются шиной питания, тактовые входы соединены между собой и являются тактовым входом управляемого параллель- 5 ного регистра, стробирующие входы соединены между собой и являются стробирующим входом управляемого àраллельного регистра, выходы являются информационными выходами управляемого 10 параллельного регистра, N первых элементов,ИЛИ, первые входы которых соединены с инверсными входами соответствующих

О\/-триггеров, N элементов И, первые входы которых соединены с выходами соответст- 15 вующих первых элементов ИЛИ, а выходы— с входами установки соответствующих DVтриггеров, резистор, первый вывод которого соединен с шиной питания, à BTGpGA Bblвод — с вторыми входами элементов И, конденсатор, первый вы вод которого соединен с вторым выводом резистора, а второй вывод — с корпусной шиной, N-1 соединенных последовательно вторых элементов

ИЛИ, входы которых соединены с вторыми входами соответствующих N-1 первых элементов ИЛИ, другие входы которых вторых элементов ИЛИ соединены с выходами соответствующих N-1 0V-триггеров, выход последнего второго элемента ИЛИ соединен с вторым входом последнего первого элемента ИЛИ, вход первого из N-1 вторых элементов ИЛИ является входом сброса управляемого параллельного регистра,