Преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством и является усовершенствованием изобретения по авт.св. N 1146803. С целью повышения быстродействия в процессе выхода на режим в преобразователь по авт.св. N 1146803, содержащий генератор 1, делитель 2 частоты, блок 3 формирования синусоидального тока, блок 4 формирования косинусоидального тока, дешифратор 5, ключи 6 и 7, формирователь 8 фазовых импульсов, элементы И-НЕ 9 и 10, блок 11 сравнения амплитуд, формирователь 12 синусоидальных напряжений, усилитель 13, фазовращатель 14, формирователь 15 импульсов, блок 16 управления, арифметический блок 17, введены индикатор 18 режима и элементы коррекции 19 - 22, шунтирующие резисторы интеграторов в цепях стабилизации амплитуды и фазы синусоидального и косинусоидального токов блоков 3, 4 на время переходных процессов. 1 з.п. ф-лы, 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИА ЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЬЙ HOMHTET

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (61) 1146803 (21) 4491931/24-24 (22) 10.10.88 (46) 30,12.90. Бюл. № 48 (72) И. Я. Прокофьева, О. А. Беляков, В. А. Догадаев и Л. Г. Матвеев (53) 681.325(088.8) (56) Авторское свидетельство СССР № 1146803, кл. H 03 М 1/64, 1983. (54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством и является усовершенствованием изобретения по авт. св. № 1 146803, С целью повышения быстро„„SU„„1617640 А 2 (51)5 Н 03 М 1/64

2 действия в процессе выхода на режим в преобразователь по авт. св. № 1146803, содержащий генератор 1, делитель 2 частоты, блок 3 формирования синусондального тока, блок 4 формирования косинусоидального тока, дешифратор 5, ключи 6 и 7, формирователь 8 фазовых импульсов, элементы

И вЂ” НЕ 9 и 10, блок 11 сравнения амплитуд, формирователь 12 синусоидальных напряжений, усилитель 13, фазоврашатель 14, формирователь 15 импульсов, блок 16 управления, арифметический блок 17, введены индикатор 18 режима и элементы коррекции

19 — 22, шунтирующие резисторы интеграторов в цепях стабилизации амплитуды и фазы синусоидального и косинусоидального токов блоков 3 и 4 на время переходных процессов. 1 з.п. ф-лы, 6 нл:

Ф е г — 1

1617640

3 4

Изобретение относитгя к В1ггомати; и

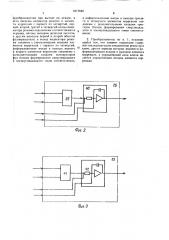

Вычислит(ль»OII технике H мо;кет,быть Нспользова1! О для сВязи al!HJIO "ОВых источННКоН информации с цифровым вычислительным устройством. !.!eJII lo изобретения является повышение быстродейстьия преобразователя при выходе на режим, На фнг. 1 привеп.!!а структурная схема преобразователя; на фиг. 2 — структурая схема компаратора ф ;:,; иа фиг. 3 — 10 труктурная схема триггера; Ila фиг. 4

1 структурная схема индикатора режима; па фиг. 5 — диаграмма работы преобразователя; на фиг. 6 — диаграмма работы ин дикатора режима.

Преобразователь угла поворота вала в, код (фиг. 1) содержит генератор 1, дели, тель 2 1астот1:1, блок 3 формирования синуcoHJI.альнОго тока, блок 4 формирования KocHHócoèäàëbIIoã0 тока, дешифратор 5, KJIIO чи 6 и 7, формирователь 8 фазовых нмпуль- 20 . сов, элементы И вЂ” HE 9 и 0, блок 11 сравнения амплитуд, формирователь 12 синусоидальных напряжений, усилитель !3, фазовращатель 14, формирователь !5 импульсов, ,блок 16 управления, арифметический блок 17, :индикатор !8 режима и элементы 19 — 22 коррекции.

Каждый из блоков 19 — 22 коррекции . Выполнен на кл(оче 23 и резисторе 24.

Блок 3 формирования синусоидального и блок 4 форм Яров(1ния кос ивусоидального 30 токов содержат соответственно компараfoры 25 и 26 фаз, элементы 27 и 28 задержки, .датчики 29 и 30 токов, ключи 31 и 32, триггеры 33 и 34, р(гулиру(ощие элементы

35 и 36.

БЛОХ 16 управления Вкл!счает синхро- 35 низатор 7 з блок 38 кл ;-.чей.

Ком(II;;paTоp фаз (фиг. 2) Выполнен На

Tp H I ã(Hc 3 9 и и(иге г ра го:;, е

Тр((гге;, (фиг. ) состоит .(з триггера 41 и н н тегра тора 42.

, HäHHaTop 18 режима (фиг. 4) содержит (з фор мир ОнатcJIH 43 11 мг((льсов ре НсТр 4 4, ко;":1 аратор 4О, триггер 46:.1 интегратор 47. .:."1еобра,Овател1 р- cëaäóIOH. „ Iì образом.

Генератор i вырабатыaacT стабильное по частоте j импульсное 1:апрян(ение, которое делитель 2 час-оты делит в 2" раз, где и —число его разрядов, вырабатывая и импульсных сигналов типа меандр, образующих кодовую маску, две последовательности опорнь!х сигналов (аст(этой 11= — — - j/2, сдВинутые одна относительно другой Hа л/2 (фиг. 5, а, б), и две последовательности управляющих импульсОВ той H(e частотой (фиг. 5, в, г), сдвинутые одна относительно другой на "f/2.

С выхода делителя 2 часто..ы управляющие ш.пул» CII и опорные меандры поступают .!Ia 55 входы блоков 3 и 4 формирсвания синуссипального н косниусоидального токов, котолые .

Вме те Г блоком 1 сравнен!1Я амг(литуд

I обеспечивают точную угтановку и стабилизацию равенства амплитуд токов, питающих фазовращатель 14: При этом напряжения с датчиков 29 и 30 токов (фиг. 5, д, е), пропорциональные амплитудам токов первой и второй обмоток фазовращателя 14, поступают на входы ключей 31 и 32, которые управляются импульсами (фиг. 5, в, г) с выходов делителя 2 частоты. Г1од действием этих импульсов ключи 31 и 32 пропускают на блок!! сравнения амплитуд сигналы в виде отрицательных импульсов (фиг. 5, ж, з) в момент достижения синусоидальными напряжениями датчиков 29 и 30 токов своих отрицательных амплитудных значений. Блок 11 сравнения амплитуд сравнивает амплитуды отрицательных импульсов с опорным постоянным напряжением и выдает информационные сигналы, которые поступают на информационные входы триггеров 33 и 34, на С-входы которых поступают соответствующие синхроимпульсы (фиг. 5, в, г). Триггеры 4! в составе триггеров 33 и 34, работающие в режиме переключения, формируют иа выходе сигналы, которые поступают. ьа вход интегратора 42. На выходе интегратора 42 образуются медленно изменяющиеся напряжения (фиг. 5, и, к), которые йоступают на входы регулирующих элементов 35 и 36, на другие входы которых приходят задержанные опорные сигналы, поступающие е выходов элементов 27 и 28 задержки. Блоки 3 и 4 формирования синусоидального и косииусоидального токов вместе с дешифратором 5, ключами 6 и 7„ формирователем 8 фазовых импульсов и элементами И вЂ” НЕ 9 и 10 производят привязку нулей фаз питающих токов к опорным сигналам делителя 2 частоты. При этом с датчиков 29 и 30 токов синусоидальные Ha!;I a I (Вил (фиг. 5, д, 8), совпадающие по фазе с токами первой и второй обмоток фазовращателя !4, поступают через ключи

6 и .7 на вход формирователя 8 фазовых импульсов (фиг. 5, н). Ключи 6 и 7 пропускают синусоидальные напряжения в момент действия на их входах управляющих импульсов (фиг. 5 л, м), поступаюш,их с дешифратора 5. Формирователь 8 фазовых импульсов формирует импульсы (фиг. 5, а)

В момент перехода этих напряжений через .1уль от Отрицательного значения к положител; но;;:у Сформированные импульсы синусоидального и косинусоидального напряжений с Выхода формирователя 8 фазовых импульсов через элементы И вЂ” HE 9 «!0 поступают на С-Входы триггеров 39 компараторов 25 и 26, а на 0-входы этих триггеров приходят опорные меандры с первого и третьего выходов делителя 2 частоты соответственно. Триггеры 39, работающие в режиме переключения, формируют на выходе

° импульсн(е напряжения частотой 40- — 60 Гц, которые поступают на входы интеграторов

40 компараторов 25 и 26 фаз. На выходах

1617640 интеграторов 40 образуются медленно меняющиеся напряжения (фиг. 5, и, р), по- ступающие на управляющие входы элементов

27 и 28 задержки, где осуществляется задержка опорных меандров во времени и, следовательно, точная установка 90-градусного сдвига фаз токов. Задержанные меандры с выходов элементов 27 и 28 задержки поступают на вход регулирующих элементов

35 и 36, с выходов которых меандры, модулированные по амплитуде и сдвинутые во времени относительно опорных меандров, поступают на входы формирователя

12 амплитудных напряжений и далее через усилитель 13 на первую и вторую обмотки фазовращателя 14. Напряжение выходной обмотки фазовращателя 14 поступает на вход формирователя 15 импульсов, вырабатывающего фазовые импульсы, временное положение которых относительно начала преобразования, определяемого опорным меандром, пропорционально углу поворота ротора фазовращателя 14. Фазовые импульсы с выхода формирователя 15 импульсов поступают на последовательно соеди ненные блок 16 . управления и арифметический блок 17, которые производят синхронизацию фазовых 25 импульсов, считывание, запись и хранение текущего кода делителя 2 частоты, эквивалентного углу поворота фазовращателя

14. Интеграторы в цепях стабилизации амплитуды и фазы синусоидального и косинусоидального токов определяют переходный 30 процесс преобразователя при включении питания. Уменьшение постоянной времени интегрирующих цепей, с одной стороны, вызывает уменьшение времени переходного процесса или выхода на режим, а с другой— увеличение размаха колебаний фазы и ам- 36 плитуды синусоидального и косинусоидального токов вокруг среднего установившегося значения. Поэтому выбирают постоянную времени интегрирующих цепей достаточно большой. Для уменьшения времени выхода на режим индикатор 18 режима подключает через ключи 23 шунтирующие резисторы 24 параллельно резисторам интеграторов 40 и 42. Время окончания переходного процесса определяется индикатором

18 режима по достижении равенства амплитуд и 90-градусного сдвига синусоидального и косинусоидального токов следующим образом.

Опорные меандры частотой fi с первого выхода делителя 2 частоты (фиг. 6, а) поступают на формирователь 43 импульсов ин- 50 дикатора 18 режима, который формирует по отрицательному фронту строб. Длительность строба выбирается с учетом требо-. ваний по точности поддержания равенства амплитуд и 90-градусного сдвига синусоидального и косинусоидальиого токов. Регистр

44 (сдвига), на V-вход которого поступают стробы, а на С-вход — меандры частотой

Afi (где К=16, 32, 64, ...,) с пятого выхода делителя 2 частоты, сдвигает стробы на (l/8— 1)К)Тi (фиг. 6, б), где T = l! f — период опорных меандров.

Одновременно синусоидальные напряжения с датчиков 29 и 30 токов (фиг. 6, в, г) поступают на компаратор 45 индикатора 18, который сравнивает входные напряжения и формирует фронты импульсного сигнала в момент равенства амплитуд (фнг. 6, д) . На выходе триггера 46 индикатора 18 формируется уровень нуля при несовпадении во времени положительного фронта импульсного сигнала на выходе компаратора 45 со стробом на выходе регистра 44 (сдвига) и единичный уровень при совпадении положительного фронта выходного сигнала компаратора 45 со стробом. Чтобы повысить помехоустойчивость работы индикатора 18., выходной сигнал триггера 46 проходит через интегратор 47 с небольшой постоянной времени. Таким образом, во время переходно-о процесса, когда положительный фронт импульсного сигнала на выходе компаратора

45 не совпадает со стробом, формируется на выходе индикатора 18 нулевой сигнал, который поступает на управляющие входы ключей 23 элементов 19 — 22. Под действием управляющего сигнала ключи 23 подключают резисторы 24 параллельно резисторам интеграторов 40 и 42 компараторов 25 и 26 и триггеров 33 и 34, тем самым уменьшая ",х постоянную времени и время выхода на режим.

По окончании переходного процесса фронт положительного импульсного сигнала на выходе компаратора 45 попад" åò во времени внутрь строба, сформированного на выходе регистра 44 (сдвига), что вызывает формирование на выходе индикатора 18 положительного уровня, который определяет размыкание ключей 23 элементов 19 — 22, т. е. отключение резисторов 24. В результате происходит увеличение постоянной времени интегрирования интеграторов 40 и 42 блоков формирования синусоидального и косинусоидального токов в установившемся режиме.

Таким образом, шунтирование резисторов интеграторов в цепях стабилизации амплитуды и фазы синусоидального и косинусон= дального токов на время переходного процесса позволяет значительно уменьшить время выхода преобразователя на режим. При этом величина постояннои времени интеграторов в установившемся режиме может быть увеличена до значения, необходимого для обеспечения точности и дискретности, ограничиваемой лишь уровнем шумов преобразователя.

Формула изобретения

1. Преобразователь угла поворота вала в код по авт. св. № 1146803, отличающийся тем, что, с целью повышения быстродействия

16

Йреобразователя при выходе на режим, в него введены индикатор режима и элементы коррекции с первого по четвертый, первый, второй, третий и четвертый входы инди-. катора режима подключены соответственно к первому, пятому выходам делителя частоты, к другим выводам первой и второй обмоток фазовращателя, а выход индикатора режима соединен с управляк)щими входами элеентов коррекции с первого по четвертый, Ииформвпиовиые входы II выходы первого второго элементов коррекции соединены с ополнительными входами компараторов аз блоков формирования синусоидального и косинусоидального токов соответственно, 17640 а информационные входы и выходы третьего н четвертого элементов коррекции сое.динены с дополнительными входами триггеров блоков формирования синусоидального и косинусоидального токов соответственно.

2. Преобразователь по п. 1, отличающийся тем, что элемент коррекции содержит последовательно соединенные резистор и ключ, другие выводы которых являются информационными входом и выходом элемента коррекции, а управляющий вход ключа является управляющим входом элемента коррекции.!

617б40

1617640

Составитель А. Смирнов

Редактор A Лежннна Техред А. Кравчук Корректор Л. Пилипенко

Заки 4! 21 Тираж 668 Подписное

f3flHlll tll r с, сар тнепного комитета по изобретениям н открытиям при ГКНТ СССР ! l:lO ° 3 ъ, .Мîi ква, Ж--35, Рауновская наб., д. 4/5

Пр >:зволсгв нп нхзательскпй комбинат «Патент», г. Ужгород, ул. Гагарина, lOl