Цифровой частотный модулятор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - расширение области изменения средней частоты выходного сигнала. Цифровой частотный модулятор содержит опорный генератор 1, накапливающий сумматор 2, буферный регистр 3, реверсивный счетчик 4, двоичный сумматор 5, блок 6 постоянной памяти, цифроаналоговый преобразователь 7, фильтр 8 нижних частот. Опорный генератор 1 и накапливающим сумматор 2 с буферным регистром 3 формируют код фазы средней частоты. Опорный генератор 1 и реверсивный счетчик 4 формируют код фазы сдвига средней частоты, т.е. величины девиации. В цифроаналоговом преобразователе 7 происходит набег фазы, который определяет сдвиг средней частоты. Этот набег фазы учитывается, вследствие чего информация передается без искажений и с высокой стабильностью частоты. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (I! ) (я)5 Н 04 1 27/12

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4635860/24-09 (22) 12.01.89 (46) 30.12.90. Бюл, М 48 (71) Ярославский государственный университет (72) Е.Н.Новиков (53) 621.394.61(088,8) (56) Авторское свидетельство СССР

М 1336265, кл, Н 04 1 27/12, 1986. (54) ЦИФРОВОЙ ЧАСТОТНЫЙ МОДУЛЯТОР (57) Изобретение относится к радиотехнике.

Цель изобретения — расширение области изменения средней частоты выходного сигнала. Цифровой частотный модулятор содержит опорный генератор 1, (накапливающий сумматор 2, буферный регистр 3, реверсивный счетчик 4, двоичный сумматор 5, блок 6 постоянной памяти, цифроаналоговый преобразователь 7, фильтр 8 нижних частот. Опорный генератор 1 и накапливающий сумматор 2 с буферным регистром 3 формируют код фазы средней частоты. Опорный генератор 1 и реверсивный счетчик 4 формируют код фазы сдвига средней частоты, т.е. величины девиации. В цифроаналоговом преобразователе 7 происходит набег фазы, который определяет сдвиг средней частоты. Этот набег фазы учитывается, вследствие чего информация передается без искажений и с высокой стабильностью частоты, 1 ил.

1617652

Изобретение относится к радиотехнике и может быть использовано в генераторах частотно-модулированных колебаний, применяемых в радиосвязи, радиолокации.

Цель изобретения — расширение области изменения средней частоты выходного сигнала.

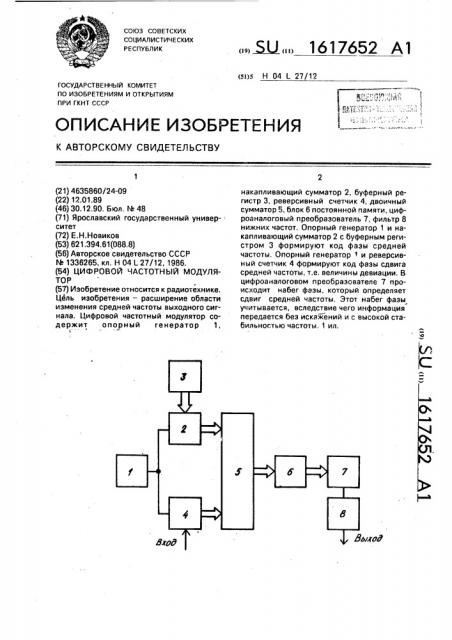

На чертеже представлена структурная электрическая схема предлагаемого модулятора, Цифровой частотный модулятор содержит опорный генератор 1, накапливающий сумматор 2, буферный регистр 3, реверсивный счетчик 4,.двоичный сумматор 5, блок 6 постоянной памяти, цифроаналоговый преобразователь 7 и фильтр 8 нижних частот.

Цифровой частотный модулятор работает следующим образом.

Опорный генератор 1 и накапливающий сумматор 2 с буферным регистром 3 служат для формирования кода фазы средней частоты, а опорный генератор 1 и реверсивный счетчик 4 — для формирования кода фазы сдвига средней частоты, т.е. величины девиации. В двоичном сумматоре 5 из упомянутых кодов формируются коды фаз характеристических частот, отличающихся от средней частоты на величину девиации.

Блок 6 постоянной памяти выполняет функции кодового функционального преобразователя, где каждой кодовой комбинации текущей фазы ставится в соответствие код, несущий информацию о мгновенном значении сигнала в данный момент времени, Цифроаналоговый преобразователь (ЦАП) 7 и фильтр 8 нижних частот (ФНЧ) преобразуют цифровой код в синусоидальный сигнал на выходе цифрового частотного модулятора.

Рассмотрим в отдельности процессы формирования сигналов средней частоты, сигналов сдвига частоты и характеристических частот.

Выходы разрядов реверсивного счетчика 4 отсоединены от соответствующих входов двоичного сумматора 5, Сигналы с выхода опорного генератора 1 поступают на синхронизирующий вхоц накапливающего сумматора 2, С каждым импульсом код на выходе накапливающего сумматора 2 увеличивается на величину кода, хранящегося в буферном регистре 3, причем если код в регистре 3 равен единице, то функционирование Накапливающего сумматора 2 не отличается от функционирования двоичного сумматора 5, Если код, хранящийся в буферном регистре 3, отличен от единицы, то значение кодов с выхода накапливающего сумматора 2 нарастает линейно, но с болв5

55 шей скоростью, а так как разрядность накапливающего сумматора 2 ограничена, то сброс его произойдет быстрее, т.е, средняя частота выходных колебаний будет выше, чем в случае работы накапливающего сумматора 2 в режиме двоичного сумматора 5.

В результате заполнения накапливающего сумматора 2 на выходе двоичного сумматора 5 вырабатывается двоичный код числа, соответствующего текущей фазе выходного сигнала средней частоты. Так как значение кода с выходов накапливающего сумматора

2 нарастает по линейному закону, угол наклона которого зависит от кода буфера регистра 3, по мере поступления на вход накапливающего сумматора 2 тактовых импульсов с выхода опорного генератора 1, то сигнал с выхода ЦАП 7 в этом случае можно представить треугольной аппроксимацией.

Выходы разрядов накапливающего сумматора 2 отсоединены от соответствующих входов двоичного сумматора 5, а выходы реверсивного счетчика 4 подсоединены к соответствующим входам двоичного сумматора 5, Управление направлением счета реверсивного счетчика 4 осуществляется поступающим на вход "Направление счета" сигналами информации. При поступлении логической единицы осуществляется прямой счет, а при поступлении логического нуля — обратный счет. Так как при прямом счете значение кода с разрядов реверсивного счетчика 4 нарастает, а при обратном убывает по линейному закону по мере поступления на вход реверсивного счетчика 4 тактовых импульсов с выхода опорного генератора 1, сигналы с выхода ЦАП 7 можно представить треугольной аппроксимацией в промежутке времени tl — tm при поступлении на вход "Направление счета" логической единицы, а в момент времени после tm— при поступлении логического нуля, Момент t +> соответствует заполнению реверсивного счетчика 4 при прямом счете, а момент tp — при обратном счете.

Восстановим связи накапливающего сумматора 2 и двоичного сумматора 5. Обязательным условием работы цифрового частотного модулятора должно быть равенство максимальных амплитуд напряжения на выходе ЦАП 7 и реверсивного счетчика 4. Это достигается выбором одинакового количест- ва разрядов чисел, подаваемых на двоичный сумматор 5 как с накапливающего сумматора

2, так и с реверсивного счетчика 4.

На выходе двоичного сумматора 5 формируются коды фаэ характеристических частот: к числам, поступающим с разрядов накапливающего сумматора 2, добавляются

1617652 возрастающие или убывающие по линейному закону числа с разрядов реверсивного счетчика 4 при прямом и обратном счете соответственно, В результате фаза колебаний на выходе

ЦАП 7 в первом случае линейно обгоняет, а в другом линейно отстает от фазы средней частоты. При этом происходит сдвиг средней частоты на величину, определяемую набегом фазы:

Составитель В.Чибисов

Техред М.Моргентал Корректор Т,Палий

Редактор А.Лежнина

Заказ 4130 Тираж 525 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Восстановим связи блока 6 постоянной памяти, в котором предварительно в двоичной системе через определенный угол записаны дискретные отсчеты косинусоидального сигнала. Путем опроса адресов блока 6 постоянной памяти числами, поступающими с разрядов двоичного сумматора

5, происходит считывание и формирование на выходе ЦАП 7 синусоидального сигнала.

Фильтр 8 нижних частот сглаживает имеющие место коммутационные выбросы.

Так как набег фазы выходных колебаний при модуляции определяется числом, записанным в двоичном сумматоре 5 с разрядов реверсивного счетчика 4, и в момент перехода информационного сигнала от логической единицы к логическому нулю это число остается неизменным, то переход от одной характеристической частоты к другой осуще=твляется без разрыва фазы, благодаря чему информация передается без иска5 жений и с высокой стабильностью частоты.

Задавая различные коды скачка в буферном регистре 3, можно изменить среднюю частоту выходных колебаний.

10 Формула изобретения

Цифровой частотный модулятор, содержащий опорный генератор, выход которого подключен к одному счетному входу реверсивного счетчика, выход которого соединен

15 с первым входом двоичного сумматора, выход которого через последовательно соединенные блок постоянной памяти и цифроаналоговый преобразователь подключен к входу фильтра нижних частот, вы20 ход которого является выходом модулятора, входом которого является другой счетный вход реверсивного счетчика, о т л и ч а юшийся тем, что, с целью расширения области изменения средней частоты вы25 ходного сигнала. введены последовательно соединенные буферный регистр и накапливающий сумматор, выход которого подключен к второму входу двоичного сумматора, при этом выход опорного генератора соеди30 нен с синхронизирующим входом накапливающего сумматора.