Устройство для вычисления фундаментальных симметрических булевых функций

Иллюстрации

Показать всеРеферат

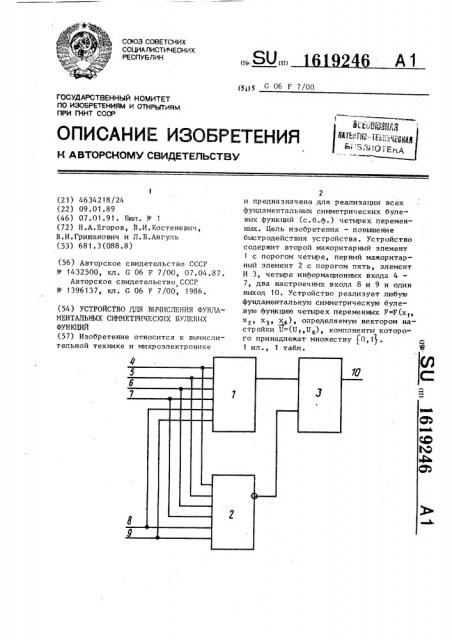

Изобретение относится к вычислительной технике и микроэлектронике 5 L 7 и предназначено для реализации всех фундаментальных симметрических булевых функций (с.б.ф.) четырех переменных . Цель изобретения - повышение быстродействия устройства. Устройство содержит второй мажоритарный элемент 1 с порогом четыре, первый мажоритарный элемент 2 с порогом пять, элемент И 3, четыре информационных входа 4 - 7, два настроечных входа 8 и 9 и один выход 10. Устройство реализует любую фундаментальную симметрическую булевую функцию четырех переменных (x,, хг, х3, .), определяемую вектором настройки U(Uj,U4), компоненты которого принадлежат множеству {0,l|. 1 ил., 1 табл. 10 (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ()9. (11) А1 (5k)5 С 06 F 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4634218/24 (22} 09.01.89 (46) 07.01.91. Бюл. - 1 (72} Н.А.Егоров, В.И. Костеневич, В.И.Гришанович и Л. Б.Авгуль (53) 681. 3 (088.8) (56) Авторское свидетельство СССР

11- 1432500, кл. G 06 F 7/00, 07.04.87.

Авторское свидетельство СССР

N -1396137, кл. Г 06 F 7/00, 1986. (54) УСТРОЙСТВО ДЛЯ В!ИИСЛЕНИЯ ФУНЛАМЕНТАЛЬНЫХ СИММЕТРИЧЕСКИХ БУЛЕВЫХ

ФУНКЦИЙ (57) Изобретение относится к вычислительной технике и микроэлектронике

2 и предназначено для реализации всех фундаментальных симметрических буле-. вых функций (с.б.A.) четырех переменных. Цель изобретения — повышение быстродействия устройства. Устройство содержит второй мажоритарный элемент

1 с порогом четыре, первый мажоритарный элемент 2 с порогом пять, элемент

И 3, четыре информационных входа 4

7, два настроечных входа 8 и 9 и один выход 10. Устройство реализует любую фундаментальную симметрическую булевую функцию четырех переменных Р=Р(х1, х, х» х ), определяемую вектором настройки 11=(U< U ), компоненты которого принадлежат множеству j0,1) .

1 ил., 1 табл.

1619246

11 ) и видом поляризации аргументов х1<ха< 3< Ф

Первообразная устройства имеет вид

С (х1 у 2у з < я- %(«+z ° з <

G G G G

Б,U<)(M<(x,х,х,х,,U1,U ), х,, если С =0 х, < если 6 =1 у я функция на выходе 10 уст» ройства

Значения сигналов на вход

Информационные входы И

1" "Х,Х Х Х4 х х х х+ 0

0 х4

x<1

1 х4

4 1

P <ак<ХЕХ<Х4Ч X

QX

P X

Х Х4

X < х<

Р4 аек х4 0 *. 0 хе х1 х<

Составитель В.Сорокин

Техред Л.Сердюкова Корректор Н.Ревская

Редактор A.Ìoòûëü

Заказ 47 Тираж Подписное

ВНИИ11И Государственного комитета по изобретениям и открытиям при ГКНТ СССР

f1303S, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород< Ул. Гагарина,101

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации всех фундаментальных симметрических буле5 вых Аункций (с.б.A.) четырех переменных.

Цель изобретения — повышение быстродействия устройства.

На чертеже представлена схема уст- fp ройства для вычисления фундаменталь-: ных симметрических булевых Аункций.

Устройство содержит второй мажоритарный элемент 1 с порогом четыре, первый мажоритарный элемент 2 с лоро- 15 гом пять, элемент И 3, четыре инАормационных входа 4 - 7, два настроечных входа 8 и 9, выход 10.

Устройство работает следующим образом. 20

На информационные входы 4 — 7 подаются двоичные переменные х, х, хя, х соответственно (или их инверсия х, х, х, х 4), на настроечные входы 8

< и 9 — сигналы настройки U1 и U соот-25 ветственно, значения которых принадлежат множеству (0,11.

На выходе 10 устройства реализуется некоторая фундаментальная симметрическая булевая Аункция четырех пеГ 0 ременных F(x(,x,х,х4) Е1 Р+,Р,1.,F4., F,Р, определяемая кортежом U=(U1 J

i=1 4.

Реализуемые. устройством функции представлены в таблице настроек.

Формула изобр етения

Устройство для вычисления Аундаментальных симметрических булевых функций, содержащее элемент И, выход которого соединен с выходом модуля, отличающееся тем, что, с целью повышения быстродействия, оно содержит два мажоритарных элемента, инверсный выход первого из которых соединен с первым входом элемента И, второй вход которого соединен с выходом второго мажоритарного элемента, i""é (i=1 4) вход которого соединен с

i-м входом первого мажоритарного элемента и i-м информационным входом модуля, j-й (j=1,2) настроечный вход которого соединен с (j+4)-м входом мажоритарного элемента и (j+4)-.м входом первого мажоритарного элемента.