Устройство для обработки нечеткой информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано в спецпроцессорах для обработки нечеткой информации, а также при построении технических средств моделирования рассуждений и автоматизации принятия решений в нечетких условиях. Целью .изобретения является расширение области применения путем обеспечения возможности вычисления результата операций нечеткой логики с ограниченными операциями и сокращение числа информационных выходов устройства. Устройство содержит два сдвиговых регистра , три коммутатора, группу элементов И, элемент И, элемент ИЛИ. Поставленная цель достигается благодаря применению унитарного кода и коммутаторов , обеспечивающих выдачу прямого а или инверсного нечетного значения S переменной. 1 ил., 1 табл. С/

СООЗ СОВЕТСКИХ . сОциАлистичесних

РЕСПУБЛИК щ) 5 G 06 F 7/50, 7/00

Ггъ -Г 141 "м & 1 ф ; „,2 ..., . . ! Я Т(";! ц (, д с.

1 .3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCHÎMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4632445/24 (22) 04. 01.89 (46) 07.01.91. Бюл. Р 1 (71) Таганрогский радиотехнический институт им. В.Л.Калмыкова (72) А.Н.Мелихов, В.П.Карелин и В.Н.Решетняк (53) 68 1.325(088.8) (56) Авторское свидетельство СССР

Ф 1256019, кл . G 06 F 7/00, 1984 .

Авторское свидетельство СССР

Р 1487028, кл. G Об F 7/50, 1987. (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано в спецпроцессорах для обработки нечетИзобретение относится к вычислительной технике и технической кибер, нетике и может бьггь использовано в специализированных процессорах для обработки нечеткой информации, а также при построении технических средств моделирования рассуждений и автоматизации принятия решений в нечетких условиях.

Целью изобретения является расширение класса решаемых задач эа счет вычисления функций нечеткой логики с операциями импликации, импликации конъюнкции, дизъюнкции, отрицания, штрих Шеффера, стрелка Пирса.

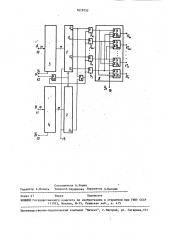

На чертеже представлена блок-схема устройства.

Устройство состоит иэ двух сдвиговых регистров 1 и 2, коммутаторов 3, „„Я0„„1619252 А 1

2 кой информации, а также при построении технических средств моделирования рассуждений и автоматизации принятия решений в нечетких условиях. Целью ,изобретения является расширение области применения путем обеспечения воэможности вычисления результата операций нечеткой логики с ограниченны" ми операциями и сокращение числа информационных выходов устройства. Устройство содержит два сдвиговых регистра, три коммутатора, группу элементов И, элемент И, элемент ИЛИ. Поставленная цель достигается благодаря применению унитарного кода и коммутаторов, обеспечивающих выдачу прямого или инверсного нечетного значения переменной. 1 ил °, 1 табл. и 4, группы элементов И 5, элемента И 6, элемента ИЛИ 7, коммутатора 8, причем каждый из коммутаторов 3,4 © и 8 содержит элементы И вЂ” ИЛИ 9, уст- ® ройство имеет входы 1О первого и 11 1 С второго операндов, тактовый вход 12, вход 13 пуска входы 14 — 16 настрой- Q ки, выходы 17 разрядов р.езультата. с, Регистры 1 и 2 служат для приема, сдвига и хранения унитарных кодов чисел, поданных с коммутаторов 3 и 4 соответственно ° Коммутаторы 3,4 и 8 служат для прямой или инверсной переда-: чи на свои выходы унитарных кодов, чисел, поданных на информационные входы.

В результате инверсной передачи на выходе коммутатора формируется отрицание А=1-А числа А, поданного на

его информационный вход.

1619252

Алгоритм работы устройства следующий.

Значения переменных Л и В, поданные на информационные входы соответственно первого и второго коммутаторов, затем из коммутаторов передаются (в зависимости от вида операции) либо без изменения, либо в преобразованном виде (в виде отрицания) соответственно в первый и второй сдвиговые регистры. После этого осуществляется одновременный сдвиг содержимого обоих регистров. В первом регистре содержимое сдвигается в сторону старших раз" 15 ряпов, а во втором — в сторону младших. Сигналом окончания сдвига и формирования ограниченной сутаны чисел „ записанных в регистрах, будет наличие единицы либо в старшем разряде перво" 20 го регистра, либо в младшем разряде второго регистра. По этому же сигналу содержимое первого регистра передается на третий кожтутатор, который опять же в зависимости от вида операции ли- 25 бо передает число из первого регистра в неизменном виде на выходы устройства, либо формирует отрипание полученного числа и передает его на выход.

Каждый 1-й из трех коммутаторов по управляющему сигналу у =1, где j=1,3, передает число с информационных входов на выходы без изменений, а по сигналу у =0 передает на выходы отрицание числа, поданного на информационные входы.

3S 1 аким о бр а з ом, приз на ко, опр ед еляющим получе же результата той или .. иной из выполняемых устройством логи ческих операций над переменными А и В, будет набор значений управляющих сиг40 налов (у1, у, уэ) на управляющих входах трех коммутаторов. Соответствие между выполняемой операцией и набором значений управляющих сигналов у, у, у показано в таблице, Простота алгоритма выполнения указанных операций свидетельствует о преимуществе унитарного кода перед двоичным в данном случае, Устройство работает следующим об 50 разом.

На входы 10 и 11 кожтутаторов 3, и 4 подаются унитарные m-разрядные коды значений переменных соответст55 венно А и В. По сигналу с входа 13 устройства значения с выходов коммутаторов 3 и 4 записываются соответственно в регистры 1 и 2. На вход 12 устройства поступают тактовые импульсы, которые через элемент И 6 проходят на входы управления сдвигом регистров 1 и 2. Содержимое регистра 1

I сдвигается в сторону старших разрядов, а содержимое регистра 2 - в сторону младших разрадов до тех пор, пока либо. в старшем разряде регистра 1, либо в младшем регистра 2 не появится единица. Как только это произойдет, на выходе элемента ИЛИ 7 появляется единичный сигнал, который закрывает элемент И 6 для прохождения тактовых импульсов на входы управления сдвигом регистров и одновременно открывает элементы группы И 5 для передачи содержимого регистра 1 на информационные входы коммутатора 8.

Формула и з обр ет ения

Устройство для обработки нечеткой информации, содержащее первый и второй сдвиговые регистры, группу элементов И и элемент ИЛИ, причем выходы разрядов первого сдвигового регистра соединены с первьжи входами соответствующих элементов И группы, о т л и— ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач за счет вьгчисления функций нечеткой логики с операциями импликации, импликации коньюнкции, дизъюнкции, отрицания, штрих Шеффера, стрелка Пирса, в него введены три коммутатора и элемент И, причем входы первого и второго операндов устройства соединены с информационными входами соответственно первого и второго коммутаторов, выходы которых соединены с информационными входами соответственно первого и второго сдвиговых регистров, выход i-ro разряда первого сдвигового регистра (i=1,2,...,m, где m - старший разряд входных операндов) соединен с первым входом -ro элемента И группы, выход которого соединен с первым входом

i-го элемента И группы„ выход которого соединен с информационным входом

i-ro разряда третьего коммутатора, выход ш-ro разряда первого сдвигового регистра соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого разряда второго сдвигового регистра, выход элемента ИЛИ соединен с вторыми входами элементов И группы и инверсным входом элемента И, .прямой вход которого сое"

52 6

i-ro элемента 2И-ИЛИ соединен с информационным входом i-ro разряда коммутатора, второй прямой вход каждого элемента 2И-HJIH соединен с. управляющим входом коммутатора, третий прямой вход i""го элемента 2И-ИЛИ соединен с информационным. входом (m-i+1)-ro раз" ряда коммутатора, управляющий вход которого соединен с инверсным входом элемента 2И-ИЛИ, выходы элементов 2ИИЛИ соединены с выходами соответствующих разрядов коммутатора. (6(92

Операция

Формула

D in (1, А+В)

Р=1-D=D

Б=шн) (1, 1-А, +1-В) =

=ппп((,1+В)

К=1-S=S

Х =т л(1,А+В) =A B

? =талип(1,А+В)=В-+А

А=1-А, (B=0)

Дизъюнкция

Стрелка Пирса

Штрих ШеААера

Конъюнкция

Импликация

Отрицание динен с входом тактовых импульсов устройства, вход настройки которого соединен с управляющими входами коммутаторов, выход элемента И соединен с входами сдвига первого и второго сдвиговых регистров, вход разрешения записи которых соединен с входом пуска устройства, выход которого соединен с выходом третьего коммутатора, первый сдвиговый регистр выполнен сдвигающим в сторону старших разрядов, причем кажцый коммутатор содержит m элементов 2И-ИЛИ, первый прямой вход

1 1

1 1

0 0

0 0

0 1

1 0 0 1 1 1

О

1

1

1619252

В

Составитель А.Зорин

Редактор А.Мотыль Техред Л.Сердокова Корректор д.бескид

Заказ 47 Тираж Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101