Скалярный умножитель векторов

Иллюстрации

Показать всеРеферат

Изобретение относится к цифр овой вычислительной технике и может быть использовано при построении машин , работаюпих в алгебре матриц, универсальных машин, а также специализированных вычислительных устройств и систем. Целью изобретения является повышение технотогнчности путем создания однородного устройства, увеличения разрядности картежя чисел при незначительном количестве наружных выводов, сокращения аппаратурных затрат при сохранении высокой производительности устройства. Устройство содержит блок 1 ввода, матрицу 2 вычислительных элементов, блок 3 суммирования , мультиплексор 4, блок 5 синхронизации с соответствующими связями. 3 з.п. ф-лы, 17 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕО-<ИХ

РЕСПУБЛИН

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4445295/24 (22) 22.06 .88 (46) 07.01.91. Вюл. М 1 (71) Институт кибернетики им. В.М,Глушкова (72) B.À.Вышинский и 10.Я.Ледянкин (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 56 1963, кл . G 06 F ?/52, 1975.

Авторское свидетельство СССР

Р 905814, кл . G 06 F 7/52 1979 (54) СКАЛЯРНЫЙ УМНОЖИТЕЛЬ В! .КТОРОВ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано при построении ма„„SU „„1619254 А 1 (5!)5 G 06 Р ?/52, !5 347

tlMH работающих B алгебре матриц, уни-. версальных машин, а также специализированных вычислительных устройств и систем. Целью изобретения является повышение технологичности путем созда— ния однородного устройства, увеличе— ния разрядности картежа чисел при незначительном количестве наружных выводов, сокращения аппаратурных затрат при сохранении высокой производительности устройства. Устройство содержит блок 1 ввода, матрицу 2 вы— числительных элементов, блок 3 суммирования, мультиплексор 4. блок 5 синхронизации с соответствующими связями.

3 3 .и. A — лы, 17 ил.

1 6 19354

Изобретение относится к цифровой вь>числительной технике и может быть использовано при построении машин, работа>ощих в алгебре матриц, универсальных машин, а также специализированных вычислительных устройств и систем, Целью изобретения является повышение технологичности за счет создания 10 однородного устройства, увеличения разрядности картежа чисел при незначительном количестве наружных выводов и сокращения аппаратурных затрат при сохранении Высокои производительности устройства.

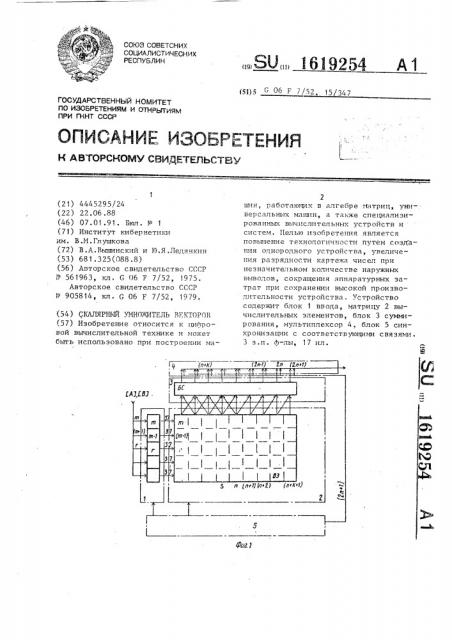

Па фиг. 1 приведена схема устройства; на фиг. 3 — блок ввода; на фиг. 3 — матрица вычислительных эле..>ентов; на фиг. 4 — схема вычислитель- 0 лого элемента; на фиг. 5 — схема сумматора; на д>иг. б — внутренняя -струк.гура сумматора; на фиг.7 — схема геператора тактовых импульсов; на фиг. 8 — внутренняя структура генера- 25 тора тактовых импульсов; на фиг. 9 схема узла управления; на фиг. 10 тактовая диаграмма; на фиг . 11 — временная диаграмма; на д>иг. 12 — внутренняя структура элемента ввода; на фиг. 13 — схема узла установки реги-.стра; на фиг . 14 — 16 — внутренняя структура вычислительного элемента; на фиг. 17 — внутренняя структура блока суммирования.

Устройство содержит блок 1 ввода, матрицу вычислительных элементов 2, блок 3 суммирования, мультиплексор 4, блок 5 синхронизации. Блок 1 ввода состоит из m элементов б ввода. Матри-, ца вычислительных элементов состоит из вычислительных элементов 7. Блок суммирования содержит сумматоры 8.

Глок управле>>ия состоит из генератора 9 тактовых импульсов и узла 10 уп- 45 равления коррекций, Злемент ввода состоит из узла 11 ввода., узла 12 управления, узла 13 преобразования кода, узла. 14 установки регистра. Узел ввода. содержит два э.>емента 2И 15, узел управления содержит элег>ейт 2И-НЕ 16, элемент ЗИ 17 и триггер 18. Узел преобразования кода содержит два элемента ИЛИ-НЕ 19, триггер 20. Узел установки регистра. содержит элемент 2И 15. Вычислительный элемент содержит пять регистров

2? памяти, три коммутатора 23, трехвходовый комбинационный сумматор 24, Кроме того, первые вычислительные элементы каждой строки матрицы вычислительных элементов содержат элемент

2И 25 и элемент 2 ИЛИ 26. Сумматор содержит семь триггеров 27 и два трехвходовых комбинационных сумматора ?8.

Генератор тактовых импульсов содержит четыре элемента 2И вЂ” НЕ 29. Узел управления коррек> лей содержит счетчик 30, два дешифратора 31 и один дешид>ратор

32 связи между элементами ЗЗ вЂ” 82 уст— ройства.

При работе устройства возможны загрузка всех строк матриць1 вычислительных элементов одновременно и загрузка строк матрицы "волной", когда на первом такте (при двухд>азной тактировке м Л - л у--с,,ф = I< ) заносят первые разряды в первую строку, на втором такте во BTOрую строку матрицы заносят первые разряды, а в первую — вторые разряды.

На r-м такте в первую строку заносят

r-й разряд первой пары сомножителей, а в r-ю строку — первый разряд r-й строки.

Для определенности рассмотрим параллельную (одновременную) загрузку матрицы.

Число входных шин в устройстве равно m по числу строк в матрице, элементов 6 ввода, информационных входов в блоках ввода и, в целом, в скалярном л умножителе. На 6, в блок ввода заносят знаковый разряд множителя (В), представленного дополнительным кодом. Он равен Q =1 либо Я >=--О. В скалярный умножитель через r-й (r=1,m) информационный вход он поступает на информационный вход r-го (r=1 m) блока

h.

У ввода. На >, по этим же связям на информационный вход г-го элемента 6 ввода поступает знаковый разряд Я», множимого. В данном случае и далее при работе скалярного устройства за л л

l.., оидн такт . (> и i) в устройство - :BBo дят S-e одноименнйе разряды (первоначально знаковые разряды всех пар сомножителей) числовых компонент вектора А(а,... а,... а„») и вектора

В(Ь1,...,Ъ„. ..Ь„,). Они организованы в пары сомножителей вида (а bi,..., а b» ...а„„Ь,„), т.е. в r-й строке будут перемножены r-e компоненты векторов А и В. Назначение r-го элемента ввода — развернуть одну последовательность чередующихся бит векторов (а>,,bÄ) в две параллельные последовательности -битов векторов (а->,) 5

161925 и (Ь1,), преобразовать (если необходимо) сомножители в соответствующий код по знаку кода множителя, выдать последовательности бит мнолммого в прямом (b „) или обратном (а„) коде, а множителя — в прямом (Ь»,) или до— пол т ьном (bp)% коде абот- ь признак установки регистра множимого в "О" либо "1", выработать признак коррекции (Кор . В) r-ro псевдорезультата (или отсутствия ее) по знаку множимого ("1" или "О" соответственно) .

С помощью узла 11 ввода r-го элемента 6 ввода коммутируют последовательность битов числа а г тактовым снижением ь, который по тактоъому вхо—

7Г ду 45 второго элемента 2И разрешает передачу S-го бита числа а„по информационному входу 33 через второй 20 элемент 2И угла 43 ввода. Последовательность битов числа b коммутируют на тактовом сигнале 7;, который по тактовому входу 44 разрешает передачу

S-ro бита b1, по информационному вхо- 25 ду 33 через первый элемент ?И. Таким образом на выходе узла 11 ввода бло— ка 1 формируют две последовательности битов: числа а по первому выходу, числа Ь», — по второму выходу. Эти вы- 30 ходы одновременно являются вторым и первым соответственно информационным входом узла преобразования кода. Второй выход узла 11 ввода связан дополнительно с первым информационным входом узла 12 управления.

При синхронной с Ы подаче импуль8 сов ь на тактовом входе 42 и У1 по

» первому управляющему 34 входу узла 12 управления блока 1 ввода, по знаку множителя Я =1 или Я =0 триггер узла управления устанавливают в "1" или

"0". Одновременно по цепи первый информационный вход узла преобразования кода — первая схема 2И второго элемен та 2И-2И-2ИЛИ знаковый разряд Я мно6 жителя в коде представления поступает на второй выход узла преобразования хода, который является и вторым выходом r-го элемента 6 ввода. Это возможно потому, что в начальный момент триггер IK-типа, например, узла преобразования кода стоит в "О" и своим инверсным выходом открывает первую схему 2И второго элемента 2И-2И вЂ” 2ИЛИ.

Установка триггера в узле 12 управления в "0" или "1" означает, что знаковый разряд Qllмножимого, который следует непосредственно за Я, будет

6 скоммутирован на первый выход 37 узла преобразования кода в прямом или обратном коде в зависимости от состояния триггера "0" или "1" в узле ввода по цепи второй информа»» »оннь»й вход узла преобразования кода — первая схема 2И или первый элемент HE — вторая схема 2И первого элемента 2И-2И-2ИЛИ соответственно.

Таким образом, знак множитсля Q> ™О либо 1 означает„что при умножении коммутации числа Ъ„будет в коде представления либо с преобразованием его в дополнительный соответственно. При этом все нули младших разрядов и первую единицу коммутируют с первого информационного входа узла преобразования кода на его второй выход, который является вторым выходом блока 1 ввода, в прямом коде, а следующие биты числа — в инверсном коде. Это происходит потому, что первая единица млад»»его разряда установит ЕК вЂ тригг по входу синхронизации в "1", а следующие старшие биты числа Ъ, коммутируют на цепи первый информационный вход узла преобразова»»ия кода — второй элемент

HE — вторая схема 2И второго элемента

2И-2И-2ИЛИ вЂ” второй выход элемент б ввода.

Знак множимого, равный Яд=О (если а„ О) и равный Я =1 (если а,(0), которнй определяет потенциал на первом выходе узла 13 преобразования кода, определяет нулевой или единичнь»»» потенциал на установочном выходе 41 узла установки регистра, поскольку импульс Я » стробируется импульсом У2 из блока 5 управления (по первому входу 35 узла установки регистра 14 он разрешает коммутацию Q< через элемент

2И узла установки регистра 14) . Кроме того, если триггер узла управления установлен в "1", то после выполнения операции перемножения r — и пары чисел на втором управляющем выходе 40 узла

12 управления вырабатывают сигнал коррекции (Кор. В) . Это происходит - потому, что элемент ЗИ открыт прямым выходом триггера узла управления, импульсом

1;2 (из блока 5 управпеи»я) по тактовому входу 45 и управляющим сигналом

УЗ по управляющему входу 36 блока ввода 5 и узла 12 у-правлени-я одновременно. Когда триггер узла управления находится в "О", сигнал "Кор.В" на первом управляющем вьгходе 39 не вырабатывают.

1619254

Одновременно с сигналом "Кор.В" на первом управляющем выходе 39 и узле 12 управления блока ввода вырабатывают элементом 2И-НЕ сигнал "Кор .А".

Это выполняется потому, что синхронно с управля«ащим сигналом У3 по второму управляющему входу блока 1 ввода по тактовому входу 44 поступает импульс С, . л

Организация работы блока управле«мя возможна на базе триггеров других типов.

По значению Яд =1 с установочного

41 выхода r-ro блока ввода все первые 1

J триггеры первых регистров памяти Я-х (S=1, (n+k+1) ) вычислительных элементов 7 устанавливают в "1", так как все установочные входы этих триггеров обьедипепы и подключены к установочному «зходу 54 и к выходу 41 r.-ro (r=1,m) элемента ввода, Бсе первые триггеры первых регистро«з памяти вычислительных элементов

r — и строки (х=1, и) выполнены на Лвой (5 ных триггерах (типа ТТ) и организованы в (и+1:+1) — разрядный регистр сдвига (кода множимого), тяк как первый

««ход S Го (Я=l (n+k+1) ) вычислитель ного элемента (триггера) соединен с первым вь«ходом 48 (S-1)-го вычислительного элемента (триггера) .

Бсе вторые триггеры первых регист-" ров памяти BbDIHcJIHTBJIbHb«x элементов

r-й строки (r=1,m) также выполнены на двой««ых триггерах и аналогично организованы в и-разрядный регистр сдвига (кода множителя), так как первый вход 55 $-го (Я=l,v) вычислительного элемента (триггера) соединен с первым выходом 59 (S-1)-го вычислительного элемента (триггера .

Б р егистр сдвига, ор гани зовапный из первых триггеров первых регистров памяти вычислительных элементов 7 r-й 45 строки последовательно, разряд за разрядом, начиняя со знакового и далее старшими разрядами вперед вводят (n+ i ) -разрядное число (я ) кода мно««лмого в прямом (а,,) или обратном

50 (а ) коде.

В регистр сдвига, аналогично организованнь«й из. вторых триггеров первых регистров памяти вычислительных элементов 7 r-й строки но млад«««ими

Ф

«55 разрядами вперед, вводят все и, разрядов числя (Ь ) исходного ходя множителя (Ь«) или в дополнительном (b«)y коде, что равносильно абсолютной величин исходного значения числа Ь при умножении знаковый разряд множителя всегда (по алгоритму) равен нулю.

Текущие S-e (Я=l, (и+1) ) разряды г-й пары сомножителей запомина«от в первом и втором триггерах первого регистра памяти r и строки вычислительных элементов. Своими значениями на выходе элементов 2И и 2ИЛИ они определяются — уровень управляющих сигналов соответственно на третьем 52 и четвертом 53 управляющих входах; уровень сигнала на выходе первого коммутатора Я вЂ” го (S=l) вычислительного элемента r-й строки матрицы. Оч соответствует "i" в случае, когда биты текущих разрядов обоих сомножителей совпадают и равны " 1", и соответствует

"0" в остальных случаях.

Уровень сигнала на третьем управляющем входе 5?, соответствующий "1" или "0" разрешает (запрещает) коммутацн«о текущих значений первых триггеров первых регистров памяти Я-х (S=2,n) вычислительных элементов данной строки, а аналогичные уровни сигналов на четвертом управляющем входе

53 разрешают (запрещают) коммутацию текущих значений вторых триггеров первых регистров памяти вычислительных элементов.

Таким образом, текущий разряд кода множителя (Ь ) разрешает "1" или запрещает "0" на третьем управляющем входе 52 коммутацию текущего частичного произведения, о«ормируемого кодом множимого (а,,) в сумматоры (через их первые входы Я-х (S=2, (и+К+1) ) вычислительных элементов r-й строки с запоминанием значений переноса и результата в первых триггерах (их выходы 59 и 61 соответственно) каждого вычислительного элемента. Аналогично текущий разряд кода множимого (а«,) разрешает или запрещает "1" или "0" на четвертом управляющем входе 53 коммутацию текущего значения частичного произведения, о«ормируемого кодом мно" жителя (Ь«,) в сумматоры (через их вторые входы) S-х (Я=2, (n-1)) вычислительных элементов r-й строки с запоминанием значений переноса и результата во вторых триггерах (их вьг оды

60 и 62 соответственно) вычислительного элемента.

В итоге в каждой r-й (r=l m) строке матрицы вь«числительных элементов с помощью первых регистров памяти вы1h19254 а Ь р (ар), (Ь„Ч к((а I ) „) ((Ь„) 1„) (+2/8) > (-4/8)=0.01 »II1.1И=1.101х0.100=1.110100+0.100=1.111000=(— 8/64) в) а) А 1.101 ок

В 0.100 дк

11101

1.110100 Пр.

0. 100 Кор .

111 )00

О )0100

0001-0

0011-00

1110-100

1! 01-3100

000010 >

111ÎÎÎ )0000

0 f) 0 0

1 .1101 È Пр .

1.1 >О Кор.

1.111000 Рез..

i.111000 Рез. числительных элементов, организованных в строке в виде регистра сдвига, формируют частичные произведения по предлагаемому алгоритму, который модернизирует два известных. Первый из них формирует частичные произведения в прямых кодах в виде некоторого треугольника, а второй — в дополнительных кодах. Суть алгоритма в том, что на входах сумматора формируются частичные произведения по правилу

Ь,QA à, а а а Ь Ь Ь а Ы,=О

Ь ядадà, aza,b bg а, Юд=О либо 1

b,Яд b3>g>a„a

Ь ЯдУд Уд Юда а1

Суммирование строк приведенной таблицы равносильно таковой

Яда! а аа4 b<

ЦдЯда а а аф Ь2

Qp (ад Ода„а аз аа Ь дд ддя„рда„а zà ад bq.

Таким образом r-я строка (r=l m) матрицы вычислительных элементов позволяет выполнять операцию умножения двоичных чисел в дополнительных кодах с интерпретацией знаковых разрядов как числовых при одной корректи- 45 рующей операции. Она состоит в прибавлении кода множителя, полученного после преобразования его в дополни— тельный, если исходный сомнояжтель был отрицательный. При этом по струк50 туре блока ввода корректирующий код множителя к моменту коррекции в требуемом виде находится во вторых триггерах первого регистра памяти вычислительных элементов r-й строки матрицы.

В умножителе для выполнения операции умножения всех пар сомножителей, которые вводятся последовательно, Отсутствие хоропих алгоритмов для одновременного преобразования кода в дополнительный и его поразрядной передачи в устройстве через элемент ввода и далее в r-ю строку через Я-й ($= 1) вычислительный элемент старними разрядами вперед (в данном случае кода множимого) затрудняет реализацию такого алгоритма. Для избежания трудностей, возникаюлИх с преобразованием кода множимого в дополнительный с пе" редачей его в устройстве старними разрядами, предлагается передавать его обратным кодом (если()д =1) с последующей коррекцией псевдореэультата в вычислительных элементах r-й строки матрицы. Коррекцию выполняют в виде сложения кода множителя, преобразованного (при Яд=1) в дополнительный с псевдорезультатом, накопленным в устройстве разряд за разрядом, для (и+1)-го разряда требуется (и+1) такт (01 и 2), так как частичные произведения II псевдопроизведения формируются параллельным способом за тот же (и+1) такт, один такт необходим для анализа знаков сомножителей и установки триггеров, хранящих значения кода множимого, один такт необходим для выполнения коррекции псевдорезультата. После чего получают двухрядный код результата и переносов. В результате за (и+1+2) та ла (c, и c ) в каждой r-й строке (r=1, m) матри1 I формируют частичные произведения m пар сомножителей а,,Ь„.

Каждое частичное произведение коммутируют на первый вход сумматора каждого вычислительного элемента из перaoro регистра памяти через первый

1619254

12 коммутатор. Одновременно через второй и третий коммутаторы поступает двухрядный код значений переноса и результата на второй и третий входы сумматора. Он поступаег с выходов триггеров четвертого и. пятого регистров памяти предыдущей (r-1)-й (r=1,m) строки матрицы.1 Каждый из пяти регистров памяти состоит из двух триггерову lp причем первые три регистра находятся на входе сумматора (по числу входов

его) а четвертый и пятый — на входе сумматора по числу выходов его. В нечетньтх триггерах регистров памяти S-x,5 (=1, (n+k+1)) вычислительных элементов хранятся частичные произведения, формируемые кодом (а„) множимого (первый регистр памяти), а также значения переноса и результата, которые вырабатывает множимое в предыдущей (r-1)-й (r=1, m) строке. С этой целью используют второй и третий регистры памяти на входе сумматора и четвертый с пятым регистры на выходе сумматора, 5

В четных триггерах регистров памяти

S-х (S=1, тп) вычислительных элемен.: тов хранятся частичные произведения, формируемые кодом (Ь >) множителя (первый регистр памяти),: а также значения переноса и результата, которые вырабатываются на предыдущей строке кодом множителя. С этой целью те же регистры находятся на входе и выходе сумматора. Раздельная тактировка дву- З> ( мя фазами позволяет сэкономить аппаратуру сумматоров. Лри этом в нечетные триггеры первых трех регистров памяти г-й строки, в которые, в свою очередь они были записаны из нечетных gp триггеров четвертого и пятого регистров памяти (r-1)-й строки на такте и

0i переписывают значения переноса и результата произведения предыдущей и пары сомножителей на такте с, В чет- 45

Z ные триггеры регистров памяти соответствующие значения записывают наоборот — в первые три на (, а в четверЛ тый и пятый на

Значение переноса (результат), которое получено в S-м (Я=1, (n+k)) или (S=1, (n+k+1)3 соответственно вычислительном элементе в качестве частичного произведения (a, ° Ь) 1 ) кода множителя и множимого соответственно (r-1)-й (r=2,m) строки матрицы с первого 59 и третьего 61 соответственно информационного выхода вычислительного элемента 7, поступает на пер" вый 55 и третий 57 соответственно информационный вход (S+1) -го (S=2, (пт)тт)) н (S-то, S=l n+k+1) ) вычислительного элемента r-й строки матрицы вычислительных элементов.

Аналогично значение переноса (рееупьтете) которое получено и S-м (S=1, (n-))) н (Б=), n) соотеетстненно вычислительном элементе в качестве частичного произведения (ат,„,-Ь). ) информативно кодом множителя в (r-1)-й (r=2,m) строке матрицы с второго 60 и четвертого 6? соответственно информационного выхода вычислительного элемента 7, поступает на второй 56 и четвертый 58 соответственно информационный вход (S+1), (S=2,п) и S-ro (S=i n) соответственно вычислительного элемента r-й строки матрицы вычислительных элементов.

Такое построение вычислительных элементов в скалярном умножителе при двухфазной тактировке в устройстве позволяет сэкономить на су(заторах, одни и те же комбинационные трехвходовые сумматоры с коммутацией на вхо де и двухразряднымн регистрами на их входе и выходе используют вначале для суммирования одной, старшей, части частичного произведения, сформированной от кода множимого, а затем для суммирования другой, младшей части его, сформированной кодом множителя.

В S — х (S=n+k+1) вычислительных элементах, начиная с S=ll+1, формируют значения переносов и результата суммирования только от кода множимого.

Частичное произведение от кода множи" мого на k (k=log m) больше, чем от кода множителя. Зто связано в основном с организацией накопления сумм та пар сомножителей. Увеличение разрядной сетки происходит автоматически в каждой строке скалярного умножителя.

В матрицу оба сомножителя поступают одинаковой значности — (и+1)-й разряд, где n — число информационных разрядов, и один дополнительный знаковый разряд числа, представляемого в дополнительном коде.

Регистр сдвига, организованный пер-. выми триггерами первых регистров памяти S-х (S=1, (и+К+1)) вычислительных элементов r-й (r=1,m) строки, по установочному 54 входу устанавливают в

"1" или "0" в начале умножения, В процессе ввода новых текущих значений кода множимого в младшие разряды стар1б19254

14 шие разряды естественно остаются в состоянии их начальной установки. Это происходит в вь»числительных элементах, начиная с первого до (и+1)-го, т.е. до момента, когда они будут заменечы

5 соответствующим разрядом множимого, сдвинутым из блока 1 ввопа. Но k старших разрядов остаются в состоянии начальной установки. Это соответствует правилу умножения чисел в дополнитель— ном коде, когда старине разряды час— тичного произведения заполняют по правилу арифметического сдвига.

Операцию умножения чисел a) и b 15 в r-й строке выполняют следую »им образом.

Вводят знаковый Я разряд кода множителя а> и на тактовом импульсе л

»» его значение запоминается в триггере узла управления блока ввода. На тактовом импульсе ь вводят знаковый разряд Я . Прямой и инверсный выходы триггера узла управления блока ввода управляют коммутацией знакового раз- 25 ряда (Qg (а затем и информационных разрядов) кода множимого через первый элемент 2И-2И вЂ” 2ИЛИ в прямом или обрат— ном коде на первый вход S-го ($=1) вычислительного элемента. Но знаковый разряд (D p с помощью узла установки регистра блока ввода по его вьгходу 4 1 устанавливает в "1" или "0" все первые триггеры первых регистров памяти вычислительных элементов r-й строки.

Поскольку при умножении Q< =0 всегда (по алгоритму)> то установка в 1 или "0 первых триггеров первых ре Т истров памяти S-x (S=1, (n+k+1)) вычислительных элементов r-й строки (г=1,ш)40 равносильно тому, что на первом тактол вом импульсе ь» и». осуществлен ввод знаковых разрядов кодов сомножителей в (k+1) é разряд. Дальнейшей обработке подлежат оставшиеся п ин4 формационных разрядов кодов сомножителей.

Положим для определенности, что

r строка скалярного умножителя обрабатывает два сомножителя à „ b„, которые взяты из примера, приведенного выше (+2/8)x(-4/8)=, )..01()х1.10 )=1.101х к0. 100=1 . 11 010< >+О. 10 )=1 . 1 110 )0= (-8/64 ), На первом тактовом импульсе триггер узла управления блока ввода устанавливают в "1" с дальней»1»им преобразованием в дополнительньй код, т.е. (Ъ».), а аг — в обратный, т.е. al следующим образом. На, и > И =1 с установочного выхода 41 блока ввода потенциал уровня единичного сигнала устанавливает в "1" все первые триггеры первых регистров памяти S-x ($=1, (n+k+1)) вычпслитсльнь»х элементов r — и (r=l,m) строки, что соответствует (п, »,n+k+1)) разрядам частичного произведения (включая знаковый) . л

На втором тактовом импульсе и cz через блок ввода в первый и второй триггеры первого регистра памяти записывают значения младшего заряда множителей (Ь „) равное "0", в дополнительном коде и старшин разряд множимого, равный "1" в обратном коде, сомножителей Ь и а, На четвертом управляющем входе вычислительных элементов установлен высокий пот廻— циал единичного уровня. Он разрешает коммутацию значений вторых триггеров первых регистров памяти S — х (S=1 (и-1}) вычислительнь»х элементов на входы сугьматоров, значения результата и переноса с которых на тактовом сигнале с запишутся во вторые триггеры четвертого и пятого регистров памяти.

Еди нич ные з на ч ения п ер вых три г r ер ов первых регистров памяти S — x (S=1, (и+1с+1)) вычислительных элементов не скоммутируют в сумматор. Учитывая, что нет совпаде»п»я текущих разрядов, в суж»атор S-ro (S=1) в:»числительного элемента через первый-. коммутатор поступит "0 . В результате в первые триггеры четвертого и пятого регистров памяти на тактовом сигнале а» запишутся нули. При этом по второму и третьему входам сумматора с предыдущей (r l)-й строки вычислительных элементов поступают нули. Это равносильно старшей части частичного произ,»„ения вида 0003. В итоге полное частичное произведение равно д000030. л

На третьем Tpêòoâîì импульсе а» и вводят аналогичные значения ини формационных разрядов кодов сомножителей. Второе частичное произведение будет также аналогично 0 )000000. л

На четвертом тактовом импульсе с» и вводят третий информационный (со стороны младших) разряд множителя, равный "1", и третий информационный (со стороны старших) разряд множимого, равный 0 . На четвертом и третьем . управляющих входах устанавливают потенциал нулевого и единичного соответственно уровня, т.е. во вторые триггеры четвертого и пято; о регист16

1б19254 ров памяти пишут нули "— — 000 (частичное произведение, формируемое кодом множителя) и 1110 " (частичное произведение, формируемое кодом множимого), а также 0 в S-м (S=1) вычислительном элементе, что дает — — 0- — ", а в итоге на таковом ими и пульсе,, и ь< во вторые и первые ,триггеры четвертого и пятого регист- 10 ров памяти запишут очередное частичное произведение вида 1110000.

"<

На пятом тактовом импульсе и < вводят четвертый информационный (со стороны младших) разряд множителя,15 равный "0", это знаковый разряд множителя и по алгоритму он всегда равен

"0", и четвертый информационный (со стороны старших) разряд множимого, равный "1". Потенциалы на четвертом 20 и третьем управляюших входах равны соответственно "1" и "0", поэтому код 0100 множителя, сдвинутый во вторые триггеры первьв: регистров памяти за предыдущие такты, скоммутируют в сумматор и далее запишут во вторые триггеры четвертого и пятого регистров памяти. Код 1101 с выходов первых триггеров первых регистров памяти

B сумматоры вычислительных элементов 30 не коммутируют. В результате пятого такта будет сформировано частичное произведение вида 0000100.

На шестом тактовом импульсе

"< и <, иэ блока синхронизации поступает З»

2 и, п и. импульс УЗ длительностью < — ь + &zan

При этом с первого 39 и второго 40 управляющих выходов блока 1 ввода по. ступают сигналы управления, которые независимо от значений первого и вто- 0 рого триггеров первого регистра памяти 8-ro (S=1) вычислительного элемента строки установит на третьем и четвертом управляищих входах $-х (S=2 (n+k+1) ) и (5=2,n) соответственно по- g5 танциалы низкого и высокого уровня, что означает запрет ввода кода множимого и разрешение коммута ы корректирующего кода множителя (Кор .А) и (Кор. В) соответственно. Это равно- — 50 сильно новому частичному произведению

0000100.

Легко проверить, что суммирование частичных произведений, полученных

55 вышее, дает правильный результат

0.000000 ЧПэн.

0.000000 ЧП 1

1.110000 ЧП 2

0.,00010 .) ЧП 3

0.000100 Кор, 1.111001) Рез.

На четвертом тактовом импульсе <,< и и в первый и второй триггеры первого регистра памяти коммутируют третий разряд со стороны мпадших разрядов кода множителя, равный "1" и третий разряд кода множимого со стороны старших, который равен "0", Первонаи, чально (до подачи < ) оба триггера (основной и дополнительный) в регистре находятся соответственно в состоянии 11 и 00. После тактового импульса < их состояние изменится с учетом входных значений на 11 и 10, а после — на ()1 и :)1 соответственно. И лишь на инверсном значении синхроимпульса оба (основной и дополнительный) триггера будут в состоянии 00 и 11. Отсюда видно, что синхронизация реализации конъюнкции на входах первого коммутатора S-ro (S=1) вычислительного элемента строки с выходов первого и второго триггеров первого регистра памяти возможна, если использовать выходы только основного и дополнительного триггеров. В противном случае ошибки неизбежны. Анализ потактной работы устройства показывает, что операция умножения выполняется за время, =2+(n+1) тактов, где г. — информационных разрядов, один знаковый.

Это следует из того, что по методу умножения знаковые разряды обрабатывают аналогично информационным за (п+1)-й такт. Кроме этого требуется один такт для установки разрядов множимого по его знаку, а также один такт для выполнения коррекции.

1.

При органиэации параллельной загрузки матрицы все одинаковые разряды чисел векторов скалярного умножителя формируют . частичные произведения одинаковой значности и в целом за и+3 такта они будут сформированы во всех строках устройства. Это означает наличие значений результата и переноса во всех (n+k+1) вычислительных элементах, т. е. в (2n+k+1) разряде двухрядного хода произведения. Для получения однорядного кода результата с распространенными переносами выполняют m и л тактов (<< + <. ), в течение которых переносы из первой строки передают в

m-ю. Отсюда видно, что время Т загрузки и очистки матрицы от переносов, 1 6 19252(Возникающих в вичислительных элементах, равно

Т =((n+3)+m) (,=(2n+3)(, при /п=п.

При организаиии работы матрицы

"волной вычислительный элемент r-й строки загруя(ается, а затем и выгру— жается (освобождается от переносов) на один такт ((,, и (. ) раньше, чем в л. л (г+1) — и строке матрицы. При m=(n+3)

Л за время „=(n+S) (полной загрузки первой строки в последнюю строку поступает первый разряд частичного произведения сомножителей а и Ь„„ ;r1e через t=(n+3,(значения переносов

2... и результата суммирования в первой строке поступают в m-ю (m +3) строку.

Отсюда следует, что через t=(n+3) такта от начала загрузки матрицы ска- 2g ляр ного умножит еля компонентами т ек,)тщего вектора ее первую строку можно загружать компонентами следующего вектора. Организация загрузки волной" дает при массовой загрузке векторами экономию во времени на (и+3) такта по сравнению с параллельной загрузкой

„ матрицы.

Двухрядный код, полученный в ма/ рице, с информационных выходов последней30

m-й строки обрабатывают в блоке суммирования следующим образом.

Первый и четвертый информационные выходы S-х ($=1 (и+1с+1) ) Вычислитель%

35 ных элементов r-й (г=тп) строки соединены с входами S -х (S =1, (2n+k+ I)) соответствующих сумматоров 8 блока суммирования так, что второй и чет вертый,информационные выходы S-х($=1,п}4 вычислительных элементов подключе"

/ ны к первым и вторым входам S -х (S

=-1,n) сумматоров 8 блока суммирования связями 60-62 и 62-68, а первый и третий HHAopMM OHHbie ВыхОды $-х (S=2 45 (п+1с+1)) вычислительных элементов под1 кл>сваны к первым н втерев> входам S -х (S =(и+1), (2n+k+1)) сумматоров 8 Опека суммирования связями 27 — 35 и 61-68.

Каждому разряду двухрядного кода частичных произведений, которые накоплены построчным суммированием r-х частичных произведений в (n+k+1): — ì вычислительном элементе каждой r -й (r=1,m) строки матрицы, соответствует свой сумматор уже в (2n+k+1) — м разрядном

55 сумматоре 8 блока 3 суммирования.

Сумматор 8 блока суммирования работает следующим образом.

Па такте, в первый и второй

I а триггеры первого яруса $ — х ($ =1,п) вычислительных элементов по первому

67 и второму 68 входам сумматоров зались/вают значения двухрядного кода из тп-й строки матрицы вычислительных элементов, а в третий по входу 69 значение переноса с выхода 71 комбинационного сумматора второго яруса ( ($ -1)-ro вычислительного элемента значение результата и переноса, кото! /" рОе выработано в $-м (S =1,п и S=

=1, (и-1) соответственно) комбинационном сумматоре первого яруса на тактовом сигнале (, записывают в триггеры втоZ рого яруса: в первый S- го сумматора, 1 во второй ($ +1) — го по иннам связи с второго 72 с S-го выхода S-ro сум I матора на четвертый вход 70 ($+1)-ro сумматора соответственно, в третий переписывают значение триггера результата S-ro сумматора.

На "àêòå /, в первый и второй

2.

/ / триггеры первого яруса S -х ($ =-(и+1), (2n+k+1) ) в>мнсл>ттельнв>х влементон по первому 67 и второму 68 входам сумматоров записывают значение двухрядного кода из ш строки матрицы .Вычислительных элементов, а в третий по входу 69 — значение переноса с выхода

71 сумматоров второго яруса (S -1) вычислительного элемента . Значение ре/ (зультата и переноса в S -м (S =(и+1), >> ° =>\,Г> ветственно) сумматоре первого яруса на тактовом импульсе /,/ записывают в л триггеры второго яруса: в первый $-ro

1 сумматора, во второй (S +1)-го по шинам связи с второго выхода 72 S-го

/ сумматора на четвертый вход 38 (S +

+1)-ro сумматора соответственно, в третий переписывают значение тригге/ ра результата S -го разрядного сумматора.

Предлагаемая структура блока суммирования и его связей в два раза ускоряет передачу переносов из первого разряда блока суммирования в (2n+

+k+1) сумматор, так как сложение производят одновременно во всех младших (1+n) и старших (и+1) -(2n+k+1) сумматорах на каждом втором сигнале..

Время t передачи переносов из млад3

mего в старший (2n+k+1)-й разряд рав(2n+1ñ+1) но t = — — — —. А общее время Т ска2 лярного произведения двух векторов А и В размерности m=n раВно T=t /+t q+t 9

19 1619254 20

=(3/и+1)+2+k/2), где k=lop

=(2п+с+1):2 до t =(2п+1):2=(n+1) так-15

3 тов время вычисления скалярного про9 изведения до T=t +t +t =(Зп+6) =

4 2

=-3(п+2), а загрузку компонент. векторов следующего скалярного произведения можно. начинать при организации загрузки матрицы "волной" через (n+3} такта.

Если описанного скругления с (k+1)-ro разряда не производить, то при параллельной загрузке матрицы 25 компоненты векторов следующего скалярного произведения можно вводить через (2n+k/2) тактов, а при загрузке "волнои" через (n+k/2+3/2) тактов, когда тп=п+1 . ЗО

Ускорение загрузки до (n+1) -го такта возможно за счет сквозного параллельного переноса по всей разрядной сетке блока суммирования путем группового параллельного. переноса при разбивке разрядной сетки блока суммирования на группы.

Результат обработки в блоке 3 суммирования двухразрядного кода фиксируют на третьих 73 выходах (2n+k+1) разрядного сумматора. Он равен результату скалярного умножения двух векторов, где произведение и каждая из компонент его представлены (и+1) разрядным числом в дополнительном коде.

Выходы 73 старгФх (2п+1} разрядов блока суммирования подключены к (2n+1) информационному входу мультнплексо" ра 4, адресные входы которых соответственно подключены к (2п+1) выходу " блока 5 управления. Поэтому при развертке адресов мультиплексора с его выхода последовательно разряд эа раз" рядом выводят значения результата суммирования B различных вариантах, требуемых по алгоритму — все (?n+1) разряд, начиная со старшего младшего или знакового, только старшие (n+1) разряд

H T ° Д °

При умножении матриц большой размерности целесообразно испольэовать и младшие разряды, т. е. все (Zn+k+1) разрядов результата. При этом в мультиплексоре 4 могут быть добавлены К информационных и соответствующих им адресных входов.

Введение блока преобразования кода, узла установки регистра узла управления, которые объединены в блок ввода для каждой строки матрицы вычислительных элементов обеспечивает реализацию алгоритма умножения чисел, представленных дополнительным кодом. Если числа сомножители представлены в скалярный умножитель в виде, удобном для умножения, т.е. множитель положительный, а множимое в обратном или даже в дополнительном коде с учетом преобразования кода множителя, то блок преобразо