Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к sa-i помянакпцим устройствам с ограниченным доступом, и может быть использовано в процессорах обработки изображений Цель изобретения - расширение функциональных возь5ожностей устройства, за счет обеспечения доступа к пакятн T trra первым зяписан - первым сплты - вается „ Устройство содержит элементы IT 7-12, элементы ИЛИ 13-16, счетчики 17 и 18, блоки 19 и 20 памяти. В устройстве также обеспечивается доступ к памяти типа первым записанпервым считывается. 1 ил,

сооэ советсних социАлистичесних

РЕСПУБЛИК

С-1 1

net 4/ ж> (".1)5 С 06 Г 1:/00 - :-.-:: "03846 !t6 tCUt4 с ОТЕНД

ГОСУДАРСТВЕННЫЙ КОМИТЕТ по изсыРетьниям и отнРьгиям пРи п нт сса (21) 3970826/24 (22) 11.09.85 (46) 07.01.91. Вил. Р 1 (72) А.Н,Афанасьев, В.И.Златкис, I0.À.Òeïòèí и И.И.Калин (53) 681.327(088.8) (56) Патент Японии Р 56-40379, кл. 97(7) С, опублик. 1981.

Патент Великобритании Р 2086623, кл. С 4 А, опублнх. 198 ?.

I (54) ЗАПОИИНАИЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с ограниченным доступом, и может быть испольэовгжо в процессорах обработки изображений.

Цель изобретения — расширение функциональных возможностей устройства.. эа счет обеспечения доступа к памяlt ти типа первым записан — первым сняты"

tt вается. Устройство содержит элементы

И 7-12, элементы Ш1И 13-16, счетчики 17 и 18 блоки 19 и 20 памяти.

В устройстве также обеспечивается

t1 доступ к пгчятя тяпа первым запнсан-! первым считывается". 1 ил.

1619282

Изобретение относится к вычислительной технике, в частности к зало- . мннаюцим устройствам с ограниченньгf доступом, и может быть использовано в процессорах обработки изображений.

Цель изобретения — рась«ирение фун-. кциона ьных возможностей устройства путем обеспечения доступа к памяти типа первым записа«i — первым считыва-.t

It

l0 ется

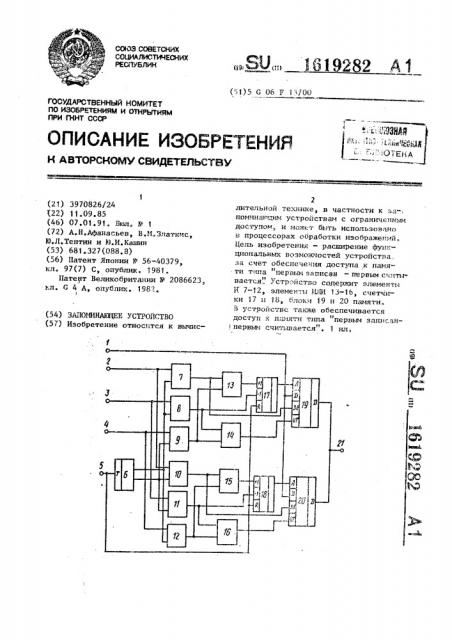

На чертеже изображена структурная схема запоминающего устройства.

На схеме позициями 1-5 обозначены соответственно информац««энный вход устро«.стна, вход Запись текуцего блока данных", вход "Чтение текуцего блока данных", вход "Чтение предьдуцего блока данн .х" и вход Конец блока данных". Устройство содержит триггер 6, первую группу элементов

И 7-9, вторую группу э.чементов И 1012, первую группу элементов ИЛИ 13 и 14, вторую группу элементов ИЛИ 15 и 16, первый 17 и второй 18 счетчики, первый 19 н второй 20 блоки памяти. Устройство имеет информационный выход 21.

Устройство работает следующим образом.

Допустим, в исходном состоян« и триггер 6 находится н состоянии О. В этом слу чае запись данньгс, поступающих с выхода 1, происходит во второй блок 20 по сиг налу "запись текуцего блока данных".

Сигнал Запись текущего блока дан11

35 ных" поступает с входа 2 на нторой блок 20 через элемент И 10. После окончания цикла записи сигнал "Запись теку« его блока данных" через элемент 40

ИЛИ 15 увеличивает содержимое второго счетчика 18, ныполняюцего функцию адресного регистра блока 20, на един.щу. Таким образом, запись следующего элемента данных будет про«зво45 диться в следуюцую ячейку блока 20.

Сигнал "Чтение текущего блока данных" с входа 3 через элемент И 1 1 поступает на вход счетчика 18, уменьшая его содержимое на единицу. Сигнал

"Чтение текуцего блока данных" через элемент ИЛИ 16 поступает на вход второго блока 20 памяти, с выхода которого данные поступают на выход 21 устройства. Таким образом осуцестнляется счить«нание последнего записан. ного элемента данных.

Сигнал "Чтение предьщуцего блока д..нши" с входа 4 поступает на вход первого блока 19 . памяти через элемент И 9 и элемент KIH 14, После окончания цикла "Чтение" сигнал "Чтение предыдуцего блока данных" через элемент KIN 13 поступает ««а вход первого счетчика 17, увеличивая его содержииое на единицу. Первый счетчик 17 ны:.олняет функцию адресного регистра первого блока 19 памяти. Таким обра-. зом, считывание следуюцего элемента данных будет производиться из следуюцей ячейки пыщти. Данные с выхода первого блока 19 памяти поступают на выход 21 устройства. Сигнал "Конец блока данных" с входа 5 поступает на входы счетчиков 17 и 18, обнуляя их, и на вход триггера б, перебрасывая его в противоположное состояние.

При прохождении следующего блока данных сигнал "Запись текущего блока

II данных через элемент И 7 и элемент

ИЛИ 13 будет управлять первым счетчиком 17 и первым блоком 19 памяти.

Сигнал "Чтение текуцего блока данных" через элемент И 8 и элемент ИЛИ 14 будет управлять первым счетчиком 17 и первым блоком 19 памяти. Сигнал

It

Чтение предьщуцего блока данных через элемент И 12, элементы ИЛИ 15 и 16.будет управлять вторым счетчи-:: ком 18 и вторым блоком 20 памяти, считывая элементы данных н порядке . их записи н течение предьщуцего блока данных.

Таким образом, н запоминаюцем устройстве реализуются дна способа дос-.. тупа к памяти: "первым записан — первым считывается" и "последним записан — первым считывается".

I формула изîбрeтения

Запоминаюцее устройство, содеРжащее первый и второй блоки памяти, информационные входы которых объединены и являются информационным входом устройства, . выходы объединены и являются информационным выходом устройства, триггер, счетный вход которого является входом "Конец блоisa данных" устройства, первую и вторую группы элементов И, первую и вторую группы элементов ИЛИ, первый и второй счетчики, о т л и ч а ю щ е— е с я тем, что, с целью расщирения функциональных возможностей устройства путем обеспечения доступа к памяти типа "первым записан — первым

161

Составитель В. Рудаков

Техред п.Сердюкова Корректор 0-Кравцова

Редактор Н.Тупица

Заказ 49 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям н открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент". г.ужгород, ул. Гагарина,10!

5 считывается™, в устройстве первые входы первых, вторых и третьих элементов И первой и второй групп соответственно объединены и являются входами "Запись текущего блока данных", "Чтение текущего блока данных" и "Чтение предыдущего блока данных устройства, вторые входы первого и второго элементов И первой группы и третьего элемента И второй группы соединены с прямык выходом триггера, инверсный выход которого соединен с вторыми входами третьего элемента И первой группы и первого и второго элементов И второй группы, выход первого элемента И каждой группы подключен к входу "Запись" соответствующего блока памяти и первому входу

9282 6 первого элемента ИЛИ соответствующей группы, выход которого подключен к

1 суииируюцему входу сос,тветствующего счетчика, выход которогр соединен с адресным входом соответствующего блока памяти, выход второго элемента

И каждой группы подключен к вычитающему входу соответствующего счетчика и первому входу второго элемсн та ИЛИ соответствующей группы, выход которого соединен с входом "Чтение". соответствующего блока памяти, выход третьего элемента И каждой группы соединен с вторыми входами элементов ИЛИ соответствующей группы, установочные входы счетчиков соединены с входом "Конец блока данных" устройства.