Устройство для сопряжения двух магистралей

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСН ИХ

ЩСГ1УБЛИН

ЦЕЬ 01Ь (51) 5 С 06 F 13/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И OTHPbtYHAM

ПРИ ГННГ QCCP

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4419136/24 (22) 03.05.88 (46) 07. 01, 91. 3; Ь (72) Л.П.Дубровский, И.С.Любчанский, Е.А.Песляк и В.И.Таратухин (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 1283781, кл. С 06 F 13/14, 1985.

Авторское снидетельстно СССР

h> 1545225, кл. С 06 Г 13/14, 25.04.88. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ИАГИСТРАЛЕЙ. (57) Изобретение относится к вычислительной технике и может быть использовано в многоканальных (многопроцессорных) системах для получения доступа к общему разделяемому ресурсу, например памяти для магистралей, в протоколах обмена которых предусмотрен сигнал "Ответ синхронизации по адресу". Целью изобретения является сокращение аппаратурных затрат устройства и повышение надежности иаботы путем сокращения. числа соединение шинно-организованных сзяэей и нем, а также уменьшение оборудования. Цель достигается тем, что в устройство введены пять элементов

И, элементов 11ЛИ и элемент адержки.

На информационные входы основных триггеров, обеспечивающих предоставление совмещенной магистрали, поПает. ся сигнал запроса соответствующей магистрали через элементы И при по" явлении сигнала "Синхронизация обме2 на" в данной магистрали. В соответствии со случайным приоритетом один из триггеров срабатывает по фронту тактового импульса (соответствено прямого или инверсного на его синхровходе)

Р и обеспечивает подключение выбранной магистрали через коммутаторы к совмещаемому ресурсу. Однонременно подается сигнал разрешения на введенные элементы И соответствующей магистрали. Дешифратор эоны, подключенный к совмещенной магистрали, через регистр адреса фиксирует наличие адреса данного разделяемого ресурса в текущем полупериоде частоты следования тактового импульса, подтверждает запрос на все время обращения магистрали к разделяемому ресурсу. При этом sa" прещается по входу сброса срабатывание основного триггера второй магистрали. В случае неподтнерждения соответствия адреса обращения данной ф магистрали адресному пространству, данног ресурса в следующем же полую периоде частоты следования тактового импульса нзводится дополнительный триггер и з;.прещается им подключение сигнала запроса от этой магистрали. Ж

Основной триггер сбрасывается,ос- Ю вобождая совмещенную магистраль по QO крайней мере до следующего обраще- Ql ння этой же магистрали с новым. за.просом, так как первый запрос- бып обращением по адресу другого ресурса, с которым эта магистраль продолжает протокол обмена. 1 ил. Зь

1619285

Изобретение относится к вычислительной технике и может быть использовано в многоканальных (многопроцессорных) системах для получения досту5 па к общему разделяемому ресурсу магистралей, в протоколах обмена которых предусмотрен сигнал "Ответ синхронизации по адресу".

Пель изобретения — сокращение аппаратурных затрат.

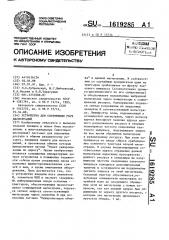

На чертеже представлена блок-схема устройства.

Устройство содержит блок 1 памяти, коммутаторы 2 и 3 магистралей, регистр 4 адреса, дешифратор 5 зо ны, первый 6, третий 7, пятый 8, второй 9, четвертый 10 и шестой 11 элементы И, элемент 12 задержки,третий элемент ИЛИ 13, десятый 14, седь- g0 мой 15, восьмой 16, одиннадцатый 17, четырнадцатый 18, девятый 19, двенадцатый 20 и тринадцатый 21 элементы И, второй 22 и первый 23 элементы

ИЛИ, элемент HF. ?4, генератор 25 импульсов, третий 26, четвертый 27, первый 28 и второй 29 триггеры, адресно-информационные шины магистра лей 30 и 31, пины 32 и 33 чтения, шины 34 и 35 записи, пины 36 и 37 син,хронизации ответа, пины 38 и 39 синхронизации, шины 40 и 41 синхронизации ответа по адресу первой и второй магистралей.

Устройство работает следующим об35 разом.

Каждая из магистралей 30 и 31 обращается к совмещенной магистрали, к которой подключен блок 1 памяти— разделяемый магистралями ресурс. При 40 этом на входы коммутаторов 2 и 3 со стороны магистралей подаются адреса блока 1 памяти, а по шинам 38 и 39 магистралей сигнал "Синхронизация".

При этом снимается сигнал сброса с триггеров 28 и 29 благодаря инверсному входу элемента ИЛИ 22.

Сигнал "Синхронизация" с шин 38 и

39 поступает на инверсные входы сброса триггеров 26 и 27 соотвественно, О позволяя им устанавливаться в состояние логической "1" при поступлении синхросигнала, так как на информационные входы триггеров 26 и 27 подан разрешающий потенциал. Сигнал "Синхронизация" на шинах 38 и 39 свидетельствует о наличии запроса от магистрали. Он подается на информационный вход соответственно триггера 28 илн 29 через элементы И 20 и 21 благо даря сигналу разрешения с инверсного выхода триггеров 26 и 27, сброшенных в исходное состояние. Тактовые импульсы с выхода генератора 25 поступают на синхровход триггера 28, а с выхода элемента НЕ 24 — на синхровход: триггера ?9 и устанавливает один из этих триггеров в разрешенное состояние. !

При этом, так как выход каждого из триггеров 28 и ?9 подключен к входу сброса другого через элементы

ИЛИ 22 и 23 соответственно, установка друг ого триггера запрещается до сброса установленного триггера. При одновременном запросе приоритет магистралей случайный и зависит от того, на какой синхровход раньше придет устанавливающий фронт синхросигнала„ а они приходят в противофазе.

Предположим взводится триггер 28 (29). В этом случае сигнал с выхода триггера 28 (29) поступает на вход элемента И 14 (17), на другом входе которого имеется разрешающий потенциал с шины 38 .(39) " Синхронизация" магистрали.Сигнал разрешения с выхода элемента И 14(17) разрешает передачу с магистрали 30 (31) адреса блока 1паI мяти в совмещенную магистраль через коммутаторы ? (3) . С выхода элемента

И 14 (17) сигнал поступает также через элемент ИЛИ 13 и элемент 12 задержки на синхровход регистра 4 адреcan записывает корректное значение адреса, обеспечиваемое на входе регистра 4 адреса благодаря элементу 12 задержки, величина которой выбирается достаточной для срабатывания коммутаторов 2 (3). Записанный адрес с выхода регистра 4 адреса поступает на адресные входы блока 1 памяти дешифратора 5 зоны. Если адрес в регистре 4 соответствует блоку 1 памяти, то на выходе дешифратора 5 зоны появляется выходной сигнал выборки, так как на управляющем входе дешифратора 5 также имеется сигнал разрешения. Сигнал выборки поступает на входы элементов И 15 (18). Так как с выхода триггера 28 (29) имеется 1 разрешение на входах элемента И 15 (16), то на шине 40 (41) "Ответ синхронизации по адресу" соответствующей магистрали появляется сигнал,сообщающий магистрали, что она может продолжить цикл обмена. Одновременно сигнал с выхода элемента И 15 (18) Если при предоставлении разделяемого ресурса для одной из магистралей не формируется с выхода дешиЬратора 5 зоны сигнал выборки, то это означает, что обращение магистрали осуществляется к другому ресурсу. В этом случае к следующему полупериоду частоты следования сигнала тактового генератора 25, относительно переднего фронта которого на синхровходе триггера 28 (29) установился разрешающий сигнал предоставления магистрали, не поступает сигнал запрета на инверсные входы элемента И 16 (19), а потому сигнал с выхода элемента

НЕ 24 проходит через элемент И 16 элемент ИЛИ 22 и сбросится в "О" триггер 28, освобождая магистраль.

При этом повторное предоставление совмещенного ресурса этой магистрали не осуществляется, так как триггер

26 (27) устанавливается по синхровходу с выхода элемента 16 (19) и запрещает прохождение сигнала запроса через элемент И ?0 (21) на информационный вход триггера 28 (29).

Вновь совмещенный ресурс может быть предоставлен этой же магистрали только по новому запросу, так как триггер 26 (27) будет сброшен в исходное состояние только при снятии сигнала с нины 38 (39) "Синхронизация °

При предоставлении совмещенной магистрали для одной иэ запрашивавших принимается решение о соответствии запрошенного ресурса данному. Если имеет место несоответствие, то, как описано выше, через элементы И 16 (19), элементы ИЛИ 22 (23) осуществляется сброс триггера 28 (29). Однако тактовый сигнал, который сбрасывает триггер 28 (29), подается и на синхровход триггера 29 (28). В то же время выход триггера 28 (29) подключен на вход сброса триггера 29 (28), поэтому в связи с задержками в цепях связей установ триггера 29 (28) не произойдет, пока триггер 28 (?9) не сбросится. В связи с этим предоставление совмещенной магистрали второй магистрали может произойти с задержкой, т.е. при следующем тактовом сигнале на входе триггера 29 (28).

Для уменьшения времени ожидания следует в цепь синхровхода триггера

29 (28) ввести элемент задержки (не показан) на время, достаточное для

5 1619285 поступает также на один из входов элемента И 16 (19), запрещая его срабатывание и одновременно разрешая работу элементов И 6-8 (9-11) дпя выбранной магистрали с блоком 1 памяти.

Тактовая частота генератора 25 выбирается такой, чтобы за полупериод частоты ее следования сигнал с выхода триггера 28 (29) успел к началу следующего инверсного полупериода запретить срабатывание элементов

И 16 (19), т ° е. полупериод должен быть больше задержки в цепи: триггер 28 (29), элемент И 14 (17), коммутаторы 2 (3), регистр 4 адреса, дешифратор 5 зоны, элемент И 15 (18).

Магистраль, владеющая совмещаемим ресурсом, осуществляет операцию обмена с памятью. Выставляет на шину 20

32 (33) или 34 (35) сигналы управления направлением работы коммутатора

Ъ

2 (3). В случае операции "Чтение" на шину 32 (33) магистраль подает сигнал и ожидает поступления инФор- 25 мации из блока 1 и сигнала ответа синхронизации на шине 36 (37), свидетельствующего о выдаче достоверной информации. В случае операции "Запись" магистраль вначале выставляет данные, сопровождает их сигналом на шинах 34 (35) и ожидает сигнала ответа синхронизации на шине 36 (37), свидетельствующего об окончании записи информации. По сигналам "Ответ синхронизации" магистраль снимает сигналы управления, в том числе и сигнал с шины 38 (39) синхронизации, т.е. запрос. В этом случае триггер

28 (29) сбрасывается в исходное состояние через элемент ИЛИ 22 (23) . 40 по входу сброса.

На входе элементов И 14 (17), 15 (18), 16 (19) снимается разрешающий потенциал, поэтому снимается разрешающий сигнал с выхода дешиАратора 45

5 зоны и сигнал с входов управления коммутатором 2 (3). Запрещается работа элементов И 6-8 (9-11). При появлении на выходе элемента И t5 (18) разрешающего сигнала для элементов И 16 (19).и появлении или наличии в этот момент разрешающего сигнала на входе элемента И 16 (19) с элемента НЕ 24 (для элемента И 19 — с .вьпсода генератора 25) сигнал на вы- 55 ходе элемента И 16 (19) не появляется, так как с их первых входов уже снят разрешающий потенциал с вьхода триггера 28 (29).

1619285

8 установления триггера 28 (29) в исходное состояние. В этом случае предоставление совмещенной магистрали при наличии запроса от второй магистрали произойдет только с указанной задержкой, а не при следующем тактовом импульсе.

Формула изобретения.10

Устройство для сопряжения двух магистрапей, содержащее блок памяти, информационный вход-выход которого подключен к первым информационным входа 1-выходам первого и RTopol o ком- 15 мутаторов магистралей, вторые информационные входы-выходы которых являются соответструющими входами-выходами устройства дпя подключения к адресно-информационным шинам первой и второй магистралей, регистр адреса, соединенный выходом с информационным входом дешифратора зоны, девять элементов И, два элемента ИЛИ, четыре триггера, генератор импульсов H элемент HF. причем выходы первого и второго элементов И объединены монтажным

ИЛИ и соединены с входом чтения блока памяти, а первые входы являются соответствующими входами устройства для подключения к шинам чтения первой и второй магистралей и соединены

30 соответственно с первыми входами напразления обмена первого и второго иены соответственно с первыми входами 40 третьего и четвертого элементов И, выходами объединенных монтажрым ИЛИ и подключенных к входу записи блока памяти, синхронизирующий выход ответа которого подключен к первым входам пятого и шестого элементов И,выходы которых являются соответствующими выходами устройства для подключения к шинам синхронизации ответа первой и второй магистралей, первый вход седьмого элемента И соединен с выходом дешифратопа зоны, первые входы и выходы. первого и второго

50 элементов ИЛИ соединены соответственно с выходами первого и второго триггеров и входами сброса второго и первого триггеров, синхровходы которых соединены соответственно с выходами генератора импульсоп и элемента НЕ, коммутаторов м гистралей, вторые вхо 3 цы направления обмена которых являются соответствующими входами ус гройства для подключения к шинам записи первой и второй магистралей и соедиподключенного входом к выходу генератора импульсов, а выходом — к первому входч восьмого элемента Р, синхровходы третьего и четвертого триггеров соединены соответственно с выходами восьмого и девятого элементов И, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат устройства,в него введены пять элементов И,третий элемент ИЛИ

Ъ и элемент задержки, причем первый и второй входы третьего элемента ИЛИ соединены соответственно с выходами десятого и одиннадцатого элементов И, а выход — через элемент задержки с синхронизирующими входами дешифратора зоны и регистра адреса, выходом и информационным входом подключенного соответственно к адресному входу блока памяти и первым информационным входам-выходам первого и второго коммутаторов магистралей, входы выборки которых соединены соответственно с выходами десятого и одиннадцатого элементов И, информационные входы первого и второго триггеров подключены соответственно к выходам двенадцатого и тринадцатого элементов И, первыми входами соединенных соответственно с выходами третьего и четвертого триггеров, входы сброса которых являются соответствующими входами устройства для подключения к шинам синхронизации первой и второй магистралей и соединены соответственно с первыми входами десятого и одиннадцатого элементов И и вторыми входами двенадцатого и тринадцатого элементов И,второго и первого элементов ИЛИ, третий вход второго элемента ИЛИ соединен с выходом восьмого элемента И, вто. рым входом подключенного к вторым входам седьмого и девятого элементов И, выход седьмого элемента И соединен с третьим входом восьмого элемента И и вторыми входами первого, третьего и пятого элемент.)в И и является выходом устройства для подключения к шине синхронизации ответа по адресу первой магистрали, выход дешифратора зоны соединен с первым входом четырнадцатьro элемента И, второй вход которого подключен к выходу второго триггера и вторым входам одиннадцатого и девятого элементов И, третьим входом соединенного с выходом генератора импульсов, третий вход первого элемента ИЛИ соединен с выходом девя1б1о285

Составитель В. Вертлиб

Редактор Н.Тупица Техред Ц. Сердюкова Корректор Н. Король,Заказ 49 Тираж Подписное

ВНИИИИ 1 ocyдap«твeнноrо комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101 того элемента И, третий вход которого соединен с вторыми входами второго четвертого и шестого элементов И и выходом четырнадцатого элемента И, выход которого является выходом устройства для подключения к шине синхронизации ответа по адресу второй магистрали.