Устройство для сопряжения двух магистралей

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многоканальных (многопроцессорных ) системах для получения доступа к общему разделяемому ресурсу магистралей, в протоколах обмена которых предусмотрен сигнал Ответ синхронизации по адресу. Целью изобретения является сокращение аппаратурных затрат и повышение достоверности работы устройства путем уменьшения числа соединений в нем шинноорганизованных связей. Цель достигается введением в устройство, содержащее блок памяти, четыре триггера, два коммутатора магистралей, два дешифратора зоны, регистр адреса, генератор импульсов, элемент НЕ, элемент ИЛИ и девять элементов И, десятого элемента И и элемента задержки. 1 ил.

сооз советских социАлистичесн их

РЕСПУБЛИК (g1)g G 06 F 13/14

b la i„ йй, Я""!

Б;-1Б й

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ пО иЗОБРетениям и ОтнРытиям

ПРИ ГКНТ СССР

1 (21) 4420167/24 (22) 03.05.88 (46) 07.01.91. Бюл. № 1 (72) Л.Б.Дубровский, М.С.Любчанский, Е.А.Песляк и В.И.Таратухин (53) 681.325(088.8) (56) Авторское свидетельство СССР № 1283781, кл. G 06 Р 13/14, 1985.

Авторское свидетельство СССР

¹ 1545225, G 06 F 13/14, 25,04,88. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖКНИЯ

ДВУХ МАГИСТРАЛЕИ (57) Изобретение относится к вычислительной технике и может быть использовано в многоканальных (многоИзобретение относится к вычислительной технике и может быть использо- вано в многоканальных (многопроцессорных) системах для получения доступа к обцему разделяемому ресурсу магистралей, в протоколах обмена которых предусмотрен сигнал "Ответ синхронизации по адресу

Цель изобретения — сокраце»»ие аппаратурных затрат устройства.

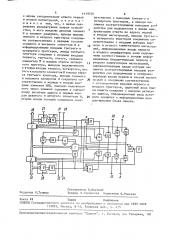

На чертеже представлена блок-схема устройства.

Устройство содержит блок 1 памяти, коммутаторы 2 и 3 магитралей, регистр 4 адреса, шины 5,и 6 ответа синхронизации по адресу, дешифраторы 7 и 8 зон, генератор 9 импульсов, третий 10, четвертый 11, первый 12 и второй 13 триггеры, первый 14, третий 15, пятьпr 16, второй 17, четвертый 18 и шестой 19 элементы И, эле„„SU„„1619286 А 1

2 процессорных) системах для получения доступа к обшему разделяемому ресурсу магистралей, в протоколах обмена которых предусмотрен сигнал "Ответ синхронизации по адресу". Целью изобретения является сокрацение аппаратурных затрат и повышение достоверности работы устройства путем уменьшения числа соединений в нем шинноорганизованных связей. Цель достигается введением в устройство, содержашее блок памяти, четыре триггера, два коммутатора магистралей, два дешифратора зоны, регистр адреса, генератор импульсов, элемент ИЕ, элемент

ИЛИ и девять элементов И, десятого элемента И и элемента задержки. 1 ил.

I мент НЕ 20, шины 21 и 22 чтения, шины 23 и 24 записи, адресно-информационные шины первой 25 и второй 26 магистралей, шины 27 и 28 синхронизации, BIHHbl 29 H 30 синхронизации ответа первой и второй магистралей, седьмой 31 и восьмой 32 элементы И, элемент ИЛИ ЗЗ, элемент 34 задержки, девятьп» 35 и десятый 36 элементы И, узлы 37 и 38 выбора банка.

Устройство работает следуюцим образом.

Во ьремя функционирования обоих устройств в узлы 37 и 38 выбора ба»»ка на входы дешифраторов 7 и 8 зоны поступают разряды адресов, определяюцих обрацение к блоку 1 памяти. В момент обрашения к данному блоку 1 по сигналам Синхронизация" на шинах 27 и 28 триггеры 12 и !3 устанавливаются в разрешенное состояние, 1619286 соответствугоцее запросу от данной магистрали, и удерживают этот запрос на входе соответствующего триггера

10 или 11.

Срабатывание триггеров 10 и 11 происходит по фронту импульса, поступающего с выхода генератора 9 и элемента HE 20 соответственно. При срабатывании одного из указанных триггеров срабатывание другого запрещается до установки в исходное состояние первого сработавшего триггера. Он устанавливается в исходное состояние после снятия сигнала с 15 соответствующего выхода триггера 12 (13). Приоритет устройств случайный.

Одновременное срабатывание триггеров невозможно.

В момент срабатывания, например, триггера 10(11) открываются коммутаторы 2(3). При этом коммутаторы 2(3) работают на передачу информации в совмещенную глагистраль. Поэтому адрес, который продолжает удерживаться в 25 магистрали 25, поступает на вход регистра 4 адреса.

Сигнал с выхода триггера 10(11) поступает также на входы элементов

И 14(17), 15(18),16(19), 35(36), 30

31 (32) и на вход сброса триггера 11 (10) .

На выходе элемента И 31(32) появляется сигнал, так как на его обоих входах имеется разрешающий потенциал.

Этот сигнал через элемент ИЛИ 33 и элемент 34 задержки поступает в качестве синхросигнала на вход регистра 4. Так как к этому моменту благодаря элементу 34 задержки устанавливается корректное значение адреса, 40 он и будет зафиксирован в регистре 4 и подан на адресные входы блока 1 памяти. Одновременно сигнал с выхода элемента 34 задержки поступает на входы, элементов И 35 и 36 и да- 45 лее на шины 5 и 6 "Синхронизация ответа по адресу". Тогда по магистра- ли 25(26) устройство, владеющее магистралью, посылает информацию и со-. провождает ее сигналом "Запись" нли выдает только сигнал Чтение и ощидаи гг ет поступления информации из блока 1 памяти.

Указанными сигналами определяется

55 а в блок 1 памяти он поступает через элементы И 14(17) и 15(18). Информация поступает на информационные входы блока 1 памяти, а окончание цикла обмена сопровождается подачей из блока 1 памяти сигнала ответа синхронизации на входы элементов И 16(19), а с них — на шины 29(30) .

В предлагаемом устройстве вся адресная информация, за исклкчением, разрядов выбора банка, передается по совмещенной магистрали, отсутствует коммутация многоразрядного адреса на адресных входах блока 1 памя-. ти, обеспечиваются требования обмена между магистралями н блоком 1 памят.и. формула изобретения

Устройство для сопряжения двух магистралей, содержащее блок пагляти, информационным Входом-Выходом соединенный с первыми информационными входами-выходами первого и второго коммутаторов магистралей, вторые информационные входы-выходы которых являются соответствующими входами-Выходами устройства для подключения к адресно-информационным шинам первой и второй магистралей, регистр адреса, два деыифратора зоны, Выходами соединенные соответственно с входами сброса первого и второго триггеров, третий триггер, синхровходом соединенный через элемент НБ с синхровходогл четвертого триггера и выходом генератора импульсов, элемент ИЛИ и девять элементов И, причем вход записи блока памяти подключен к объединенным ИОНТЛННИИ ИЛИ Выходам первого и второго элементов И, первые входы которых соединены соответственно с первыми Входамн направления обмена первого и второго коммутаторов магистралей и являются соответствующими входами устройства для подключения к шинам записи первой и втрой магистралей, вход чтения блока памяти соединен с объединенными МОНТАМНЫИ

ИЛИ выходами третьего и четвертого элементов И, первые Вхопы которых являются соответствующими Входагли усч ройства для подключения к шинам чтения первой и второй магистралей и соединены соответственно с вторь1ми входами направления обмена первого и второго коммутаторов магистралей, . выход синхронизации ответа блока па,мяти соединен с первыли входами пятого и шестого элементов И, выходы которых являются соответствуюцнми выходами устройства для подключения

Составитель В. Вер тлнб

Техред П.Ссрдскова Еорректор Н.Ревская

Редактор Н.Тупица

Заказ 49 Тираж Подписное

ЗЫИПИ Государственного ко.л:тета до изобретениям lf открытня1 при ГЕНТ СССР

113035, >1осква, Ж вЂ” З5, Раушсхая наб., ; . - /5

Производс гвенно-издательский комбинат "Патент", г. )ы арод, ул. Гагарина, 101

5 161920 к шинам синхронизации ответа первой и второй магистралей, о т л и ч а— ю ц е е с я тем, что, с целью сокращения аппаратурных затрат устройства, в него введены десятьп элемент

И и элемент задержки, причем выходы первого и второго триггеров соединены соответственно с первыми входами седьмого и восьмого элементов И и информационными входами третьего и четвертого триггеров, вь»ход третьего триггера соединен с вторыми входами первого, третьего, »ятого, седьмого элементов И и входом сброса четвертого триггера, выходом подключенного к в торым вход ам в торо ro, че тв е р то го, ше с того и восьмого элементов И н входу сброса третьего триггера, выходы седьмого и восьмого элементов И соединены со- 20 ответственно в первым и вторым входами элемента HJIII, выходом подключенного через элемент задержки к синхровходу регистра адреса и первым входам девятого и десятого элементов И, 25 вторые входы которых соединены соответственяо с выходами третьего и четвертого триггеров, а выходы являются соатветствующ»пчи вь»ходаии уст ройства для подключения к шинам син-, хропизации ответа по адресу первой и второй магистралей, выходы третьего и четвертого триггеров соединены соответственно с входами выборки первого и второго коммутаторов магпстралей, информационные входы первого и второго дешифраторов зоны подключены соответственно к вторым информационным входам-выходам первого и второго коммутаторов магистралей, синхронизирующие входы которых явлжотся соответствующими входаьа» устройства для подключения к синхронпзируюцим шинам первой и второй л»агис.», тр.»лей» н соед»»иены соответственно с установочными входами первого и второго триггеров, адресный вход блока памяти соединен с выходом регист- . ра адреса, информационньп вход которого соединен с информационным входом-выходом блока памяти.