Фотоприемная ячейка

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, к оптоэлектронным устройствам считывания и хранения оптической информации. Целью изобретения является повышение чувствительности ячейки и расширение ее функциональных возможностей,, Фотоприемная ячейка содержит дифференциальный усилитель , состоящий из усилительных 1, 2, нагрузочных 3, 4 и токостабилизи

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (st)s 0 11 С 11/42

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

flPH ГКНТ СССР (21) 4649355/24 (22) 10.02.89

; (46) 07.01.91. Бкп. N - 1 (71) Институт автоматики и электрометрии CO АН СССР (72) В.Е. Бутт, Б.Н. Панков, В.В„ Савельев и П.Е. Твердохлеб (53) 681.327.66(088.8) (56) Авторское свидетельство СССР й- 661608, кл. С 11 С 11/42, 1977.

Автометрия, 1977, М 2, с. 79-85„

ÄÄSUÄÄ 1619344 А1

2 (54) ФОТОПРИ1. ИНЛЯ ЯЧЕЙКА (57) Изобретение относится к вычислительной технике, к оптоэлектронным устройствам считывания и хранения оптической информации, Целью изобретения является повышение чувствительности ячейки и расширение ее функциональных возможностей. Фотоприемная ячейка содержит дифференциальньп усилитель, состоящий из усилительных 1, 2, нагрузочных 3, 4 и токостабилизи1619344

lp рующих 5 и 18 транзисторов,фотодиоды

7 и 8, подключенные к затворам усилительных транзисторов 1 и 2 и подложке

9, ключевые транзисторы стирания 10 и 11, затворы которых подключены к шине 12 стирания, стоки - к источнику

13 смещения фотодиодов, а истоки — к соответствующим затворам усилительных

Изобретение относится к вычислительной технике, а точнее к оптоэлектронике, и может быть использовано в устройствах для считывания и хранения оптической информации.

Цель изобретения - повышение чув.ствительности фотоприемной ячейки и расширение ее функциональных возможностей за счет обеспечения точности выполнения логико-арифметической об.работки информации в составе многоэлементной фотоприемной матрицы.

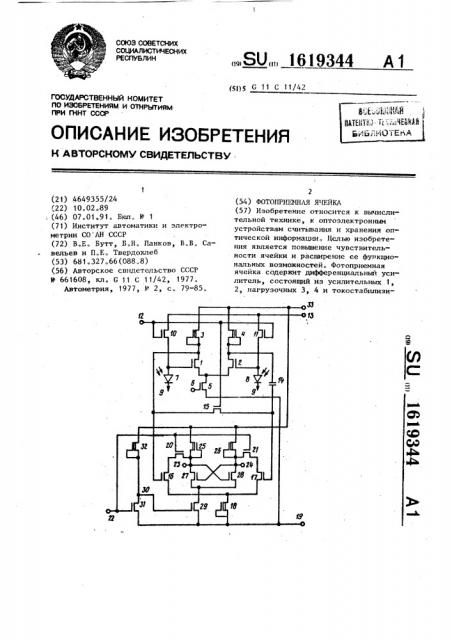

На чертеже преДставлена схема фотоприемной ячейки для дифференциального сравнения двух оптических сигналов.

Фоточувствительная ячейка содер- 30 жит первый и второй усилительные транзисторы 1 и 2, первый и второй нагрузочные транзисторы 3 и 4, hepвый токостабилизирующнй транзистор 5, шину 6 установки режима, фотодиоды 35

7 и 8, подложку 9 фотодиодов и транзисторов, ключевые транзисторы 10 и

11 стирания, шину 12 стирания, источник 13 смещения, запоминающий конден сатор 14, дополнительный транзистор 40

15 стирания, третий и четвертый усилительные транзисторы 16 и 17, второй токостабилизирующий транзистор 18, общую шину 19, первый и второй ключевые транзисторы 20 и 21 записи, шину 2245 записи, выходные шины 23 и 24 фотоприемной ячейки, третий и четвертый нагрузочные транзисторы 25 и 26, пя-. тый и шестой усилительные транзисторы

27 и 28, третий ключевой транзистоР 50

29 записи, инвертор 30, ключевой транзистор 31, пятый нагрузочный транзис тор 32, шину 33 питания. "

Усилительные транзисторы 1 и 2, на» груэочные транзисторы 3 и 4, токоста 5 билизирующий,транзистор 5, управляемый от задающей режим шины 6, образуют дифференциальный усилитель. Фотодиодй транзисторов 1 и 2. Новым в ячейке является использование дополнительного стробируемого дифференциального усилителя-компаратора (триггера-защелки) с цепочкой на входе иэ последовательно соединенных ключевого транзистора стирания и запоминающего конденсатора. 1 ил.

7 и 8 подключены к затворам усилительных транзисторов 1 и 2 и к подложке 9.

Затворы ключевых транзисторов 10 и 11 стирания подключены к шине 12 стирания, стоки - к источнику 13 смещения фотодиодов, а истоки — соответственно к затворам усилительных транзисторов

1 и 2. Между стоками усилительных транзисторов 1 и 2 включена цепочка, состоящая иэ последовательно соединенных запоминающего конденсатора 14 и дополнительного транзистора 15 стирания, затвор которого соединен с шиной

12 стирания. Сток и исток транзистора

15 подключены соответственно к затворам усилительных транзисторов 16 и

17 дополнительного дифференциального усилителя, являющегося составной частью триггера-защелки. Истоки транзисторов 16 и 17 дополнительного дифференциального усилителя соединены со стоком токостабилизирующего транзистора 18 этого усилителя, а затвор и исток токостабнлиэирующего транзистора 18 — с общей шиной 19. Стоки третьего и четвертого усилительных транзисторов 16 и 17 соединены соответственно с истоками ключевых транзисторов 20 и 21 записи, затворы которых подключены к шине 22 записи, а стоки, являющиеся выходами 23 и 24 дополнительного дифференциального усилителя и фоточувствительной ячейки (триггера-защелки), — соответственно к нагрузочным транзисторам 25 и 26 дополнительного дифференциального усилителя. Сток усилительного транзистора 27 и затвор усилительного транзис- тора 28 подключены к нагрузочному транзистору 25 (первому выходу 23 фоточувствительной ячейки), сток усилительного транзистора 28 и затвор уси лительного транзистора 27. подключены к нагрузочному транзистору 26 (второму выходу 24 фоточувствительной ячейки). Истоки усилительных транзисторов

1619344

27 и 28 соединены со стоком ключевого транзистора 29 записи, исток которогс подключен к общей шине 19, а затвор -1 к выходу инвертора 30 сигнала на шине 22 записи. Инвертор сигнала "=aписи содержит ключевой 31 и нагрузочный 32 транзисторы. Питание дифференциального усилителя, дополнительного дифференциального усилителя и инвер- 10 тора сигнала записи осуществляется от источника питания по шине 33.

Принцип работы фотоприемной ячейки состоит в следующем.

По сигналу стирания с шины 12 сти- 15 рания через открытые каналы ключевых транзисторов 10 и 11 стирания заряжаются до напряжения источника 13 смещения емкости фотодиодов 7 и 8. На выходах, дифференщ(ального усилителя

20 (стоках усилительных транзисторов 1 и 2) устанавливается при этом напряжение П„ы„ начального разбаланса этого усилителя, которое через открытый канал дополнительного транзистора

15 стирания подается на запоминающий конденсатор 14 и запоминается на его емкости.

По окончании сигнала стирапия каналы транзисторов 10, 11 и 15 запира- 30 ются. Фотодиоды 7 и 8 оказываются обратно смещенными зарядами, запасенными их емкостями во время стирания,а на емкости запоминающего конденсатора

14 сохраняется напряжение навьи, соот-35 вь о ветствующее начальному разбалансу диф-. ференциального усилителя. Это напря- . жение, суммируясь с выходным напряжением дифференциального усилителя (за счет последовательного соединения кон- 40 денсатора 14 с выходом этого усилителя), компенсирует на входах дополнительного дифференциального усилителя действие начального разбаланса. В результате на входах дополнительного . 45 дифференциального усилителя будет сигнал, соответствующий только полезному сигналу первого каскада.

Дополнительный дифференциальный усилитель, включающий третий и четвертый усилительные транзисторы 16 и

17, иагрузочиые транзисторы 25 и 26, включенные поспедовательно с ключевыми транзисторами 20 и 21 записи, образует вместе с дополнительными пятым и шестым усилительными транзисторами 27 и 28, инвертором на транзисторах 31 и 32 и транзистором записи 29 выходной каскад фотоприемной ячейки с функциями высокочувствительного компаратора с ячейкой памяти (триггеразащелки).

При отсутствии сигнала записи на шине 22 каналы ключевых транзисторов

20 и 21 записи заперты, а ключевой транзистор 29 — открыт (выходным сигналом с выхода 30 инвертора сигнала записи). При этом конфигурация, состоящая из транзисторов 27, 28, 25 и

26, образует статический триггер (транзистор 29 включает его питание), т.е. ячейку памяти с выходами 23 и 24.

На время действия сигнала записи питание этого триггера отключается (канал транзистора 29 запирается), зато при замкнутых каналах кл;очевых транзисторов 20 и 21 из транзисторов

16, 17, 20, 21 25, 26 и 18 образуется конфигураций дифференциального усилителя, который усиливает дифференциальный сигнал на его входах (затворах транзисторов 16 и 17). Усиленный сигнал запоминается на паразитньгх емкостях выходов 23 и 24. По заданному фронту сигнала стирания, когда каналы транзисторов 20 и 21 записи запираются, а канал транзисторов 29 открывается, происходит срабатывание триггера в соответствии со знаком напряжения, установившегося на его входах (выходах 23 и 24) перед концом сигнала записи. Таким образом производится компарирование сигнала дифференцижп ного усилителя с фотодиодами на входах, его нормирование по уровню и запись в триггер.

Отсутствие на входе дополнительного дифференциального усилителя начального разбаланса первого каскада повышает отношение сигнал/шум для ячейки в целом, а следовательно, увеличивает ее пороговую чувствительность. Применение в составе фотоприемной ячейки триггера-защелки предложенной конфигурации расширяет ее функциональные возможности. Это позволяет, использовать предложенную ячейку в качестве элементарной ячейки многоэлементной интегральной матрицы, способной выполнять в общем случае не только операции записи/чтения, но и многоканальную логико-арифметическую ооработку страниц цифровой оптической информации. Такие фотоматрицы (называемые фотоматричньми процессорами),при использовании в них в качестве элемен1619344

Составитель С. Самуцевич

Редактор В. Б гренкова Техред Л.Сердюкова Корректор И. Муска

Заказ 52 . Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r Ужгород, ул. Гагарина, 101 тарной ячейки предложенной конфигурации, обладающей высокой фоточувствительностью, помехоустойчивостью и расширенными. функциональными возможностями, обеспечивают высокие скорости выдачи и обработки потока цифровых данных, поступающих из оптической памяти.

1О

Формула изобретения

Фотоприемная ячейка, содержащая первый и второй усилительные транзис- тори, стоки которых подключены к истокам и затворам соответственно первого и второго нагрузочных транзисторов, стоки которых соединены с шиной литания, истоки первого и второго усилительных транзисторов соединены со стоком токостабилизируюцего транзистора, затвор которого подключен к управляющей шине, первый и второй фотодиоды, которые подключены к затворам соответственно первого н второго усилительных транзисторов и к подложке,. 25 первый и второй ключевые транзисторы стираниятистоки которых соединены соответственно с первым и вторым фотодиодами, а стоки подключены к источнику смещения фотодиодов, затворы первого и второго ключевых. транзисторов стирания соединены с.шиной стирания, о т л и ч .а ю щ а я с. я кем, что, с целью повышения чувствительности ячейки- и расширения. ее Функ циональных возможностей," в ячейку введены третнй ключевой транзистор стирания и запоминающий конденсатор, третий и четвертый нагрузочные транзисторы, первый, второй и третий клю-40 чевые транзисторы записи, третий и четвертый .усилительные транзисторы, второй токостабилизирующий транзистор, пятый и шестой усилительные транзисторы, ключевой транзистор и пятый 45 в нагруэочный транзистор, причем сток первого усилительного транзистора подключен к затвору третьего усилительного транзистора и к истоку третьего транзистора стирания, затвор которого подключен.к шине стирания, сток второго усилительного транзистора соединен через запоминающий конденсатор со стоком. третьего транзистора стирания и с затвором четвертогс усилительного транзистора,.истоки третьего и четвертого усилительных транзисторов соединены со стоками второго стабилизирующего транзистора,, затвор и исток которого подключены к общей шине, стоки третьего и четвертого усилительных транзисторов соединены соответственно к истокам первого и второго ключевых транзисторов записи, затворы которых подключены к шине записи, а стоки — к затворам и истокам соответственно третьего и четвертого нагрузочных транзисторов, сток пятого усилительного транзистора и затвор шестого усилительного транзистора подключены к затвору третьего нагрузочного транзистора, сток шестого усилительного транзистора и затвор пятого усилительного транзистора соединены с затвором четвертого нагрузочного транзистора, истоки пятого и щестого усилительных транзис, торов соединены со стоком третьего ключевого транзистора записи, загвор которого подключен к стоку ключевого транзистора, затвору и истоку пятого нагрузочного транзистора, затвор ключевого транзистора подключен к шине записи, стоки третьего, четвертого и пятого нагрузочных транзисторов сое динены с шиной питания, истоки ключе вого транзистора и третьего ключевого транзистора записи подключены к общей шине.