Устройство для измерения скорости изменения частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике. Цель изобретения - повышение точности измерения скорости изменения частоты - достигается путем выполнения дополнительных отсчетов. Устройство содержит входной формирова

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (зов G 01 R 2 :/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4635071/21 (22) 09,01,89 (46) 15.01.91. Бюл. М 2 (72) M.А,Павлов и А,А.Шевлягин (53) 621.317(088.8) (56) Авторское свидетельство СССР

Ра 1449924, кл, G 01 R 23/00, 1987, „„5U„„1620952 А1 (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СКОРОСТИ ИЗМЕНЕНИЯ ЧАСТОТЫ (57) Изобретение относится к измерительной технике, Цель изобретения — повышение точности измерения скорости изменения частоты — достигается путем выполнения дополнительных отсчетов. Устройство содержит входной формирова1620952

20

40 ватель 1, N счетных каналов 2, формирователь 3 времени счета, триггер 11, два коммутатора 18, 19, регистр 17 сдвига сигналов. управления коммутаторами, блок вычитания

4, индикатор 5, В устройство дополнительно введены N — 2 счетных каналов и регистр сдвига сигналов управления, а в формироваИзобретение относится к измерительной технике и предназначено для измепе ия и контроля скорости изменения частоты.

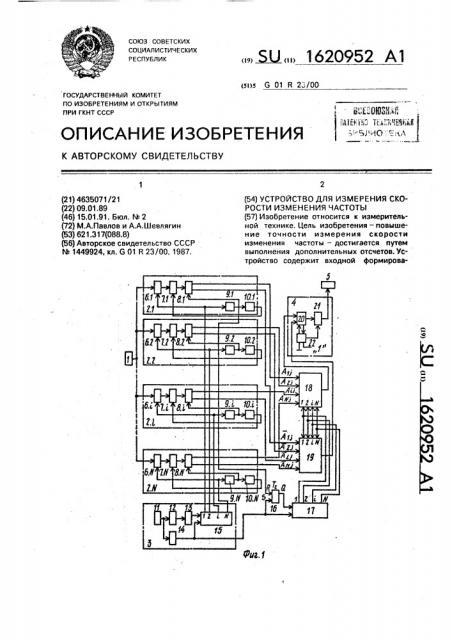

Цель изобретения — повышение точности измер ния скорости изменения частоты за счет уменьше, .я интервала интерполирования функции f(t), На фиг. 1 приведена структурная схема устройства для изб зрения скорости изменения частоты; на фиг. 2 — временные диаграммы работы устройства.

Устройство для измерения скорости изменения частоты (фиг. 1) содержит входной формирователь 1, N счетных каналов 2.1, 2.2,...,2,N, формирователь 3 времени счета, блок 4 вычитания и индикатор 5, Каждый 1-й счетный канал содержит последовательно соединенные селектор 6.l, счетчик 7,l, буферный регистр 8.I, а также последовательпо соединенные одновибратор 9.i nepenucu кода и одновибратор 10л импульса сброса.

Формирователь 3 времени счета образуют опорный r знератор 11, декадный делитель "2 частоты, формирователь 13 стробов, делитель 14 частоты и регистр 15 сдвига стробов. Устройство также содержит триггер 16, регистр 17 сдвига сигналов управления и коммутаторы 18 и 19.

Блок 4 вычитания включает сумматор

20, преобразователь 21 кодов и блок 22 BhIделения знака, В устройстве входы счетных каналов 2 подключены к выходу входного формирователя 1. В каждом счетном канале соединены последовательно селектор 6, счетчик 7, буферный регистр 8, а выход одновибратора 10 импульса сброса подключен к обнуляющему входу счетчика 7, выход одновибратора 9 переписи кода соединен с управля ощим входом буферного регистра 8.

B формирователе 3 времени счета соединены последовательно опорный генератор 11, декадный делитель 12 частоты, формировател 13 стробов, вход делителя

14 частоты соединен с выходом опорного генератора 11, а выход подключен к тактовому входу регистра 15 сдвига стробов и тактовому входу регистра 17 сдвига сигналоо управления. тель времени счета устройства введены де литель частоты и регистр сдвига стробов с соответствующими связями, что позволяет зэ счет уменьшения интервалов интерполяции функции повысить точность измерения скорости изменения частоты при одновре".енном увеличении быстродействия. 2 ил.

Выходы регистра 15 сдвига стробов соединены с селектирующими входами селекторов 6 и одновибраторов 9 переписи кода счетных каналов, Информационный вход регистра 15 сдвига соединен с выходом формирователя 13 стробов, а информационный вход регистра 17 сдвига сигналов управления подключен к выходу триггера 16, R-вход которого подключен к выходу одновибратора 9,1 переписи кода.

Управляющие входы коммутаторов 18 и

19 соединены с соответствующими выходами разрядов регистра 17 сдвигов сигналов управления.

Выходы коммутаторов 18 и 19 соединены с соответствующими входами блока 4 вычитания, выход которого соединен с входом индикатора 5. Прямые выходы буферных регистров 8 счетных каналов соединены с входами коммутатора 18. Инверсные выходы буферных регистров 8 счетныхканалов соединены с входами коммутатора 19, Сумматор 2С блока вычитания 4 представляет собой M-разрядный полный сумматор, который выполняет сложение двух двоичных чисел. Преобразователь 21 содержит известные злементы цифровой техники

ИСКЛЮ4АЮЩЕЕ ИЛИ, преобразователь двоичного кода в двоично-десятичный, Блок 22 выделения знака представляет собой одноразрядный полный сумматор, вхсд переноса которого подключен к выходу переноса старшего разряда сумматора 20, а выход переноса блока 22 соединен с входом переноса младшего разряда сумматора 20

Рассмотрим работу устройства в соответствии с време: ной диаграммой, приведенной на фиг. 2, Формирователь 3 времени счета из частоты опорного генератора 11 вырабатывает две последовательности импульсов, Первую последовательность импульсов формирует декадный делитель 12 частоты, управляющий работой формирователя 13 стробов, Вт орую последовательность импульсов формирует делитель 14 частоты.

Строб-импульсы с выхода формирователя 13 стробов поступают на информационный вход четырехразрядного регистра 15

1620952

50

М

Е}

t« тсч сдвига стробов, на тактовый вход которого поступают импульсы с выхода делителя 14 частоты, что обеспечивает относительный временной сдвиг строб-импульсов на выходах разрядов регистра 15 на величину (фиг. 2) т = тсчИ

t« — длительность строб-импульса формирователя стробов 13.

Таким образом, строб-импульсы одинаковой длительности, поступающие со сдвигом т= t« 2 с первого, второго, третьего и четвертого выходов регистра 15 сдвига стробов формирователя 3 времени счета последовательно на соответствующие селектирующие входы селекторов 6.1 — 6.4 счетных каналов 2.1-2.4, создают временные "ворота" для счетчиков 7.1 — 7.4, которые заполняются импульсами, сформированными из входной частоты импульсов входного сигнала формирователя и поступающими на объединенные между собой информационные входы счетных каналов 2.1 — 2.4.

В момент окончания времени счета первого счетного канала одновибратор 9.1 переписи кода вырабатывает импульс переписи кода, который поступает на управляющий вход буферного регистра 8.1 и переписывает код частоты, просчитанной счетчиком 7.1 за время t«, в регистр 8.1, после чего одновибратор 10.1 импульса сброса вырабатывает импульс. сброса, который поступает на обнуляющий вход счетчика 7.1, подготавливая первый счетный канал

2.1 к очередному измерению. Одновременно импульс переписи кода с выхода одновибратора 9.1 переписи кода поступает на

R-вход триггера 16, устанавливая его в единичное состояние (фиг. 2). В этом состоянии триггер 16 находится до момента прихода на $-вход импульса с выхода делителя 14 частоты, переводящего триггер в нулевое состояние.

В момент окончания времени счета второго счетного канала одновибратор

9.2 переписи кода вырабатывает импульс переписи кода, который поступает на управляющий вход буферного регистра 8.2 и переписывает код частоты, просчитанной счетчиком 72 за время t«, в регистр 8.2, после чего одновибратор 10.2 импульса сброса вырабатывает импульс сброса, который поступает на обнуляющий вход счетчика 7.2, подготавливая второй счетный канал

2.2 к очередному измерению.

В момент окончания времени счета третьего счетного канала одновибратор 9.3 переписи кода вырабатывает импульс переписи кода, который поступает на управляю5

35 щий вход буферного регистра 8.3 и переписывает код частоты, просчитанный счетчиком 7.3 за время тсч, в регистр 8.3, после чего одновибратор 10,3 импульса сброса вырабатывает импульс сброса, который поступает на обнуляющий вход счетчика 7.3, подготавливая третий счетный канал 2.3 к очередному измерению.

В момент окончания времени счета четвертого счетного канала одновибратор 9.4 переписи кода вырабатывает импульс переписи кода, который поступает на управляющий вход буферного регистра 8.4 и переписывает код частоты, просчитанной счетчиком 7.4 эа время t«, в регистр

8,4, после чего одновибратор 10.4 импульса сброса вырабатывает импульс сброса, который поступает на обнуляющий вход счетчика 7.4, подготавливая четвертый счетный канал 2.4 к очередному измерению.

Импульсы, поступающие с выхода делителя 14 частоты на тактовый вход регистра

17 сдвига сигналов управления коммутаторами, начиная с импульса, переводящего триггер 16 в единичное состояние, осуществляют потактовый сдвиг сигнала с уровнем

"1", поступающего с прямого выхода триггера 16 на информационный вход регистра 17.

В результате по мере продвижения по разрядам регистра 17 "1" на управляющие входы коммутаторов 18 и 19 последовательно поступают. управляющие сигналы с уровнем

"1", обеспечивающие подачу на входы блока

4 вычитания кодов частот с буферных регистров счетных каналов: с прямых выходов— через коммутатор 18, с инверсных выходов— через коммутатор 19. В результате на сумматоре 20 блока 4 вычитания происходит поочередное сложение кодов чисел Ац+ А1}, Asj + А2}, . A4} + Аз); Ag+1) + A4j, и т.д., т.е. производится вычитание кодов двоичных чисел, соответствующих двум последовательным измерениям частот в счетных каналах: Az} — A1}; Asj — Аг}, A4J — Аз); А10+1)- А4} и т.д.

Приращение частоты Ж на временном интервале t«определяется разностью между последовательными во времени значениями частот, измеренными поочередно в счетных каналах:

4 f} fj — f}-1:

Ь }+1 fj+1 — fj и т.д.

Скорость изменения частоты определяется как приращение частоты за время измерения:

1620952

fi +1 — 1) +> = тсч

40

Поскольку формирователь 3 времени счета формирует декадное время, то приращение частоты, определенное блоком 4 вычитания, является скоростью изменения частоты, выраженное в нормированных единицах.

В блоке 4 вычитания определяется знак изменения частоты (блок 22 выделения знака) и происходит преобраэованиедвоичного кода разности частот в десятичный (преобразователь 21).

Информация о скорости изменения частоты в виде прямого или инверсного кода в зависимости от знака суммы, преобразованная в удобную для считывания десятичную форму, поступает в индикатор 5.

В устройстве за счет выполнения дополнительных отсчетов функции f(t) на интервале тсч можно измерять с повышенной точностью скорость изменения частоты входного сигнала, Таким образом, по сравнению с известным предлагаемое устройство характеризуется повышенной точностью измерения скорости изменения частоты.

Формула изобретения

Устройство для измерения скорости изменения частоты, содержащее входной формирователь, выход которого соединен со счетными входами первого и второго счетных каналов, состоящих из последовательно соединенных селектора, счетчика и буферного регистра, а также одновибратора переписи кода и одновибратора импульса сброса, причем выход одновибратора переписи кода соединен с управляющим входом буферного регистра и с входом одновибратора импульса сброса, выход которого соединен с обнуляющим входом счетчика, триггер, R-вход которогб соединен с выходом однбвибратора переписи кода первого счетного канала, формирователь времени счета, содержащий последовательно соединенные опорный генератор, декадный делитель частоты и формирователь стробов, два коммутатора, причем первый информационный вход первого коммутатора соединен с прямым выходом буферного регистра первого счетного канала, а второй — с прямым выходом буферного регистра второго счетного канала, первый информационный вход второго коммутатора соединен с инверсным выходом буферного регистра первого счетного канала, второй информационный вход второго коммутатора соединен с инверсным выходом буферного регистра второго счетного канала, выходы коммутаторов подключены соответственно к первому и второму входам блока вычитания, выход которого соединен с индикатором, о т л и ч а ю щ e eс я тем, что, с целью повышения точности измерения скорости изменения частоты, в него дополнительно введены N — 2 счетных канала, входы которых объединены и подключены к выходу входного формирователя, N-разрядный регистр сдвига сигналов управления коммутаторами, информационный вход которого соединен с прямым выходом триггера, выходы разрядов регистра соединены с соответствующими управляющими входами первого и второго коммутаторов, а в формирователь времени счета введены N-разрядный регистр сдвига стробов и делитель частоты, причем информационный вход регистра сдвига стробов соединен с выходом формирователя стробов, а тактовый вход — с выходом делителя частоты, S-входом триггера и тактовым входом регистра сдвига сигналов управления, вход делителя частоты соединен с выходом опорного генератора, выходы разрядов регистра сдвига стробов соединены с селектирующими входами соответствующего счетного канала; прямые выходы

N — 2 буферных регистров N-2 счетных каналов соединены с соответствующими информационными входами первого коммутатора, а инверсные выходы этих буферных регистров соединены с соответствующими информационными входами второго коммутатора.

1620952

9.4

46

Ю4

/Я

Яр р

494(8.Z

Составитель В.Новоселов

Редактор А,Огар Техред M.Моргентал Корректор О,Кравцова

Заказ 4244 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 10>