Устройство для умножения чисел с контролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических узлов. Цель изобретения - повышение достоверности работы устройства. Устройство содержит группу регистров, матрицу элементов И, матрицу сумматоров , сумматор, выходной регистр, узел сравнения, триггеры, элементы И. Сомножители поступают на входы множимого и множителя устройства и записываются в регистр группы (по одному разряду каждого сомножителя в регистр) по синхроимпульсу с тактвого входа устропстиа. Результат вычислений записывается в выходной регистр. Затем происходит циклический сдвиг информации врегистрах группы,в результате чего меняются местами сомножители.Новый результат вычислений сравнивается узлом сравнения с содержимым выходного регистра. При неравенстве двух результатов триггер устанавливается в одиночное состояние, что говорит об ошибке в работе устройства. 2 ил. /) с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9) (И! (gy)g r, 06 r 11/00, 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4427356/24 (22) 17.05.88 (46) 15. 01.91. Бюл. Р 2

" (71) Одесский политехнический институт (72) А. В. Дрозд, В.Л. Полин, В. П. Новицкая, О.Н.Паули и Ю,В.Дрозд (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 1203512, кл . r, 06 Р ?/52, 1984.

Самофалон 1"..Г. и др, Прикладная теория цифровых автоматов. 1".иев:

Вища школа, 1987, с.95. (54) УСТРОЙСТВО ДЛЧ У П1ОИЕНИЯ П1СЕЛ

С 1ОНТРОЛП! (57) Изобретение относится к вычислительной технике и может бьггь использовано при построении арифметических узлов. Цель изобретения — повышение достоверности работы устройства. УстИзобретение относится к вычислительной технике и может быть использовано при построении арифметических узлов.

Целью изобретения является повышение достоверности работы устройства.

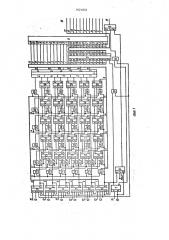

На фиг.1 приведена функциональная схема устройства для шестиразрядных сомножителей; на фиг.2 — временная диаграмма его работы.

Устройство (фиг.1) содержит группу 1 регистров, матрицу 2 элементов

И, матрицу 3 сумматоров, сумматор 4, выходной регистр 5, узел 6 сравнения, триггеры 7-9, элементы И 10, 11; входы 12, 13 множимого и множителя устройства соответственно, тактовый 14

2 ройство содержит группу регистров, матрицу элементов И, матрицу сумматоров, сумматор, выходной регистр, узел сравнения, триггеры, элементы И. Сомножители поступают на входы множимого и множителя устройства и записынаются в регистр группы (по одному разряду каждого сомножителя в регистр) по синхроимпульсу с тактвого входа устройства. Результат вычислений записывается в выходной регистр. Затем происходит циклический сдвиг информации в регистрах группы,в результате чего меняются местами сомножители. Новый результат вычислений сравнивается узлом сравнения с содержимым выходного регистра. При неравенстве двух результатов триггер устанавливается в одиночное состояние, что говорит об ошибке в работе устройства. 2 ил. и установочный 15 входы устройстна, информационный выход 16 устройства, контрольный выход 17 устройства.

Устройство работает следующим образом, На входы 12 и 13 устройства поступают множимое и множитель соответственно. Иа тактовый вход 14 устройства подаются синхроимпульсы типа меандр. Импульс, поступающий на установочный вход 15 устройства в начале работы,. устанавливает в нулевое состояние первый 7 и второй 8 триггеры.

В момент времени Т1 по заднему фронту синхроимпульса происходит при3 1621033 а

С выхода сумматора 4 снимаются старшие разряды (с седьмого IIo двенадцатый) произведения, а младшие разряды произведения (с первого по шестой) снимаются с выхода элемента

И первой строки первого столбца мат55 ем разрядов множимого и множителя в регистры группы 1.

Режим приема обеспечивается нулевым значением сигнала P на входах эа5 дания режима работы регистров группы 1, поступающего с прямого выхода первого триггера 7. С выходов регистров группы 1 разряды множимого и множителя поступают соответственно па первые и вторые входы элементов

И матрицы 2, которые определяют конъюнкции разрядов множимого и множителя. 1(онъюнкция с выходов элементов 11 каждой j-й строки (j+1)-ro .столбца матрицы 2 поступает на первый информацпо ный вход сумматора л-й строки j-ro столбца матрицы 3 (1 C j (п-1),где п — разрядность мнояимого и множителя).

1(опъюнкция с.выходов элементов И (j+1)-й строки первого столбца матрицы 2 поступает на вторые входы сумматоров j-й строки первого столбца матрицы 3.

На вторые входы сумматоров k-й строки каждого столбца матрицы 3, начиная с второго, поступают сигналы с выхода суммы сумматора (k + 1)-й строки предыдущего столбца матрицы 3 (1 (k n-2). На вторые входы сумматоров (n-1)-й строки каждого столбца матрицы 3, начиная с второго, поступают конъюнкции с выходов элементов И п-й строки предыдущего столбца матрицы 2, Третьи входы сумматоров первого столбца матрицы 3 подключены к шине нулевого потенциала устройства, Третьи входы сумматоров всех столбцов 40 матрицы 3 соединены с выходами переноса соответствующих сумматоров предыдущего столбца матрицы 3.

На сумматоре 4 суммируются сигналы с выходов суммы и переноса сумма- 45 торов (п-1)-го столбца матрицы 3 и выходов элемента И и-й строки n-ro столбца матрицы 2, причем в k-м разряде сумматора 4 складываются выход переноса сумматора k-й строки и выход суммы сумматора (k+1)-й строки (n—

1)-ro столбца матрицы 3. рицы 2 и выходов суммы сумматоров первой строки матрицы 3.

Все 12 разрядов произведения поступают на информационный вход выходного регистра 5 и записываются в него по сигналу с выхода элемента И 10 в момент 12 по заднему фронту синхроимпульса.

По этому фронту синхросигнала происходит циклический сдвиг содержимого регистров группы 1. Режим сдвига определяется единичным сигналом на прямом выходе триггера 7.

Таким образом, меняются местами множимое и множитель. Вычисление повторяется, но результат произведения в регистр 5 не записывается, а поступает. на первый информационный вход узла 6 сравнения, где сравнивается с предыдущим результатом, записанным в регистре 5. При несравнении устанавливается в единичное состояние триггер 9 и на контрольном выходе 16 устройства формируется единичный сигнал, говорящий о неисправности устройства.

Формулаизобретения

Устройство для умножения чисел с контролем, содержащее матрицу элементов И размерности их п (n — разрядность сомножителей), матрицу сумматоров размерности (n-1)х(п-1) и сумматор, причем выход каждого элемента

И j-й строки (1+1)-ro столбца матрицы соединен с первым информационным входом сумматора j-й строки j-ro столб" ца матрицы (1 с л (n-1), второй информационный вход, сумматора (п-1)-й строки j-го столбца соединен с выходом элемента И и-й строки j-го столбца матрицы, выход суммы сумматора р-й строки k-го столбца матрицы соединен с вторым информационным входом сумматора (р-1)-й строки (k+1)-го столбца матрицы (2 с р ((n-1);

1 c k < п-2), выход переноса каждого сумматора j-й строки k-го столбца матрицы соединен с третьим информационным входом сумматора )-й строки (k+1)-го столбца матрицы, второй информапионный вход сумматора j-й строки первого столбца матрицы соединен с выходом элемента И (j+1)-й строки первого столбца матрицы, третий информационный вход сумматора первой строки матрицы подключен к шине ну5 162 левого потенциала устройства, выход переноса сумматора j-й строки (п

1)-ro столбца матрицы соединен с

1-м разрядом входа первого слагаемого сумматора, k-й разряд входа второго слагаемого сумматора соединен с выходом суммы сумматора (k+1)-й строки (и-1)-ro столбца матрицы, выход элемента И и-й строки и-го столбца матрицы соединен с последним разрядом входа второго слагаемого сумматора, о т л и ч а ю щ е .е с я тем, что, с целью повышения достоверности работы устройства, в него введены группа регистров, выходной регистр, узел сравнения, два элемента

И и три триггера, причем первые и вторые разряды информационных входов регистров группы подключены к соответствующим разрядам входа множимого и входа множителя устройства соответственно,выход первого разряда i-ro регистра группы (1 .« i « n) соединен с первыми входами всех элементов И

i-го столбца матрицы, выход второго разряда i-ro регистра группы соединен с вторыми входами всех элементов

И i-й строки матрицы, тактовые входы регистров группы, счетный вход первого триггера и первые входы первого и второго элементов И подключены к тактовому входу устройства, выход второго разряда i-ro регистра группы соединен с последовательным входом i-ro регистра группы установочЭ

I ные входы первого и второго триггеров подключены к установочному входу устройства, прямой выход первого тригтриггера соединен с вторым входом первого элемента И, тактовым входом второго триггера и входами задания режима работы регистров группы, ин10 весный выход первого триггера соединен с вторым входом второго элемента И, выход первого элемента И соединен с тактовым входом выходного регистра, выход элемента И первой строки первого столбца матрицы, выходы суммы сумматоров первой строки матрицы и выходы суммы и выходы переноса сумматора соединены с соответствующими информационными входами выход-. ного регистра и соответствующими разрядами первого информационного входа узла сравнения, выход несрав- . нения которого соединен с информационным входом третьего триггера, выход которого является контрольным выходом устройства, выход второго элемента И и прямой выход второго триггера соединены с тактовым и установочным входами третьего триггера соответственно, выход выходного регистра соединен с вторым информационным входом узла сравнения и является информационным выходом устройства, информационный вход второго триггера подключен к шине единичноЗ5 го потенциала устройства.

1621033

1621033

6И

Ф2

Редактор А.Иаковская

Заказ 4248 Тирам Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Рауновская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Умгород, ул. Гагарина, !01

Якюд успрвосв5а

Рг ke3a

Р os Ф

Составитель В. Гречнев

Техред M,Äèäèê Корректор Н.Король