Систолический процессор для вычисления четырехточечного дискретного преобразования фурье

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специапизированных системах обработки сигналов высокой производительности . Целью изобретения является сокращение аппаратурных затрат за счет выведения из структуры систолического процессора умножителей. Поставленная цель достигается тем, что в систолическом процессоре для вычисления четырехточечного ДПФ, состоящем из четырех линейно связанных вычислительных блоков, каждая ячейка матрицы содержит дополнительно группу элементов ИЛИ, коммутатор, две группы элементов И, элемент И, элемент НЕ, блок задержки тактов, элемент задержки. 6 ил., 1 табл. i (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (И) (s1)s С 06 F 15/332

1043 А I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4458080/24 (22) 23, 05. 88 (46) 15. 01.91. Бюл. ),"- 2 (71) Ленинградский институт точной механики и оптики (72) Г.А.Кухарев, Н.Д.Новоселов и А.10.Тропченко (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 1196894, кл. О 06 F 15/332, 1983, Тезисы докладов Всесоюзной конференции Иетоды и микроэлектронные средства цифрового преобразования обработки сигналов. Рига. 1986, с.504-507. (54) СИСТОЛИЧЕСК111! ПРОЦЕССОР ДПЯ ВЫЧИСЛЕ1П!11 ЧЕТ1>1РЕХТО 1ЕЧНО ГО ДИСКРЕТНОГО

ПРЕОБРАЗОВАНИЛ ФУРЬЕ

Изобретение отнсоится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов высокой производительности.

Цель изобретения — сокращение аппаратурньгх затрат. "

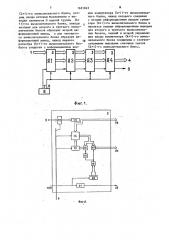

Па фиг.1. представлена функциональная схема систолического процессора четырехточечного дискретного преобразования Фурье; на фиг.2 — функционапьная схема первого вычислительного блока", на фиг.3 — функциональная схема (k+1)-ro (k = 1, 3) вычислительного блока; на фиг.4 — функциональная схема коммутатора; на фиг.5 — динамика работы вычислительных блоков по тактам; на фиг,б — временная диаграмма работы вычислительных блоков.

2 (57) Изобретение относится к вычислительной технике и может быль использовано в специализированных системах обработки сигналов высокой производительности, Целью изобретения является сокращение анпаратурных затрат за счет выведения из структуры систолического процессора умножителей.

Поставленная цель достигается тем, что н систолическом процессоре для вычисления четырехточечного ДПФ, со- стоящем из четырех линейно связанных вычислительных блоков, каждая ячейка матрицы содержит дополннтельно группу элементов ИЛИ, коммутатор, две группы элементов И, элемент И, элемент Н1., блок задержки тактов, элемент задержки. 6 ил ., 1 табл.

Процессор содержит информационный вход 1, первый вычислительный блок 2, с второго по четвертый вычислительные блоки 3, информационный выход 4, упранляюций выход 5, блок 6 синхронизации,второй 7 и первый 8 выходы блока синхронизации.

Вычислительные блоки 2и 3 содержат информационные входы 9 и 10, второй вход 11 синхронизации,первый регистр 12, блок 13 задержки, сумматор

14, второй регистр 15, группы 16 и

17 элементов И, элемент НЕ 18, эле.мент И 19, счетчик 20, элемент 21 задержки, группу 22 элементов ИЛИ, чнформационные выходы 23, 24, управляюпвш выход 25 и коммутатор 26.

Коммутатор 26 содержит входы 27 и

28 вецестненной и мнимой частей комплексного числа, управляющие входы 29

1621043 К Ко (2) Выход комму— татора

1 41 о

Вход коммутатора

Умножен:е на

51 52

27 28

С вЂ” ЕХ, Х =Lzo, х,, c= (с„с,, 1 1 1 1

I -j -1 j

1 -1 1 -1

Е, 1

1 j -1

ЧK K (-Ь); и 30, группы элементов И 31-38, группы элементов НЕ 39&2, элементы И 43—

46, элементы IIE 47 и 48, группы элементов ИЛИ 49 и 50 и выходы 51 и

52 (фиг.4) .

Систолический процессор четырехточечного дискретного преобразования

Фурье работает следующим образом.

Устройство осуществляет выполнение 10 процедуры ДПФ: где С и - — - четырехкомпонентные векторы, т.е.

3) т т — векторы разСо, С> мера 4х1, 20 компоненты которых определяют информацию на входе и выходе систолической матрицы;

Š— матрица дискретных экспоненФ 25 циальных функций (ДЗФ) 4-го порядка

K h с элементами 1,„, = И, -ехр (-j 2nkn/

/4); 1;,и 6 0,3, т.е.

Умножение осуществляется на тривиальные множители 1,"1, ), -1, Голь умножителя в предлагаемой систоличе ской матцице выполняет коммутатор 26. "0

1(омпоненты вектора входных данных представляют собой комплексные числа, т.е. х = а + jb,где а = Ге(х) вещественная, а Ь = Iù(х) — мнимая части комплексного числа. На входы

27 и 28 коммутатора поступают вещественная а и мнимая Ъ части комплексного операнда х. В качестве инициирующих сигналов коммутатора выступают сигналы 1(и I".I двухразрядного счет- 50 чика 20 и в зависимости от комбинации (I(< (см. таблицу) формируется результат Y.< и У< на выходах 51 и 52 коммутатора 26 соответственно, а именно; 55

1 = 1 Ко " К(КоЬ ч К о (а) Ч

У = К,К,Ь Ч К Ко(а) " К1Ко(-Ь)Ч где и У вЂ” функция коммутатора по выходам. !

00 а jb à jb +1

01 à jb Ь -За -)

10 à jb -а . -jb -1

11 à jb -Ь ja +j

Входной операнд х поступает на входной регистр 12 первого блока 2 (фиг.2) в первый такт времени (фиг,5) и с задержкой на блоке 13, равной задержке коммутатора 26, передается на выход 23 блока 2 и соответственно на регистр 12 второго блока 3, а также поступает на первый вход сумматора

14 ° В первом такте просходит сложение хо с О, поступающим на второй вход сумматора из регистра 15, далее с выхода сумматора хо поступает через открытую группу элементов И 16 на информационный вход регистра 15. В первом такте времени состояние счетчика "00" и, следовательно, на вторых входах элементов И 17, имеются запрещающие "О", а на вторых входах

И 16 - разрешающие "1". Во втором такте включается в работу второй блок 3 (фиг.3) при этом счетный импульс с задержкой в один такт на элементе 21 первого блока 2 приходит на счетный вход счетчика 20 второго блока 3. В этом такте состояние счетчика первого блока "01", а второго блока — "00". Таким образом, входной операнд х во втором блоке, проходя через коммутатор 26 (управляющие сигналы "00") умножается на +1, в первом блоке во втором такте происходит сложение входного операнда х с накопленным х и запись хо + х в регистр 5. В третьем такте (фиг.5) включается в работу третий блок 3, при этом с учетом задержки счетного импульса состояние счетчиков первого, второго и третьего вычислительных блоков "10"„ "01", "00". В этом

1043

30

40

55 такте в пер«ом блоке 2 н регистре

15 за!тисы»ает(.я сумма (х о + х т +

+ х ), «о втором блоке 3 входной (7flp ранд хт, проходя через коммутатор (управляющие сигналы 01) умножается на "1, складттнается с х„н результат записывается в регистр 15, в третьем блоке 2 в этом такте входной операнд х, проходя через коммутатор, домножается на +1, складывается с 0 и записывается в регистр 15. В четвертом такте работают все четыре вычислительных блока, причем состо,яние счетчикон "11"., "1О", "01", ."00 1 и результат суммы (хо + х, +

>х + х. ) н пер«ом блоке 2 с выхода

1 сумматора через открытые элементы, И 17 (элементы И 16 закрыты управля ющим нулем), выход 24, вход 10 вто-. рого блока 3, элементы ИЛИ 22, выход

24 второго блока 3 и т.д, проходит через систолический процессор н виде результата на выход 4. Во втором блоке 3 н этом такте в регистре 15 формируется сумма (х — j ..; — х ), а в третьем блоке 3 — (хо — хт) . .В пятом такте форм!!руется результат во втором блоке и. через открытые эле. менты И 17, .элементы ИЛ!1 22, выход

24, вход 10 третьего блока 3 и т.д. проходит на выход 4 систолического процессора. В шестом и седьмом так-. тах фор>мируется результат н третьелт и четвертом блоках 3 соответственно (фиг.5). На фиг.6 представлена временная диаграмма четырех тактов работы одного Bt,tvffcnft Tesr l Ifof.o. блока систолического процессора.

Формул а из обре те»ия

Систолический процессор для вычисления четырехточечного дискретного преобразования Фурье, содержащий четыре вычислительных блока и блок синХронизации, причем информациоштый вход процессора подключен к информациоинотлу входу первого вычислительного блока, первый вход синхронизации которого соединен с первыми входами синхронизацит! с второго по четвертый вычислительных блоков и с первым выходом блока синхронизации,первый и тэторой информацношьые ньгходы

k-ro (Е = 1,3) вычислительного блока соединены соответственно с первым и вторым инфортлационт!ьтмт! Входами (1с+1)го вычислительного блока, информациФ

0 lit!3 !It 131 IxoJl; че (Вер Tot o ныч(1(зттлт(..>t lэ((i>г(7 бл(>кл я»ляется информлцион»ьfN Выходом ттроцес(.(>рл, !три этом клждт,N Бь(чттслтттет!1.»тлтт блок (.одержит л,«а регистра и суммлт(>р, первый ннформл ионныи 13x(>tf вычислительного бттока подключен к информационному «ходу первого рс(гнстрл, Бых(>д второго регистра соединен с перным информационным Бходом сумматора,cffftxpo«xoд которого соединен с cff ftxpntfx<>JtaNff первого. и второг(регистров и является первым входом синхронизлпии Вычислительного блока, о т л и ч л ю 1! 1! и с я тем, что, с це|тью сократ(тети!я лпттлрлтурных

3QTp(3T > BTopoff Выход бп(>к(l elf fix pofflf злции соединен с 13торым входом синхронизации первого вычислительного блотсл, упрлнляющнт! «Ыхоц k го Бычислительногo блока соединен с Вторым входом синхро»излцнн (k+1)-го вычислителштогo блока, ут117лв>тя!опт!!1! выход четвертого»ь нтстти . ель»ог(7 блока является у!117(1»ттяюгдит! Быходотт проттессора, причем 1(л.т(дьтй hf>IHcJIII Tpль»ый блок допол»ителт.но содержит дне rpyttttt t элементов И, элемент НГ, элел!еттт И, . счетч!11 та кто« 11 эут t f(.ft t злдержкн причем Быхо>т, элемента задержки является уира«ляюшим Выходом каждого Bfl !Исттител ьнот О б>1(7к(3 > Втор(71! Вход elf »

xpnI3ff atfItt3 которого соедине» с входом элемента злд(р>(ки и со счетным Вхо дом счетчика тлкто«, «btxoJlы которого соединен f c uxoJia»ff элемента И, выход которот о соецп те» с первыми входами элементов И первой группы и через элемент Нà — с первыми входами элементов И второй группы, «ыходы которьг. соединены с информационными входами «торого регистра, выходы .сумматора соединены с вторыми входами элементов И первой и Второй групп, кроме этого, первый вычислительный блок дополнительно содержит блок задержки, причетл выход первого регистра через блок задержкй соединен с нторым информлт!иот(нт,тми»ходом сумматора и с первым информациот(ным выкодом первого вычислительного блока, «торой пнформациошптй выход которого образован выходами элементов И первой группы, кроме этого (k+1)-й вычислительный блок дополнительно содержттт коммутатор .и группу элементов ИЛИ, причем второй информлттионттыт! вход (k+1) -го вычислительного блока соединен с первыми входами элементов ИЛИ группы

1621043

ФиГ 2.

t (Ic+1)-го вычислительного блока, вторые входы которых подключены к выходам элементов Й первой группы (К+

4 1)-го вычислительного блока, выходы которых дпя второго и третьего вычислительных блоков образуют второй информационный выход, а для четвертого вычислительного блока образуют ин.формационный выход, выход первого 1п регистра (k+1)-ro вычислительного блоблока соединен с инфоомационным входом коммутатора (k+1)-ro вычислительного блока, выход которого соединен с вторым информационным входом сумматора (k+1)-го вычислительного блока и является первым информационным выходом для второго и третьего вычислительных блоков, первый и второй управляющие входы коммутатора (1с+1)-го вычислительного блока соединены с соответствующими выходами счетчика тактов (k+1)-го вычислительного блока.

1621043

1621043

162!043

1621043

Тсч.

И22

Редактор Л.Пчолинская

Заказ 4248 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Г1осква, К-35, Раушская,наб., д. 4/5

tt t t

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Вых

Составитель Ю.Ланцов

Техред Г1.Дидык Корректор Н.Король