Преобразователь напряжения в интервал времени

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в составе информационно-измерительных систем автоматического контроля, в частности в. цифровых вольтметрах для измерения удельного электрического сопротивления полупроводниковых материалов двухзондовын методом, иетырехзондовым методом и методом сопротивления растекашя. Цель изобретения - увеличение разреыающеп способности и обеспечение возможности лреоьразовання напряжений обеих полярностей - достигается за счет введения дополнительных элементов и изменения схемы погического блока, 1 з.п. ср-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

А2 (gg)g Н 03 М 1/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР

{61) 1282331 ,(21). 4634257/24 (22) 09.01.89 (46) 15.01.91. Бюл. N - 2 (71) Научно-исследовательский конструкторско-технологический институт средств контроля электроннои аппаратуры и изделий электронной техники (72) .А.И. Федонин, N.А, Брежнев, Д.А. Кувшинов и Е,В. Финк (53) 681.325(088,8) .(56) Авторское свидетельство СССР

1282331, кл. Н 03 М 1/52, 1984 (прототип), (54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ Б ИНТЕРВАЛ БРЕМЕНИ

Изобретение относится к цифровой электроизмерительной технике и может быть кспользавано в составе информационно-измерительных систем автоматического контроля, в частности цифровых вольтметрах для измерения удельного электрического сопротивления

° полупроводниковых материалов двухзандовым методом, четырехзондовым методом и методом сопротивления растекания о

Цель изобретения — повышение разрешающей способности и обеспечение возможности преобразования напряжения обеих полярностей.

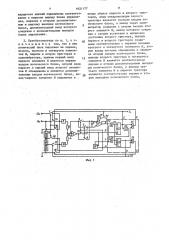

На фиг. 1 представлена функциональная схема предлагаемого преобразователя на фиг. 2 и .3 — временные диаграммы его работы.

„„SU„„1621177

2 (57) Изобретение относится к цифровой электроизмерительной технике и может быть использовано в составе информационно-измерит ельных систем автоматического контроля, в частности в цифровых вольтметрах для измерения удельного электрического сопротивления полупроводниковых материалов двухзондовым методом, четырехзондовым методом и методом сопротивления растекания. Цель изобретения — увели ение разрешающей способности и обеспечение возможности пр еобразования напряжений обеих полярностей — достигается за счет введения дополнительных элементов и изменения схемы логического блока, 1 з,п, Ф-лы, 3 ил.

Преобразователь напряжения в интервал времени содержит первый 1 и второй 2 ключи, масштабный усилитель

3, операционный усилитель 4, токоограпичиваюший элемент 5, выполненный на резисторе, третий 6 и четвертый 7 ключи, накопительпьп элемент, выполненньп в виде конденсатора 8, пятый 9 и шестой 10 ключи, компаратор 11, логический блок 12, блок 13 управления, седьмой ключ 14, делитель 15 напряжения, восьмой 16, девятый 17 и десятый 18 ключи, даполнительньп масштабный усилитель 19, дополнительный токоаграничивающий элемент 20, выполненньп в виде резистора, потенциометр

21 и одиннадцатьп ключ 22, Логический блок 12 выполнен на первом 23, втором 24, третьем 25 и чет16211 77

U + - -- Т = О

0 К2 п Rg Xo (2) UoKz кс 7„ (3) (4) о

35 где Бо

Н Махе

Н

К„и К

ТхоI тх,—

С

П вертом 26 элементах И, первом 27 и втором 28 триггерах и ддновибраторе 29.

На фиг. 2 и 3 обозначены: А А, . F - сигналы на первом, втором и третьем выходах генератора тактовых импульсов (блока 13 управления); Ц вЂ” из-! менение напряжения на нижней обкладке конденсатора 8 относительно верхней; . — сигнал на выходе комнаратора 11;

С вЂ” сигнал на выходе первого триггера

27 и на управляющих входах четвертого и одиннадцатого ключей 14 и 22; Р— сигнал на выходе второго триггера 28 и на управляющем входе девятого ключа

17; Š— сигнал на выходе четвертого элемента И 26 и на управляющем входе десятого ключа 18; О - сигнал на выходе третьего элемента И 25 и на управ- 20 ляющем входе второго ключа 2; Н— сравнение потенциалов на входах компаратора 11 с учетом собственных шумов последнего.

Преобразователь работает следующим 25 образом.

В первый полупериод работы преобразователя в течение фиксированного интервала времени Т интегрируется сумма преобразуемого напряжения U> и 30 напряжения на первом выходе делителя

15 напряжения Uo- К, Ио окончании ин. тервала времени Т состояние ключей б 10 и 7,9 изменяется, вызывая переворот конденсатора 8 в цепи отрицательной обратной связи операционного усилителя 4. Данное включение сохраняется в течение второго полупериода преобразования также длительностью Т.

В начале второго полупериода преоб- > разования в течение информативного ин,тервала времени ТН посредством один надцатого ключа 22 принудительно изменяется порог срабатывания компаратора

11 (напряжение U> и происходит интег- 45 рирование опорного сигнала U на конденсаторе .8, причем напряжение на последнем убывает. В момент достижения напряжением на конденсаторе 8 порого>«о напряжения Пя компаратора 11 пос-50 ледний формирует положительный .импульс, обеспечивающий отключение опорного сигнала Uo и подключение уменьшенного опорного сигнала Uo, К ф второго выхода делителя 15 напряжения. В этот момент формируется передний фронт дополнительного информатив-! ного интервала времени ТН и устанавЛивается собственный порог срабатывания компаратора 11. Фронт окончания

I интервала времени Т формируется комХ паратором 11 в момент снижения напряжения на конденсаторе 8 до собственного порога срабатывания, В оставшееся время до начала следующего цикла преобразования, входы масштабных усилителей 3 и 19 подключаются к общей шине и поэтому на конденсаторе 8 может интегрироваться только напряжения смещения 1, включающее напряжение смещения масштабных усилителей 3 и 19 и операционного усилителя 4.

Поскольку инверсия включения конденсатора в цепи отрицательной обратной связи осуществляется через полупериод преобразования, влияние напряжения смещения 1 (в силу постоянства) практически исключается из результата преобразования.

Обеспечение максимальной разрешающей способности преобразователя предполагает выполнение условий, описываемых системой уравнений:

Uo K(По Uo К2

Т + --- Т + ---, — Т = 0

RC хо К xo (1) напряжение опорного сигнала (положит ель но е); максимальное положительное напряжение преобразуемого сигнала; коэффициенты передачи делителя 15 напряжения для первого и второго выходов; длительность полупериода преобразования; информационный интервал времени при Uх =0; дополнительный информатнв-. ныи интервал времени при

v„-- o; сопротивление резисторов 5 и 20 (сопротивления могут быть неравными); емкость конденсатора 8; напряжение порога срабатывания .компаратора 11 в течен е интервала времени Т, S о со» (10) 1 1х»»схкс Тхо fF/Ê

5 162 спектральная плотность приведенных к входу собственных шумов компаратора 11; частота единичного усиления компаратора 11; частота импульсов синхронизации на третьем выходе блока 13 управления.

1! 77 6

T до минимально возможного с нракХ тической точки зрения. В этом случае разрешающая способность преобразова5 теля для обеих полярностей сигнала

Бх должна быть не менее, чем

Ux макс Т0

Txo+ К1Тхо (5) ссn = - ко сс ГБо у; (6) RC — + -,, (7)

axe K Т (Тхо+К Тхо ) fp 6о!

Т (8) В случае U>g 0 результат преобразования должен вычисляться по формуле

1 с Uõ+ UaK»

Т + Тх = - — ---- — Т, (9)

К, х х= Бо причем дополнительньпл информативный ,.с с интервал времени Т„= Тхо практически не зависит от U, Интеграл времени Т!» связан с U прямо пропорциональной зависимостью. Исходя из этого, для повыпения разрешающей способности преобразователя необходимо уменьшить

Уравнение (1) справедливо для случая, когда напряжение преобразуемого сигнала U = О, Уравнение (2) характеризует операцию интегрирования уменьшенного делителем 15 напряжения опорного сигнала

Uо за время Тхо

Уравнение (3) определяет скорость изменения напряжения на конденсаторе.

8 во время интегрирования уменьшенного делителем 15 напряжения опорного сигнала Ц за время Т . 11аксиь»аль/

Хо ная разрешающая способность достигается при скорости, равной отноше»»и»о напряжения собственных шумов компаратора

11 (фиг. 3) к периоду импульсов синхронизации (1/Е ) на третьем вь»ходе блока 13 управления.

Уравнение (4) определяет динамический диапазон преобразуемого сигнала U>.

Параметры Uo, К, U, R С для

П данного пр ео бра зоват еля являются искомыми, Решение системы уравнений имеет следующий вид:! р 1IpH U)(y»»yp 1с5В; Т = 2 10 с;

Ухо 9 1 0 с; » хю 1 ° 1 0 5с; К = 1 / 6 >

f z = 106 Гц и при использовании в качестве компаратора 11 операционного усилителя КР544Д1А с»3 f = 10 Гц и !

1В = 3 ° 1О В/Гц по соотношениям (5):-(8) легко определить Uî = 3,33 В; U = 3-10 В; RC = 6,8 10 с; K<=0,453.

В этом случае, используя соотноше20 ние (10), можно определить N< хмаке

144000. Это почти в шестнадцать раз превышает значение разрешающей спо. собности преобразователя-прототипа, Таким образом, предлагаемь»й» преобразователь обладает более высокой разре»пающе1» способностью и обеспечивает возможность преобразования входных сигналов обеих полярностей.

30 Ф о Р м У л B H з о б р е и е и и я

1„ Преобразователь напряжения в интервал времени по авт.св. 1! 1282331, отличающийся тем, что, с целью повышения разрешающей способности и обеспечения воэможности преобразования напряжений обеих полярностей, в него введены потенциометр, восьмой, девятьп1, десятьп» и одиннад40 цатьп» ключи, дополнительный токоограничивающий элемент, выполненный па резисторе, дополнительный масштабный усилитель и делитель напряжения, входы которого являются соответственно

45 шиной опорного сигнала и общей»шлнсо»», а выходы через восьмой и девятьпл ключи соответственно соединены с входом дополнительного масштабного усилителя, вход которого через десятый ключ подключен к общей оп»не, выход через резистор — .к инвертирующему входу операционного усилителя, первый и»»7opou выводы балансировки нуля компаратора соединены с первым и вторым выво55 дами потенциометра соответственно, подвижный контакт которого через одиннадцатый ключ подключен к шине питания компаратора, управляющие входы восьмого, девятого, десятого и один1621177 надцатого ключей подключены соответственно к первому выходу блока управления, первому и второму дополнительным и -первому выходам логического блока, дополнительный вход которого соединен с дополнительным выходом блока. управления.

2. Преобразовать по и 1У о т- 10 л и ч а ю шийся тем, что в нем логический блок выполнен на первом, втором, третьем и четвертом элементах И, первом и втором триггерах и одновибраторе, причем первый вход первого элемента И является первым входом логического блока, второй вход первого,и первый вход второго элементов И объединены и являются дополни-. тельным входом логического блока, выход первого элемента И подключен к входу сброса первого и второго триггеров, вход синхронизации первого триггера является третьим входом логического блока, а выход через одновибратор соединен с вторым входом второго элемента И, выход которого соединен с входом установки в единичное состояние второго триггера, выходы первого и второго триггеров соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых объединены и являются вторым входом логического блока, выходы второго триггера и четвертого элемента И являются соответственно первым и вторым дополнительнь и выхода ми логического блока, а выходы третьего элемента И и первого триггера являются соответственно первым и вторым выходами логического блока, 1621177! (I !

Фиг,5

Составитель В, Махнанов

Техред Г..ГГикеы Корректор М. 11ожо

Редактор А. Лежнина

Тираж

Заказ 4255

Подписно.е

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раутская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101