Устройство для измерения сопротивлений

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной технике и может использоваться в цифровых омметрах и комбинированных приборах. С целью упрощения устройства и повышения точности измерения в него введены блок 22 резисторов с резисторами 12, 18-20, выполненных по единой технологии и расположенных на одной подложке, и измеритель 11 отношения токов. Измеряемый резистор 3 включается в цепь обратной связи операционного усилителя 1. По командам блока 21 управления коммутаторы 8 и 9 работают в противофззе, при этом Р одном из тактов запоминающий конденсатор 13 соединяется с выходом и инвертирующим входом операционного усилителя 17. а в другом - с источником 10 ЭДС Тогда на вход усилителя 1 поступает в одном такте величина напряжения источника 10, а в другом - нулевой сигнал с учетом ошибок смеа1вния. Измеритель 11 определяет отношение в каждом такте, а конечный результт получается в вычислительном блоке 15 и отображается а блоке 16 индикации. Образцовый резистор 14 преобразует напряжение в ток. Клеммы 4, 7, 2 и 6 являются токовыми и потенциальными соответственно Коммутатор 5 служит для выбора предела измерений , В описании приведены примеры реализации блока 21, измерителя 1 1 и блока 16. 2 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

s G 01 R 27/02

ГОСУДАР СТ В Е ННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4042138/21 (22) 24.03.86 (46) 30.01.91, Бюл. М 4 (71) Производственное объединение "Краснодарский ЗИП" (72) Г.А. Кийков и Ю,И. Синельников (53) 621,317.7(088.8) (56) Авторское свидетельство СССР

N 566190, кл, G 01 R 17/02, 1975.

Авторское свидетельство СССР

М 1239608, кл. G 01 R 27/02, 1984. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЙ (57) Изобретение относится к электроизмерительной технике и может использоваться в цифровых омметрах и комбинированных приборах. С целью упрощения устройства и повышения точности измерения в него введены блок 22 резисторов с резисторами 12, 18 — 20, выполненных по единой технологии и расположенных на одной подложке, и измеритель 11 отношения токов. Измеряемый

„„ 4 „„1624352 А1 резистор 3 включается в цепь обратной связи операционного усилителя 1. По командам блока 21 управления коммутаторы 8 и 9 работают в г: ротивофгэе, при этом в одном из тактов запоминающий конденсатор 13 соединяется с выходом и инвертигующ1м входом операционного усилителя 17, а в другом— с источником 10 ЭДС. Тогда на вход усилителя 1 поступает в одном такте величина напряжения источника 10, а в другом — нулевой сигнал с учетом ошибок смещения.

Измеритель 11 определяет отношение в каждом такте, г конечный результат получается в вычислительном блоке 15 и отображается в блоке 16 индикации, Образцовый резистор 14 преобразует напряжение в ток.

Клеммы 4, 7, 2 и 6 являются токовыми и потенциальными соответс венно t,оммутзтор 5 глужит для выбора предела измерений, В описании приведены примеры реализации блока 21, измерителя 11 и блока

16, 2 ил.

1624352

Изобретение о1носится к электроиэмерительной технике и может быть использовано в цифровых омметрах и комбинированных приборах, Целью изобретения является упрощение устройства и повышение точности измерения.

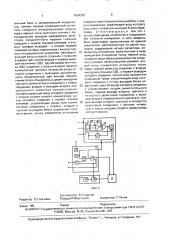

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — пример реализации блоков управления, измерителя отношения токов и блока индикации, Устройство для измерения сопротивлений содержит операционный усилитель 1. инвертирующий вход которого через потенциальную клемму 2 соединен с IlBpBblM выводом измеряемого резистора 3 и токовой клеммой 4, которая соединена с выходом коммутатора 5. второй вывод измеряемого резистора 3 соединен с потенциальной клеммой 6 и токовой клеммой 7, которая соединена с выходом операционного усилителя 1, неинвертирующий вход которого соединен с первыми входами коммутаторов 5, 8, 9, первым выводом источника ЭДС 10 и третьим входом измерителя 11 отношения токов, второй вход которого через резистор

12 соединен с вторым выводом источника

ЭДС 10 и вторым входом коммутатора 8, тре гий и четвертый входы которого соединены с выводами запоминающего конденсатора 13, потенциальная клемма 6 через образцовый резистор 14 соединена с первым входом измерителя 11 отношения, вы;;д которого через вычислительнь.й бло,< 15 соединен с входом блока 16 индикации, два выхода коммутатора 8 объединены с сооТ ветствующими выходами коммутатора 9 и соединены соответствено с инвертирующим входам и выходом операционного усилитегя 17, неинвертирующий вход которого соединен с вторым входом коммутатора 5, третий — пятый входы которого соединены с вторыми выводами резисторов 18-20, первые выводы которых объединены и соединены с выходом опврэционного усилителя 17.

Управляющие входы коммутаторов 8, 5, 9, блока 16 индикации, измерителя 11 отношения токов и вычислительного блока 15 соединены с первого по шестой выходами блока 21 управления соответственно.

Резисторы 12, 18-20 образуют блок 22 резисторов, которые выполнень1 по единой технологии и на одной подложке.

Измеритель 11 отношения токов (см. фиг. 2) содержит ключи 23, 24, входы которых являются первым и вторым входами измерителя 11 отношения, выходы ключей

23 и 24 объединены и соединены с входом интегратора 25, выход которого через компаратор 26 соединен с первыми входами

55 элемента И 2/ и триггера 28, второй вход которого является уп равляюгцим входом измерителя 11 отношения т. ков г1 соединен с управ1яющим входом ключа 23 и вторым входом элемента И 27, третий вход которого соединен с выходом триггера 28 и управляющим входом ключа 24, выход элемента И

27 является выходом измерителя 11 отношения токов.

Блок 16 индикации (см. фиг. 2) содержит запоминающий регистр 29. вход которого является входом блока 16 индикации, jllравляющим входом которого является управляющий вход запоминэ,ощего регистра

29, выход которого ссединен с входом цифрового индикатора 30.

Блок 21 управления (:м. фиг, 2) содержит переключатель 31 диагазонов, выход которого является вторы:.1 зыходом блока 21 управления, вторым вь .ходом которого является выход элемента И 32, первый вход которого соединен с первым выходом счетного триггера 33 и является четвертым выходом блока 2 1 управления, вторсй и шесгой выходы которого объединены и явля1отся вторым выходом счетного триггера

33, вход которого является пятым в одом блока 21 управления и соединен с выходом генератора 34 входом и гервым выходом счетчика 35 второй выход которого соедин н с вторым входом элемента И 32, Vc.ãðoéñTI3o работает следующим образом.

Блок 21,правления в зависимости от поддиэпазона измерения подключает через перекл1очатель 31 диапазонов и коммутатор

5 соответствующий резистор блока 22 резисторсв к токовому выводу измеряемого резистора 3 и неинвертирующему входу операционного усилителя 17. По командам блока 21 управления коммутаторы 8 и 9 работа1от в противофазе ким образом, чтобы при одном такте запоминающий конденсатор 13 подключался между инвертирукщим входом и выходом операционного усилителя 17. Коммутатор 9 разомкнут, В .:,ледующем такте заг,оминающий конденсатор 13 подкл1очается к исто, нику ЭДС

10, коммутатор 9 замкнут и соединяет выход усилителя 17 с его входом, Г1рИ ГОЛъШОМ ВХОДНОМ СОГрОтИВЛЕНИИ

onepaqvri ного усилителя l7, малых токах утечки в I o.. мутаторах 8 и 9, высокой тактовой частоте запоминающий хонденсатор 13 быстро зарядится до напряжения Е источника 10 ЭДС и будет сохранять его неизменным при последующей. работе устройства.

Это позволяет считать, что коммутатор 8 при одном из двух тактов включает в цепь отрицательной обратной связи операцион1624352 ного усилителя 17 источник 10 ЭДС равной Е. При другом такте коммутатор 9 замкнут и в обратной связи операционного усилителя 17 ЭДС равна нулю.

При наличии смещения нуля усилителя 5

17 по напряжению Ео и малом смещении его нуля по току на резисторе 18 с сопротивлением Ro при одном такте будет поддерживаться напряжение Е + Ео, а при другом такте — напряжение, равное Ео. Ток через 10 резистор 18 будет попеременно принимать значения

Rx R12

n; — п2 =—

Ro Rt4

Е + Ео I Еo ! = — — и (Rî по

При высоких входных сопротивлениях операционных усилителей 1 и 17 ток через коммутатор 5 и измеряемый резистор 3 будет таким же в зависимости от такта изме- 20 рения, Напряжение на выходе операционного усилителя 1 будет равно

U =I Rx = — (Е + Ео) Ro

Ток, поступающий на первый вход измерителя 11 отношения токов через образцовый резистор 14, величиной R14 будет равен

R12 Rx п2

Р14 Ro

Ео

45

R1 Rx

П1 — П2

R R

Команды на вычислителI. Iûé блок 15 и

50 запоминание значения nl — п2 регистром 29 поступают с выхода счетного триггера 33.

Управление коммутаторами 8 и 9 осуществляется сигналами с двух противофазных выходов счетного триггера ЗЗ.

Формула изобретения

Устройство для измерения сопротивлений, содержащее измеритель отношения, два операционных усилителя, образцовый резистор, источник ЭДС. три коммутатора, блок управления, блок индикации, вычисли11 R R п1

12 Й14 RoE 12 Rx Eo или п2 =

R14Ro Е

R при одном такте и U = — Е при другом, I x

Ro где Rx — величина сопротивления резистора

U Rx

I1 = — = — — — (Е + Ео)

R14 1 14 Ro г ри одном такте и

1 Rx Ео при другом, Ток, поступающий на второй вход измерителя 11 отношений токов через резистор

12, величиной R12 будет равен I2 =- — как

Е

R12 в первом, так и во втором такте.

Измеритель 11 отношения токов при каждом такте по командам блока 21 управления находит отношения в зависимости от такта и передает полученные результаты в вычислительный блок 15, который вычитает из каждого нечетного результата п1 четный результат п2 и полученную разность, являющуюся результатом измерения

Измеритель 6 отношения токов преобразует отношения токов в количество импульсов и работает по методу двухтакгного интегрирования. Синхронизация работы измеритеггя 6 осуществляется блоком 21 yrpaeneIIIl4, в котором формируются временные интервалы путем деления частоты генератора 34 счетчиком 35. Когда ключ 23 замкнут, напряжение на выходе интегратора 25 возрастает.

Разряд интегратора 25 при замкнутом ключе 24 будет продолжаться до момента, когда напряжение на выходе интегратора 25 достигает нулевого значения. Компаратор

26 через триггер 28 размыкает ключ 24, прекращается разряд интегратора 25, закрывается элемент И 27 и прекращается поступление импульсов генератора 34 в вычислительный блок 15. Количество импульсов, поступающих в вычислительный блок

21 в четные и нечетные интервалы, будет определяться выражениями

R12Rx Е+Ес

r11 — + А;

R14 Ro Е где А — постоянная величина, пропорциональная величине смещения нуля интегратора 25.

В вычисли- ельном блоке 15 осуществляется операция вычитания из четных результатов измерения нечетных результатов

1624352

Фие. 2

Составитель В,Смирнов

Техред M.Моргентал Корректор Т.Палий

Редактор О.Спесивых

Заказ 185 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям.при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород. ул.Гагарина, 101 тельный блок и запоминающий конденсатор, причем первый операционный усилитель соединен инвертирующим входом через первую потенциальную клемму с потенциальным выводом измеряемого резистора. соединенного первым токовым выводом с первой токовой клеммой, а вторым токовым выводом — с второй токовой клеммой, которая подключена к выходу первого операционного усилителя, неинвертирующий вход которого соединен с первыми входами трех коммутаторов и первым выводом источника ЭДС, другой вывод источника ЭДС соединен с вторым входом первого коммутатора, третий и четвертый входы которого соединены с выводами запоминающего конденсатора, два выхода первого коммутатора объединены с двумя выходами третьего коммутатора и соединены с инвертирующим входом и выходом второго операционного усилителя соответственно, неинвертирующий вход которого соединен с вторым входом BTopoi коммутатора, выход которого соединен с первой токовой клеммой, управляющие входы трех коммутаторов соединены с первым, вторым и третьим выходами блока управления соответственно, выход измерителя отношения соединен через вычислительный блок с входом индикации, упраляющий вход которого соединен с четвертым выходом блока управления, о т л и ч а ю щ е е с я тем, что, с

5 целью упрощения устройства и повышения его точности измерения, в него введены блок резисторов, выполненных по единой технологии, расположенных на одной подложке, содержащий четыре резистора, из10 меритель отношения, выполненный в виде измерителя отношения токов, первый вход которого через образцовый резистор соединен с второй потенциальной клеммой, второй вход измерителя отношения токов

15 через первый резистор соединен с вторым выводом источника ЭДС, с первым выводом которого соединен третий вход измерителя отношения токов, управляющий вход которого соединен с пятым выходом блока уп20 равпения, шестой выход которого соединен с управляющим входом вычислительного блока, первые выводы второго, третьего и четвертого резисторов соединены с выходом второго операционного усилителя, вто25 рые выводы в орого, третьего и четвертого резисторов соединены с третьим, четвертым и пятым входами второго коммутатора соответственно.