Устройство для функционального контроля больших интегральных схем

Иллюстрации

Показать всеРеферат

Изобретение относится к контрольноизмерительной технике и может быть использовано для контроля цифровых интегральных схем. Цель изобретения - расширение области применения за счет возможности контроля других типов микросхем микропроцессорных наборов и повышение достоверности койтроля за счет повышения информативности контроля - достигается введением регистра 17 рода работ , блока 18 управления синхроимпульсами , триггера 19 управления, цифрового компаратора 20, счетчика 21 адресов, элементов 22 и 23 задержки, блока 24 элементов ИЛИ. Устройство также содержит блок 1 микропрограммного управления, блок 2 задания воздействий и реакций, генератор 3 импульсов, узел 4 синхронизации, формирователь 5 временной задержки, блок 6 формирователей формы сигналов, блок 7 формирователей уровней, коммутаторы 8 и 9, блок 10 компараторов, блок 11 сравнения, блок 12 памяти ошибок, элемент 13 задержки , счетчик 14 циклов, выходную и входную шины 15 и 16. Блок 18 управления синхроимпульсами содержит преобразователь 25 уровней, триггер 26, элементы И. 1 з.п.ф-лы, 2 ил. СО с

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 01 R 31/28

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4419060/21 (22) 03.05,88 (46) 30.01.91. Бюл, М 4 (72) Д.А. Ефремов (53) 621,317.799(088.8) (56) Авторское свидетельство СССР . М 1160373, кл. 6 05 В 23/02, 1983.

Авторское свидетельство СССР

М 1179375, кл. G 01 R 31/28, 1984, (54) УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ БОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМ (57) Изобретение относится к контрольноизмерительной технике и может быть использовано для контроля цифровых интегральных схем. Цель иэобрвтения— расширение области применения за счет возможности контроля других типов микросхем микропроцессорных наборов и повышение достоверности коНтроля за счет

„„Я „„1624370 А1 повышения информативности конгроля достигается введением регистра 17 рода работ. блока 18 управления синхроимпульсами, триггера 19 управления, цифрового компаратора 20, счетчика 21 адресов, элементов 22 и 23 задержки, блока 24 элементов ИЛИ. Устройство также содержит блок 1 микропрограммного управления, блок 2 задания воздействий и реакций, генератор 3 импульсов, узел 4 синхронизации, формирователь 5 временной задержки, блок 6 формирователей формы сигналов, блок 7 формирователей уровней, коммутаторы 8 и

9, блок 10 компараторов, блок 11 сравнения, блок 12 памяти ошибок, элемент 13 задержки, счетчик 14 циклов, выходную и входную шины 15 и 16. Блок 18 управления синхроимпульсами содержит преобразователь 25 уровней, триггер 26, элементы И. 1 з,п.ф-лы, 2 ил.

1624370

30

40

55

Изобретение относится к контрольноизмерительной технике и может быть использовано для контроля цифровых интегральных схем.

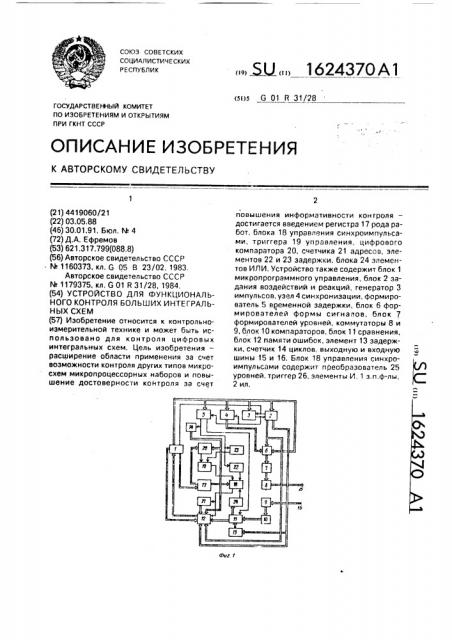

Целью изобретения является расширение области применения за счет возможности контроля других типов микросхем микропроцессорных наборов и повышение достоверности контроля за счет повышения информативности контроля, На фиг,1 изображена функциональная схема предлагаемого устройства; на фиг.2— функциональная схема блока управления син хроим пул ьсами.

Устройство (фиг.1) содержит блок 1 микропрограммного управления, блок 2 задания воздействий и реакций, генератор 3 импульсов, узел 4 синхронизации, формирователь 5 временной задержки, блок 6 формирователей формы сигналов, блок 7 формирователей уровней, коммутаторы 8 и

9, блок 10 компараторов, блок 11 сравнения, блок 12 памяти ошибок, первый элемент 13 задержки, счетчик 14 циклов, выходную и входную шины 15 и 16 соответственно, регистр 17 рода работ, блок 18 управления синхроимпульсами, триггер 19 управления, цифровой компэратор 20, счетчик 21 адресов, второй и третий элементы задержки соответственно 22 и 23 и блок 24 элементов

ИЛИ с соответствующими связями.

Блок 18 управления синхроимпульсами (фиг.2) содержит преобразователь 25 уровк.й, триггер 26, элементы И 27 — 33 с соответс вующими связями.

Блок 1 микропрограммного управления предназначен для хранения программы контроля БИС (больших интегральных схем) и передачи ее в составные элементы устройства, а также для управления процессом контроля, Блок 2 задания воздействий и реакций предназначен для формирования поверочн ых кодов, в состав которых входит информация о входных сигналах для контролируемых

БИС, сигналах управления формирователями формы сигналов блока 6, выходных сигналов (реакциях) БИС, сигналах управления блоком 11 сравнения.

Генератор 3 импульсов предназначен для задания частогы функционального контроля. Узел 4 синхронизации предназначен для формирования импульсных сигналов заданной задержки и длительности для формирователей формы сигналов блока 6.

Формирователь 5 временной задержки служит для формирования импульсов синхронизации, используемых для управления блоком 11 сравнения и записью информации в блок 12 памяти ошибок, причеь временное положение формируемых импульсов задается в соответствии с требованиями нормативных документов на проверяемую микросхему, Формирователь 5 временной задержки представляет собой двухканальное устройство, каждый из каналов которого аналогичен генератору 3 импульсов. Блок 6 формирования формы сигналов предназначен для формирования временной диаграммы входных воздействий для испытуемой

БИС из выходных сигналов блока 2 задания воздействий и реакций и узла 4 с нxpoнизэции. Блок 7 формирователей уровней предназначен для преобразования логических уровней выходных сигналов блока 6 в требуемые для контроля БИС уровни. Коммутаторы 8 и 9 предназначены для подключения испытуемой БИС через выходную и входную шины 15 и 16 к узлам устройства. Блок 10 компараторов служит для сравнения выходных сигналов БИС с ожидаемыми уровнo,ì,è в количестве 2N шт. (по два компэратооа на выход контролируемой БИС для сравнения уровней "0" и "1").

Блок 11 сравнения предназначен для цифрового сравнения выходной информации, поступающей с блока 10 компэрэторов на первую группу входов, с ожидаемой информацией, поступающей ереэ элемент 13 задержки с блока 2 задания воздействий и реакций нэ вторую группу ходов блока 11 сравнения, Блок 12 памяти ошибок предназначен для записи информации о результатах функционального контроля. Элемент

13 задержки служит для задержки информации, поступающей из блокг 2 задания воздействий и реакций нэ блок 11 сравнения, на время задержки информации в тракте: блоки 6--8, выходная шина 15, кон ролируемая БИС, входная шина 16, блоки 9 и 10.

Элемент 13 представляет собой линию задержки.

Счетчик 14 циклов предназначен для подсчета номеров циклов поверочно о функционального теста. Выходная 15 и входная

16 шины служат для связи o6be <тэ контроля (контролируемой БИС) с коммутаторами 8 и

9, Регистр 17 рода работ предназначен для хранения информации о номере цикла функциональ- ого теста, с которого следует проводить анализ результатов функционального контроля, передачи этой информации в цифровой компаратор 20, э также для формирования сигналов управления процессами записи информации в блок 18 управления синхрпимпульсами в зависимости от реэлиэуемого устройством режима работы. Таким образом, регистр 17 рода работ служит для задания режима работы устройства.

1624370

Блок 18 управления синхроимпульсами (фиг.") служит дгя организации трех режимов работы устройства путем пропускания соответствующих импульсов на блок 12 памя1и ошибок и счегчик 21 адресов в зависимости от сигналов управления, поступающих от формирователя 5 временной задержки через элементы 22 и 23 задержки и тоиггер 19 управления

Входы преобразователя 25 уровней образуют группу первых входов блока 18 управления синхроимпульсами, первый вход триггера 26 образует второй вход, а первый и второй входы элемента И 27 являются соответственно-.ретьим и четвертым входами блока 18управления синхроимпульсами.

Преобразователь 25 уровней предназначен для преобразования уровней ТТЛ в уровни

ЭСЛ, элемент И 27 — для пропускания синхроимпульсов с триггера 19 управления и с элемента 22 задержки на объединенные входы элементов И 31-33, служащие для формирования синхроимпульсов, определяющих один из трех режимов работы.

Триггер 19управления предназначен для установки сигнала разрешения на прохождение синхронизирующих сигналов в блок 18 управления синхроимпульсами. Цифровой компаратор 20 служит для сравнения выходных кодов счетчика 14 циклов и регистра 17 рода работ. Счетчик 21 адресов предназначен для формирования адресной информации для блока 12 и мяти ошибок. Элементы 22 и

23 служат для задержки выходных импульсов формирователя 5 временной задержки с целью компенсации задержки сигналов в элементах устройства. Блок 24 элементов ИЛИ предназначЕн для сбора всех выходных сигналов блока 11 сравнения и формирования сигнала общего брака для блока 18 управления синхроимпульсами, управляющего процессом записи информации в блок 12 памяти ошибок.

Устройство работает следующим образом.

В исходном состоянии из блока 1 микропрограммного управления в блок 2 заносится информация о составе функциональных поверочных тестов; в генератор 3 импульсов — о величине периода функционального контроля; в узел 4 синхронизации — о временных параметрах сигналов, подаваемых на входы контролируемых БИС; в формирователь 5 временной задержки — о требуемой величине задержки стробирующего си нала; в блок 6 формирования формы сигналов — о составе и форме сигналов, подаваемых на входы

БИС; а в регистр 17 рода работ -- о начальном адресе анализируемой кодовой после50

45 довательности и режиме работы устройства, При запуске устройства генератор 3 импульсов вырабатывает тактовые ил1пульсы, поступающие на входы блока 2, узла 1. формирователя 5. На каждый тактовый импульс блока 2 задания воздействий и реакций вырабатывается одно кодовое слово разрядностью 4N; 2N разрядов поступает на блок 6 формирователей формы сигналов «2N разрядов поступает через элемент 13 задержки на блок 11 срав ения, Узел 4 синхронизации вырабатывает а каждый тактовый импульс серию импульсов определенной длительности и определенного временного положения.

Блок б формирозателей формы сигналов преобразует ин к.нзл1ацию, поступаюшую на его входы, в импул ьсные последовательности, требуемые для воздействия на входы

БИС. Выходные сигналы с блока б поступают на входы блока 7 фор;1«рователей уровней, которые преобразуют уровни поступающих импульсных последовательностей в требуемые для контроля БИС. Выходные сигналы с блока 7 через коммутатор 8 и выходную шину

15 устройства поступают на объект контроля, выходные сигналы которого через входную шину,16 и коммутатор 9 поступают на блок 10 компараторов, где осуществляется сравнение выход ы>. гигналов с ож 1даел1ыми уровнями. Выходные сигHàëû компараторов блока 10 поступают на блок 11 сравнения, где осуществляется их сравнение с ожидаемой кодовой информацией, Управляющие сигналы и ожидаемая кодовая информация поступают с выхода элемента 13 задержки, компенсирующего задержку тракта: бло.;« "-8, выходная шина

15, объект контроля, входн"".ë шина 1б, блоки

9 и 10. Сравнение осуществляегся в моменты времени, определяемые положением стробирующего импульса, поступающего с формирователя 5 временной задержки.

Выходные сигíà Ibl блока 11 сравнения и блока 2 задания воздействий и реакций поступают на входы блока 12 памяти оши бок, где записываются по соответствующему адресу, формируемому с <етчикол1 21 адресов, по .синхроимпульсу, пос гупающему с выхода блока 18 управления синхроимпульсами. После прохождения всей кодовой комбинации блок 2 воздействий и реакций вырабатывает запрещающий сигнал, который останавливает генератор 3 импульсов и одновременно передается в блок 1 микропрограммного управления как сигнал окончания процесса контроля, Устройство реализует три режима работы, задаваемых регистром 17 рода работ.

1624370

Режим работы устройства с записью информации в каждом такте генератора 3 импульсов осуществляется следующим образом, В регистр 17 рода работ заносится соответствующая информация. Разрешена работа элементов И 28, 31 блока 18 управления синхроимпульсами, и синхроимпульсы поступают на выход блока 18 независимо от результата контроля.

Первый режим обеспечивает запись информации в блок 12 памяти ошибок при каждом такте функционального контроля.

Задание режима осуществляется занесением соответствующей информации в регистр 17 рода работ. Основная особенность данного режима — формирование синхроимпульсов в блоке 18 на каждый импульс, поступающий от формирователя 5 временной задержки через элемент 22 задержки, В результате осуществляется запись в блок 12 памяти ошибок совокупной информации о поступающей на объект контроля информации с указанием координаты (номера цикла). При ограниченном объеме блока 12 памяти ошибок, организации последовательного его заполнения и последующего считывания под управлением блока 1 микропрограммного управления реализуется полное считывание всей информации функционального теста в оперативную память блока 1 для последующего или текущего анализа. Последовательность выбора соответствующих элементов функ. 1онального теста осуществляется последовательным изменением номера цикла в регистре 17 рода с кратностью, равной гпубине ОЗУ блока 12 памяти ошибок.

Данный режим является наиболее информативным, так как позволяет провести полную оценку реакции объекта контроля на входные воздействия при их сопостаелении, Режим работы устройства с записью информации в тех тактах, в которых существует функциональный брак, осуществляется следующим образом.

В этом режиме разрешена работа элементов И 29 и 32, на входы последнего поступает выходной сигнал блока 24 элементов ИЛИ, информирующий о наличии одного или нескольких бракованных разрядов испытуемой БИС. При втором режиме работы устройства блок 18 управления синхроимпульсами формирует сигналы записи информации при наличии неудовлетворительного результата контроля и появления соответствующего сигнала на выходе блока 24 элементов ИЛИ. Задание режима осуществляется через регистр 17 рода работ. В результате использования второго режима е блок 12 памяти ошибок

20

55 заносится информация о забракованном цикле функционального теста. Синхрониэирующий импульс осуществляет запись v. :формации в блок 12 памяти ошибок и переключение счетчика 21 адресов только в тактах с функциональным браком, Достоверность контроля повышается при втором режиме работы устройства зя счет постро:— ния соответствующей модели зависимости брака на цикле от дефектов в БИС, что е принципе реализовано для отработаннь х технологий, Относительно малый объем информации при наличии такой модели вляется достаточным, а производительность существенно повышается, что важно при массовом контроле, Режим работы устройства с записью ин формации в каждом такте до появления сигнала "БРАК" осуществляется следующим образом.

В этом режиме разрешена работэ элементов И 30 и 33, Синхроимпульсы поступают ня выход блока18 до появления сигналя

"БРАК", который взводит триггер 2б, сигнал с инверсного выходе которсго звере цает прохождение импчльroo. В результате е блок памяти ошибок записывается информация, предшествующая появлению брака, Третий режим работы устройства сочетает в себе признаки первого и второго i. жимов, так как при оТ0М осущ:-.стеляет-.я запись информаций е блок 12 памяти ошибок в каждом такте функционального теста до тех пор, пока в каком-либо такте не появится сигнал "Брак" ня выходе блоке 24 элементов ИЛИ. После этсго процесс записи прекращается, и в блоке 12 памяти сшибок хранится инфер лация о забракованном такте и о предыдущих тактах функционяльногс теста, Такой набор информации позволяет локализовать область функциональн:-с теста, е которой произошло эабракоеание, и составить логическую модель условий áoàкования без предеари1ельного математического моделирования. Таким образовал, данный режим обеспечивает повышение достоверности по критериям первого режима, но без избыточности, характерной для него.

В случае, если объект контроля является функционал но годным, через блок 12 памяти ошибок проходит вся информация из блока 2 задания воздействий и реакций и блока 11 сравнения, После окончания функционального контроля в блоке 12 останется информация о последних тактах теста, которую можно не анализировать.

Синхроимпульсы на вход блока 18 поступают с формирователя 5 временной задержки через элемент 22 задер аи, 1624370

О п 3 т

От гер окам

Отр ра17 рода с группой третьих входов блока памяти ошибок и с входами первого элемента задержки, группа четвертых входов блока памяти ошибок соединена с выходами счетчика адресов, а группа пятых входов — с группой вторых выходов блока микропрограммного управления, группа третьих выходов которого соединена с входами регистра рода работ, группа первых выходов которого соединена с группой первых входов блока управления синхроимпульсами, второй вход которого соединен с выходом блока элементов ИЛИ, входы которого соединены с группой вторых выходов блока сравнения, третий вход блока управления синхроимпульсами соединен с выходом триггера управления, четвертый вход — с выходом второго элемента задержки, а выход — с шестым входом блока памяти ошибок и выходом счетчика адресов, первый вход триггера управления соединен с входом третьего элемента задержки, второй вход — с выходом цифрового компаратора, группа первых входов которого соединена с группой вторых выходов регистра рода работ, второй выход формирователя временной задержки соединен с входами счетчика и второго и третьего элементов задержки, а выходы счетчика соединены с группой вторых входов цифрового компаратора и группой седьмых входов блока памяти ошибок.

2. Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок управления синхроимпуль5 сами выполнен на преобразователе уровней, триггере и семи логических элементах

И, причем входы преобразователей уровней образуют группу первых входов блока управления синхроимпульсами, первый вход

10 триггера образует второй вход, а первый и второй входы первого элемента И образуют соответственно третий и четвертый входы блока управления синхроимпульсами, первый, второй и третий выходы преобразова15 теля уровней раздельно соединены с первыми входами второго, третьего и четвертого элементов И, вторые входы которых соединены с четвертым выходом преобразователя уровней, а выходы раздельно сое20 динены с первыми входами пятого, шестого и седьмого элементов И соответственно, вторые входы которых соединены с выходом первого элемента И, а выходы объединены и образуют выход блока управления синхроим25 пульсами, третий вход шестого элемента И соединен с первым входом триггера, второй вход которого соединен с выходом четвертого и вторым входом седьмого элементов И, а выход — с третьим входом седьмого элемента И.