Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано для автоматизированного контроля и диагностики неисправностей в цифровых блоках радиоэлектронной аппаратуры и ЭВМ. Целью изобретения является расширение функциональных возможностей устройства за счет расширения класса проверяемых неисправностей и повышения частоты тестирования. С этой целью а устройство , содержащее генератор тактовых импульсов, два счетчика, первый триггер, одновибратор, элемент И, дешифратор, генератор псевдослучайных последовательностей , группу сигнатурных анализаторов, блок сравнения, демультиплексор и группу шифраторов состояния, введены дое группы элементов И, группа элементов ИЛИ, элемент задержки и второй триггер. 2 ил.

СОЮЗ CORETCKVIX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 F 1/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (111 : 1:

g ь C.Ú ...

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АЬТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4429675/24 (22) 23.05.88 (46) 30.01.91. Бюл. М 4 (72) В.И.Заславский (53) 681.3 (088.8) (56) Авторское свидетельство СССР

М 817721, кл. G 06 F 11/22, 1979.

Авторское свидетельство СССР

М 1142837, кл. G 06 F 11/26, 1985. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано для автоматизированного контроля и диагностики неисправностей в цифровых

Изобретение относится к цифровой вычислительной технике и может быть использовано для автоматизированного контроля и диагностики неисправностей в цифровых блоках радиоэлектронной аппаратуры (РЭА) и ЭВМ.

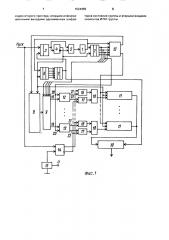

Цель изобретения — расширение функциональных воэможностей устройства эа счет расширение класса проверяемых неисправностей и повышения частоты тестирования, На фиг,1 представлена структурная схема устройства; на фиг.2 — приведена схема шифратора.

Устройство для контроля логических блоков содержит (фиг,1) генератор 1 тактовых импульсов, первый счетчик 2, первый триггер 3, одновибратор 4, элемент И 5, второй счетчик 6, дешифратор 7, генератор 8 псевдослучайных последовательностей, который соединен с контролируемым блоком

9, кроме того, устройство содержит блок 10 Ы 1624459 А1 блоках радиоэлектронной аппаратуры и

Э В М. Цел ью изобретения является расширение функциональных возможностей устройства за счет расширения класса проверяемых неисправностей и повышения частоты тестирования. С этой целью в устройство, содержащее генератор тактовых импульсов, два счетчика, первый триггер, одновибратор, элемент И, дешифратор, генератор псевдослучаиных последовательностей, группу сигнатурных анализаторов, блок сравнения, демультиплексор и группу шифраторов состояния, введены две группы элементов И, группа элементов ИЛИ, элемент задержки и второй триггер. 2 ил.

Ф

l сравнения, группу сигнатурных анализаторов 11, шифраторы 12 состояний, демультиплексор 13, второй триггер 14, элемент 15 задержки, первую группу элементов И 16, вторую группу элементов И 17, элементы

ИЛИ 18 и имеет информационный вход 19 шифратора состояний (информационный вход устройства), вход 20 синхронизации шифратора состояний, первый выход 21 д шифратора состояний, второй выход 22 шифратора, Шифратор 12 (фиг.2) содержит компаратор (1) 23, компаратор (О) 24, элемент И 25, элемент И 26 с одним инверсным входом.

При этом счетный вход второго триггера

14 соединен с выходом "Пуск" устройства, а установочный вход триггера 14 — с выходом элемента 15 задержки. Прямой выход триггера 14 соединен с первыми входами элементов И 16, а инверсный выход соединен со вторыми входами элементов 17. Первый выход каждого шифратора 12 группы под1624459

10 ключен к второму входу одноименного элемента 16 группы, второй выход шифратора

12 группы подключен к первому входу одноименного элемента 17 группы, выходы каждого из элементов 16 и 17 соединены со входами одноименного элемента 18 группы.

Устройство работает следующим образом.

При включении питания с помощью элемента 15, подключенного к установочному входу триггера 14, этот триггер устанавливается в нулевое состояние. Элемент задержки реализуется по известной схеме и представляет собой RC-цепочку.

Обычно в качестве резистора R используегся делитель, один из выводов которого подключается к источнику напряжения О, другой к корпусу (шине нулевого потенциала). Средняя точка делителя подключается к установочному входу триггера. К этому же входу подключается емкость С, а второй ее контакт подключается к корпусу. Коэффициент деления выбирается таким образом, чтобы в средней точке уровень напряжения соответствовал уровню лог. "1".

При появлении на обоих входах элемента 5 сигналов 1 на его выходе формируется сигнал, запускающий генератор 1. С выхода генератора 1 сигнал подается на информационные входы первого и второго счетчиков

2 и 6 и демультиплексора 13. С выхода первого счетчика сигналы подаются на адресный вход демультиплексора 13 и на тактовый вход блока 9.

По сигналу со второго информационного выхода демультиплексора 13 сигнал поступает на синхровход генератора 8, на выходах которого, являющихся выходами устройства, формируется набор теста. Этот набор теста подается на информационные входы проверяемого блока 9. С выходов блока 9 сигналы подаются на соответствуюцие входы блока 9, являющиеся информационными входами шифраторов 12. На синхровходы 20 шифраторов 12 поступает сигнал с одного из разрядов счетчика 2.

Выбор номера выхода счетчика 2, к которому следует подключить шину, подающую разрешающие сигналы на синхровходы 20 шифраторов 12, определяется из расчета промежутка времени, необходимого для шифрации бита информации (поступающего на входы 19 шифраторов 12) в два бита на информационных выходах 21 и 22.

Логические сигналы с информационного выхода 21 шифратора 12 через открытый элемент 16 и элемент 18 подаются на информационный вход блока 11 (группы сиг чтурных a an aaropoe). По синхросигналу

55 с первого информационного выхода демультиплексора 13 логические сигналы эаписываются в сигнатурный анализатор 11.

Второй счетчик 6 ведет подсчет количества наборов теста, формируемых генератором 8. Информация с его выхода подается на вход дешифратора 7.

Частота импульсов синхронизации на обоих выходах демультиплексора 13 (в отличие от известного устройства) практически одинакова. Только синхросигналы с первого выхода задержаны по отношению к синхросигналам с второго выхода на время, равное задержке прохождения логических сигналов от какого-либо иэ выходов контролируемого блока 9 к информационному входу соответствующего сигнатурного анализатора 11.

После подачи последнего тестового воздействия срабатывает дешифратор 7, который переводит первый триггер 3 в исходное состояние, В сигнатурных анализаторах 11 фиксируется значение сигнатуры, отражающее информацию о логических сигналах на выходе контролируемого блока 9. По сигналу от. дешифратора 7 разрешается индикация результатов сравнения в блоке 10 значений сигнатур с сигнатурами, полученными в результате проверки исправного однотипного блока (блок индикации на структурной схеме фиг,1 не показан), На этом первый цикл проверки блока 9 заканчивается. В этом цикле проверяются неисправности, приводящие к изменению значений логических сигналов "0" и "1" на выходах блока 9.

Далее следует второй цикл проверки блока 9 на наличие неисправностей, приводящих к искажению информации о третьем состоянии на выходах этого блока.

По сигналу "Пуск" триггер 14 устанавливается по счетному входу в нулевое состояние и с его инверсного выхода разрешающий сигнал "1" подается на входы

22 элементов 17. Дальнейшая работа устройства происходит так же, как и в первом цикле проверки. Только во втором цикле на информационные входы сигнатурных анализаторов 11 поступает информация о третьем состоянии выхода блока 9. Сигнал с каждого иэ выходов блока 9 преобразуется шифратором 12 и с выходов 22 через элементы 17 и 18 подается на информационный вход анализатора 11.

По завершению второго цикла работы устройства в анализаторах 11 фиксируются сигнатуры, отражающие информацию о третьем состоянии выходов блока 9.

Рассмотрим работу шифратора 12 (фиг.2) при поступлении на его информаци1624459 онный вход 19 логического сигнала (U), С выхода проверяемого блока он поступает на вход компаратора 23 и компаратора 24 (в качестве компаратора может быть, например, использована микросхема 521 САЗ).

Компаратор 23 настраивается на минимальный (по техническим условиям) уровень (U>) напряжения 1 (при положительной логике), а компаратор 24 — на максимальный уровень (02) напряжения О. Если поступающий логический сигнал имеет уровень напряжения — 1, т.е, U > Ui, то на выходах обоих компараторов формируется лог, "1", Если же поступающий логический сигнал U имеет уровень напряжения — О, т.е. 0 < Ug, то на выходах обоих компараторов формируется лог. "О". Если контролируемый выход блока

9 находится в третьем состоянии, то уровень напряжения U этом выходе будет

02

1, то с выходов компараторов 23 и 24 на второй и третий вход элемента 25 и 26 будет соответственно поступать сигнал "0" или

"1", и при подаче синхросигнала с выхода счетчика 2 на вход 20 шифратора 12 и соответственно на первый вход элемента 25 и

26, на выходе 21 будет сформирован сигнал

"О" или "1" соответственно, ча выходе же 22 будет формироваться только сигнал "0".

Если же сигнал U по уровням напряжений будет соответствовать третьему состоянию выхода блока 9, то на второй и третий вход элементов 25 и 26 будет соответственно подаваться сигнал "О" и "1". При наличии синхросигнала на входе 20 на выходе 21 будет формироваться сигнал "0", а на вь ходе 22 — "1", Следовательно, на выходе 22 шифратора 12 будет формироваться сигнал "1" только в том случае, если контролируемый выход блока 9 находится в третьем состоянии. 4

Устройство для контроля логических блоков, содержащее генератор тактовых 5 импульсов, два счетчика, первый триггер, одновибратор, элемент И, дешифратор, генератор псевдослучайных последовательностей, группу сигнатурных анализаторов, блок сравнения, демультиплексор и группу 5 шифраторов состояния, причем установочный вход первого триггера является входом пуска устройства, выход дешифратора подключен к входу сброса первого триггера и

Формула изобретения управляющему входу блока сравнения, выход которого является выходом индикации устройства, выход превого триггера соединен с входом одновибратора и первым вхо5 дом первого элемента И, второй вход и выход которого подключены соответственно к инверсному выходу одновибратора и входу генератора тактовых импульсов, прямой выход одновибратора соединен с уста10 новочными входами первого и второго счетчиков, генератора псевдослучайных последовательностей и сигнатурных анализаторов группы, выходы которых подключены к одноименным информационным входам

15 блока сравнения, выход генератора тактовых импульсов соединен со счетными входами первого и второго счетчиков и информационным входом демультиплексора, выход первого счетчика подключен к

20 адресному входу демультиплексора и является выходом устройства для подключения к тактовому входу контролируемого блока, один из разрядов выхода первого счетчика соединен с синхровходами шифраторов со25 стояния группы, информационные входы которых являются входами устройства для подключения к выходам контролируемого блока, выход второго счетчика подключен к входу дешифратора, первый информацион30 ный выход демультиплексора соединен с синхровходами си H" óðíûõ анализаторов группы, а второй информационный выход демультиплексора подключен к синхровходу генератора псевдослучайных последова35 тельностей, выход которого является выходом ус ройства для подключения к информационному входу контролируемого блока,отличаю ще еся тем,что,с целью расширени функциональных возможно10 стей устройства за счет расширения класса проверяемых неисправностей и повышения частоты тестирования, оно содержит две группы элементов И, группу элементов

ИЛИ, элемент задержки и второй триггер, 5 счетный вход и установочный вход которого соединены соответственно с входом пуска устройства и выходом элемента задержки, вход которого подключен к шине нулевого потенциала, первые и вторые входы и выхо0 ды элементов И первой группы соединены соответственно с прямым выходом второго триггера, первыми информационными выходами одноименных шифраторов состояния группы и первыми входами

5 одноименных элементов ИЛИ группы, выходы которых подключены к информационным входам одноименных сигнатурных анализаторов группы, а первые и вторые входы и выходы элементов И второй группы соединены соответственно с инверсным вы1624459 ходом второго триггера, вторыми информационными выходами одноименных шифраторов состояния группы и вторыми входами элементов ИЛИ группы.

1624459

Составитель Г,Виталиев

Техред М.Моргентал КоРРектоР Т.Палий

Редактор А.Долинич

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 191 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5