Устройство для отладки программ

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для отладки программ микроЭВМ и микропроцессорных устройств. Цель изобретения - повышение достоверности контроля хода программы. Устройство для отладки программ содержит схему сравнения разрядов адреса, мультиплексор магистралей, первый дешифратор, формирователь короткого импульса, первый триггер, регистр адреса, второй дешифратор, селектор управляющих сигналов, регистр управляющих сигналов, вычитающий счетчик импульсов, селектор контроля, регистр режима контроля, второй триггер, элемент ИЛИ. Устройство автоматизирует процесс отладки программ за счет того, что позволяет контролировать очередной адрес операндов в текущей команде, задавать несколько адресов и условий останова . 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю G 06 F 11/28

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4430389/24 (22) 25.05.88 (46) 30.01.91. Бюл. М 4 (71) 20-й Государственный подшипниковый завод (72) А.Ю.Лунев, B.Þ.Ëóíåâ и И,Л.Бабынин (53) 681.3 (088.8) (56) Авторское свидетельство СССР

М 1100627, кл, G 06 F 11/26, 1984.

Авторское свидетельство СССР

М 1223236, кл. G 06 F 11/28, 1986, (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ (57) Изобретение относится к вычислительной технике и может быть использовано для отладки программ микроЭВМ и микропроИзобретение относится к вычислительной технике и может быть использовано для отладки программ микроЭВМ и микропроцессорных устройств в реальном масштабе времени.

Цель изобретения — повышение достоверности контроля хода программы.

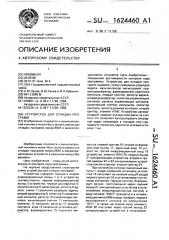

На чертеже представлена структурная схема устройства для отладки программ.

Устройство содержит первый и второй информационный входы 1 и 2 устройства соответственно, первый информационный выход 3 устройства, первый дешифратор 4, мультиплексор 5 магистралей, регистр 6 адреса, схему 7 сравнения разрядов адреса. второй дешифратор 8, селектор 9 управляющих сигналов, регистр 10 управляющих сигналов, вычитающий счетчик 11 импульсов, селектор 12 контроля, регистр 13 режима контроля, вход 14 начальной установки устройства, формирователь 15 короткого им„„ Ы„„1624460 А1 цессорных устройств. Цель иэобретения— повышение достоверности контроля хода программы. Устройство для отладки программ содержит схему сравнения разрядов адреса, мультиплексор магистралей, первый дешифратор, формирователь короткого импульса, первый триггер, регистр адреса, второй дешифратор, селектор управляющих сигналов, регистр управляющих сигналов, вычитающий счетчик импульсов, селектор контроля, регистр режима контроля, второй триггер, элемент ИЛИ. Устройство автоматизирует процесс отладки программ за счет того, что позволяет контролировать очередной адрес операндов в текущей ком; нде, задавать несколько адресов и условий останова. 1 ил, пульса, первый триггер 16, второй информационный выход 17, адресный вход 18 устройс-ва, третий информационный вход 19 устройства, элемент ИЛИ 20, первый выход

21 синхронизации устройства, второй и третий выходы 22 и 23 синхронизации устройства соответственно, второй триггер 24.

При включении питания одиночный импульс с входа начальной установки устройства 14 поступает на нулевой вход (R-входа) первого триггера 16 и устанавливает его нулевое состояние. Первый триггер 16 формирует сигнал, поступающий через первый выход 21 синхронизации устр йства в отлаживаемую микропроцессорную систему в виде сигнала "WAIT" (ожидать) и в отлаживающую миниЭВМ в виде нулевого первого маскируемого сигнала на прерывание

"INT1", а также на второй вход элемента

ИЛИ 20 поступает через третий выход 23 синхронизации устройства в отлаживаю1624460

1520

50 ;.Ic миниЭВМ е виде второго маскируемого сигнала на пперыеание "!МТ2".

Через первый и фсрмацио;IHblln вход 1 ус гройстза на первый вход первого дешифратора 4 поступают сигналы шины управления стлажиеающей миниЭВМ. На второй вход первого дешифратора 4 через адресный влсд 18 устройства поступают младшие разряды адресной шины отлаживающей миниЭ ВМ.

При поступлении :а первый дешифрагор 4 coen";óïности сигналов разрядое адресз сиг>.алов управления "Запись е устройство ввода-еь;вода", "Чтение устрсйс е ввода-вывода" L зависимости от ко а, поступившего на вход первого дешифратора 4, возбу,кдается один из выходов первого дешифратсра 4, Поступа ощий код на выходе первого дсшифрагора 4 может быть десяти типов, В соиTe""TcTеии с описанной ниже работой устройс.еа для отладки программы обозначим каждый из:адов символами а, Ь, с, d, е, f, g, Ь,! ). При поступлении на вход первого

;,ешифсатора 4 кодов а, Ь, с возбуждается состее-ственно первый, второй, третий выходь1 пеоеого дешифратора 4, которые соединены ",оо1ветсте. нно с первым, вторым, .ретьи; входами управления мультиплексора 5 магис;ралей. При наличии кодов а, Ь, с к;. Rxop, первого дешифратора 4 му,Iчиплексср 5 магистралей обеспечивает коммут,"цию соответственно второго ин —,рмац1 cJHHого входа 2 устройства, третье, I .. .; 1жрмац, снно-î входа 19 усгройс-.еа, па реог< ин формационного выхода 3 устройства Hà второй и, фсрмацион -IblA выход 17 уст .ойс тел, Код <, возбуждает соответственНо етеергый выход первого дешифратора

4, КО Ср „I-, СовдИНЕН ССОГЕЕГСтВЕННО С чЕтеертым ехадом управления мультиплексора = ма;истра; ей.! lðè;.ànè÷èè кода d на входах первого дешифратсра 4 мультиплексор

5 м .гистралсй обеспечивает коммутацию информационного выхода 17 устройства соо еетсгеенно -Ia первый информационный выход 3 ус-.ройства.

Код е еозбуждает пятый выход первого дешифратора 4, который соединен с входом формирователя 15 короткого импульса. Код е, запуская формирователь 15 короткого импульса, переводит первый триггер 16 по установочному входу (S-вход) в единичное состояние, снимая тем самым сигнал

"Ф/А Т" с первого выхода 21 синхронизации усссйс еа и осуществляя автоматический запуск отлаживаемой микропроцессорной сис емы посге останова. Годы f, g, h, i возбуждают соответственно ILpcTGLR седьмой, восьмой девятый Rblходы первого дешифратора 4, которые подключены к входам разрешения записи соответственно регистра 6 адреса, регистра 10 управляющих сигналов, вычитающего счетчика 11 импульсов, регистра 13 режима контроля. При наличии кодов f, g, h, i на входе первого дешифратора 4 последний сигналами на шестом, седьмом, восьмом, девятом своих выходах разрешает запись информации из второго информационного выхода 17 устройства соответственно в регистр 6 адреса, регистр 10 управляющих сигналов, вычитающий счетчик 11 импульсов, регистр 13 режима контроля.

Ксд J возбуждает десятый выход гервого дешифратора 4, который подключен к тактовому входу второго триггера 24. При наличии кода J на входе первого дешифратора 4 последний сигналом на десятом своем выходе, поступающим на тактовый вход (С-вход) второго триггера 24, разрешает запись информации из линии старшего разряда второго информационного выхода 17 устройства во второй триггер 24 через его информационный вход(0-вход).

Регистр 6 адреса предназначен для сохранения адреса очередной контрольной точки о1лаживаемой программы.

Схема 7 сравнения разрядов адреса вырабатывает нулевые сигналы при совпадении старших и младших разрядов адреса, соответственно поступающих из регистра 6 адреса (разряды адреса очередной контрольной точки отлаживаемой программы) и из гтсрого информационного входа 2 устройства (разряды текущего адреса обращения).

При поступлении на второй дешифратор 8 совокупности сигналов; разрядов управления из отлаживаемой микропроцессорной системы через третий информационный вход 19 устройства и сигналое со схемы 7 сравнения разрядов адреса в зависимости оТ кода, поступающего на входы второго дешифратора 8, возбуждается один из четырех выходов второго дешифратора 8.

Поступающий код может быть четырех типов и соответствует четырем сйтуациям в отлаживаемой микропроцессорной системе: чтение памяти с определенным адресом, запись в память с определенным адресом, чтение устройства ввода-вывода с определенным адресом, запись в устройство ввода-вывода с определенным адресом, и сооТВ8ТсТВ8НН0 этому возбуждает сигнал на первом, втором, третьем и четвертом выход: х второго дешифратора 8.

Под воздействием комбинации сигналов, хранящейся в регистре 10 управляющих сигналов, селектор 9 управляющих

3624460 сиг(алов проп,ск:)ет только;,дин опредеЛЕННЫЙ оаЗГ ЯД> УГ)РаРЛЕГ)(1Я С ОЕГьЕ! О ИН формациоHHolo всда .9 устоойства на счетный вход в(чита)ое:его счег ика 11 1мпульсов, который iio входу предустанова ус- 5 танавливается н подсчет определенного числа импул.сов в пределах от 1 10 2", где п — число двоичных са )рядов входа предустанова вычитающего счетчика 1, импульс0В. При поступлении нз вычитаюший 10 счетчик 11 импульсов зад; iiíîTî )(оличестг>а импульсов рззряда у; раьг - ния пропускаемого селеKTGðoì 9 упрaeë÷foif,f х сигначoR с третьего информационного входа 19;стройства, вычитающий счетчик 11 ил пульсов 15

ВОЗбуждаЕт СИГНаЛ, Поегуи,»ощ 1!1 На СИНХронизирующий вход (С-вход) первого триггера 16, На инфсрмациоГ 1ый вход ()3-вход) первого триггера 16 подаегся лог, "0". Г)ри поступлении сигнала на ..и )хро.".Изиру о- 20 щий вход ((-ьхсд) первого Ti )ггг Г а 16 последний уста навл ива Гc 3 и; Чевсе состояние, вырабатывая!. гнал " )1(АI "для

Отлаживаемсй млкроппоцсc(. орной системы и пергый нулевой маскируемый сигнал 25

"INT1" для отлаживающей миниЭБМ fia первом выходе?1 синхронизации устройстВа.

ПОД Зс Зде 1СТГ>ие)4 Kof46I1H 3(I 1Л Си) Нс3лов, хранящейся в регистре 13 р".жима кон- 30 трс. я, СЕЛЕКтар 1? ro)) р "Г>я Чр()П>>схаст нулевой СЛГГ ал с одного лз ч") . ..I,)ех Bl,ходов второ(о дешифг.-вторя 8 i)a )epвый Bх(од элеi4eHTa И,г)И 20. С выхода .iepf 0.-0 тг>иггера

;6 посту-:a>BT нулевой сигнал Hз второй Bход 35 элел1ента Е)чИ 20 Элемент ИЛИ 20 только при наличии нулевых сигналов На c:)oèõ Входах выраба -:BaeT Hy) евои втопои мзскируемый сигнал прерывания "! NT2" для с>тла)киьающей миниЭР;, на тре. ье(4 выхо- 40 де 23 синхронивации устрс1с(ва.

Бторол i ригге,; 24 вь раба > ыв ет сигнал

"Блокирс вка i.laìÿòè" На второ.4 выходе 22 синхронизации стройства для о(гаживающей микрспроцеf. ñîpíoé си темы, блокиру- 45

Ощий обращение к памяти Ilaлажилаемой

MI4f(pof-pope. copHoI4 cvc емы.

Для отладки псс-ра!411 к устройству подсоедин яет«я минн "-, B M . Г )лаж ива >ма я микропроцессорная системз работает сле- 50

Дую(цим сбразом Адресная )лина миниЭБМ подсоединяется к а„оесному входу 18 устройства, шина управления к первому информационному входу " устройства, шиНа данных — Ko BTopo)4y !1Hфсрмационнсму 55 выходу 17 устройства, г)ин(я сигнала нл первый маскируемь и зч)) рос прерывания

"ihIT1" — к первому .".,) *:Оду 21 с 1)Ir f",0H(4aaции устройства. линия сигнала на второй

МаСКИруЕЛ1Ый ЗасрОС п(;ЕрЫВЛЧИя INT2" — К третьему вылсду 23 сиH сзниз=- „. и,(Tpo!4ства, линия си(налз на-a::.i,о.. ус;.н;зки— к входу 14 начальной у:-а,-:сг;(уст".)..с-ва.

Адресная B!ина От. =.:-:Игаем,.зй микропроцессорной систе)1ы l)c;,-с .Д(я "Tcÿ ко второму инфор," ацио . )о..1у в).оду 2 усгройства, шина управления пслсоединяется к третьему инфсрмзционному входу 1)9 устРсйСтВа, ШИНа Да 1 1ЫХ вЂ” V ЕРВС 4, ИНфОРл1ацис HH014ó Г)ых ду 3 ус,"и. с В;!, линия

cvãнзла )(1/АIT" — к пе, Ому выходу 21 син;:р(низации устр йс, вз л)4ния сигнала

"Ьлокиповка памя 1" — Yc BTGI)of4у выходу

?2 СИНХрОH(4ЗацИИ (гстрсй)СТВа. с)ормула изобпетения

\ ТРОЙ(.TB0 ДЧЯ 0T))a. f l1 Г Рогсга) ) 4, СОд>с>р . : (Е, Уг>), -г г>. >, с ).Л >(.,Д. ° .3 Д-3 са, мул,.ип ек".О .,1а °; —: ), 3!1, f)r.р;)ый дес ифратср, (1>ор)4ИГ)огаг«.:,,;;, Qofo имг)ульса, первый тси- р. f;!) " ..1 а,;;,ес))ый

ВХОД УCTPoй. »a ДЛ : -:;..;.;Г I(., )ИНЕ адрЕСЗ Отл,".ж ..;« i.! — ..l г1 С. =.,,».i и = ПЕрЛ„)М ИНфООЛ1;),). "() М Д3!4 Г с-.(.-ОГО дЕШ.)фсатОра, ЗтОрс И):".всрЛ1,"., О -:,i;; ВХОД

КОтОООГО СОЕДИ)): = ПЕРВЫ .)нфСРЛ1аЦИСННЫМ ВХОДОМ VCT pã>I)ã òf)a гг ЛЯ Г>(д)(Л) ГГ>>внисс К

ШИНЕ УПРа,Ч(3НИЯ ОтЛЗ .;FBÞÙB:13RM. ВтОро.: информ"-.цис I,II,.II B) nд . 1ройс i Ba дгя

)10(1К>-)IО IBЧИЯ К L И)-)Е с>ДГ.BСЛ,)ТЛа)),>1(3ЛК) Д» Й ) P I . СОСДИ) -.;; .. . П;, 1;:фСРл1 цис), !)xo, Ом a(.,С(са

f".àãi4icTpагей и пер -!-,4,гх,) ..с 4)) сравнен))я разрядо(3 ()дГ>с сз, T . и:,:;) „3;,!1ОГ)НЬ Й г)ХОД УС"гР»I1CTRB ДЛ -) f) :.",,: (Г!Ннс> К шине управлгн-)sI ОT. (():;,). )()()и " = :1 ссеДИгier C BTOIQI> . 4 " «ollf >Г),,1 ) )! .:(4 Г>ХО .1 л1(льти —;лвкСООЛ f). ã; (::); . ".. (. F-i(1 инфо,>Ы:) 0 ИОННЫ 3 г) .>) ЛГ)д уСТ р ).1С > В. ДЛЯ ПОД

Кг)ЮЧЕнис) К ШИН .. )>Н>У ОГЧ - . Сс В)40Й

Э Е ", 1 со "динен c I () i ь.1м 11нфсг I: 3ционным

ВУОДСгм f4 ËÜòÈÏë":(,;)а Мс! .:Т 3» . ПЕPВЫЙ, ВТОРОЙ, TP)e1l 1 И сс I I.. Р) Ы,) f Ы -,:)ДЫ первого де пифр;.>ора соеди>1«,i СОО)()етСТВЕH I,с С О!(1 )И" с )iIЫ. 111 ;) )I,Я ; I l,(1Л1И

ВХОДаМИ МУ. ЬТ11Г)Л".Ксг>Р i г. З! ИС) l "Г(й), f3bl хсд которсгэ соедин вн с (;ОI)f- ";,;н орл1аЦИО fHI>lf4 ВЫ/O 3 )ги )(С Р:ОЙС Гва ДЛЯ

ПОДКЛ)О ЕНИЯ К III 1)i., Hi!i . Отлзгч()ваЕМОЙ

ЭБМ, п«тыи f! лад ". Г«:О с, г- .;и, paTopa соединен черсз 1(ч .1,,.)()в".-Гль коро) кого

И!4П )f". ;-". С (.Дпс>(1-> : ОД ;".>> I: > C Pl1l

Гера, f ó.)åB0() лс),,).. „)0 ., „Г; р-. соединен с входом н, чal) ьн, y т--ilовки устройства, информацион) ) I!1!:. Од первого триггера соединен с в . но.- ),лево-с . отанциала устрсйства, 0 T fл и ч с3 к) ш е е с я тем, ЧтО, С Ц,ЛЬЮ П",ЫШ«нис,лсс . ".I "),(".— "КОНТРОЛ 3 ХОГ ) ПС>.)ГB>i "1. ) I, " "Г . И >.,(«.— ны регистр адреса,вторс, и.:и, раiÎp, селектор управляя . 3) х -.! . ), ". Г. .Гистр

1624460

18

Составитель А.Цыбин

Редактор А.Долинич Техред М.Моргентал Корректор Т П ий

Заказ 191 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4(5

Производственно-издательский комбинат "патент", r Ужгород, ул.Гагарина, 101 управляющих сигналов, вычитающий счетчик импульсов, селектор контроля, регистр режима контроля, второй триггер, элемент

ИЛИ, причем информационный вход регистра управляющих сигналов, вход предустанова вычитающего счетчика импульсов, информационный вход регистра режима контроля соединены с вторым информационным выходом устройства для подключения к шине данных отлаживаемой ЭВМ, старший разряд второго информационного выхода устройства соединен с информационным входом второго триггера, шестойдевятый выходы первого дешифратора соединены соответственно с входами разрешения регистра адреса, регистра управляющих сигналов, вычитающего счетчика импульсов, регистра режима контроля, десятый выход первого дешифратора соединен с тактовым входом второго триггера, выход регистра адреса соединен с вторым входом схемы сравнения разрядов адреса, выход которой соединен с первым входом второго дешифратора, первый информационный вход устройства для подключения к шине управления отлаживаемой ЭВМ соединен с вторым входом второго дешифратора и с информационным входом селектора управляющих сигналов, выход регистра управляющих сигналов соединен с входом управления селектора управляющих сигналов, выход которого соединен со счетным вхо5 дом вычитающего счетчика импульсов, выход вычитающего счетчика импульсов соединен с тактовым входом первого триггера, прямой выход первого триггера соединен с вторым входом элемента ИЛИ и

10 является первым выходом синхронизации устройства для подключения к входу первого маскируемого запроса прерывания отлаживаемой ЭВМ и к входу ожидания отлаживаемой ЭВМ, первый, второй, третий

15 и четвертый выходы второго дешифратора соединены соответственно с одноименными информационными входами селектора контроля, выход которого соединен с первым входом элемента ИЛИ, выход которого

20 является третьим выходом синхронизации устройства для подключения к входу второго маскируемого запроса прерывания отлаживающей ЭВМ, выход регистра режима контроля соединен с входом управления се25 лектора контроля, выход второго триггера является вторым выходом синхронизации устройства для подключения к входу блокировки памяти отлаживаемой ЭВМ.