Декодер

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации. Декодер осуществляет мажоритарно-логическое декодирование с использованием в качестве дополнительных проверочных символов кода информационных символов соседних каналов, что повышает достоверность декодирования. Декодер содержит регистр сдвига, каналы цифровой обработки с блоками сумматоров по модулю два и мажоритарным элементом, каждый блок считывания на элементах И. Кодер содержит регистр сдвига и сумматор по модулю два. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 М 13/00

ГОСУДАPСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4627289/24 (22) 26,12.88 (46) 30.01.91. Бюл.:М 4 (72) В.В.Калмыков, А.С.Косолапов, В.Ф.Тимошенков, С.И.Наумкин, С.С.Юдачев и В,М,Лисичкин, (53) 621.394(088.8) (56) Пенин П.И., Филипов Л.И. Радиотехнические системы передачи информации. M.:

Радио и связь, 1984, с.188 — 189, рис.8,2, 8,3.

Журавлев В.И. Поиск и синхронизация в широкополосных системах. M.: Радио и связь, 1986, с,97 — 99, рис,3.7. (54) ДЕКОДЕР

Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации.

Цель изобретения — повышение достоверности декодера.

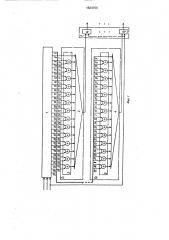

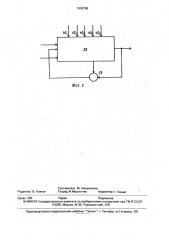

На фиг.1 представлена функциональная схема декодера; на фиг,2 — фрикционная схема кодера.

Декодер содержит (фиг.1) регистр 1 сдвига, каналы 2 цифровой обработки, каждый из которых выполнен на блоке 3 сумматоров по модулю два и мажоритарном элементе 4, блок 5 считывания, выполненный на элементах 6 И и выходы 7 — 37 регистра 1 сдвига, Кодер содержит (фиг,2) регистр 38 сдвига, сумматор 39 по модулю два и информационные входы 40 регистра 38.

Для примера рассмотрим декодер (фиг.1), содержащий и = 5 каналов 2 цифровой обработки. При этом регистр 1 содержит

2 — 1 = 31 ячеек, выходы которых подключе5 Ы 1624700 А1 (57) Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации. Декодер осуществляет мажоритарно-логическое декодирование с использованием в качестве дополнительных проверочных символов кода информационных символов соседних каналов, что повышает достоверность декодирования.

Декодер содержит регистр сдвига, каналы цифровой обработки с блоками сумматоров по модулю два и мажоритарным элементом, каждый блок считывания на элементах И, Кодер содержит регистр сдвига и суммато)» по модулю два. 2 ил. ны к сумматорам по модулю два блока 3 i-го канала 2, i = 1, 5, согласно выражениям

Bi = Bl ai = а +16+ ан-о а =. а +7+ ai+22

Bl = а;..1+ а +1В а = Bi+6+ Bi+27 Bl = BI+13+a i+14

ai = ai+2+ ai+5 ai = а +3+ а +29 ai = а +26+ Bi+26

ai = Bi+4 + аН.10 Bi = Bi+12 +а)+23 Bl = Bi+21+Bi+23

ai = аН-В+ а +20 ai = al+15+ ai+24 ai = а +11+ а +19 где а +1 — выход (!+Д-й ячейки регистра 1, причем индексы складываются по модулю

2" — 1 =31.

Декодер осуществляет декодирование кода М-последовательности, образованной на основе многочлена f(x) = х + х + 1 и формируемой кодером (фиг,2), Устройство работает следующим образом.

Двоичные канальные символы, поступающие на информационные входы 40 кодера (фиг.2) управляющим сигналом цикловой

1624700

20

30

50! г r синхронизации записываются в ячейки регистра 38, По окончании импульса записи регистр 38 переводится в режим сдвига и под действием тактовых импульсов с помощью сумматора 39 по модулю два генерирует линейную рекурентную последовател ь н ость с начал ьн ыми условиями, соответствующими значениям двоичных канальных символов.

Сформированная кодером M-последовательность поступает на информационный вход декодера (фиг.1) и под воздействием тактовых импульсов записывается в регистр

1 сдвига и поступает на входы каналов 2, В каждом канале 2 формируются двоичные символы, представляющие результат сложения по модулю два содержимого ячеек регистра 1, и в момент поступления циклового синхроимпульса на выходах сумматоров блока 3 в каждом канале 2 формируется ! = ",5.вариантов канального сигнала, Все вариантов информационного сигнала поступают на мажоритарный элемент 4, который присваивает выходному двоичному символу значение, определяемое по принципу большинства.

Цикловые синхроимпульсы поступают также на управляющий вход блока 5 считывания, на информационные входы которого с выходов мажоритарных элементов 4 поступают канальные сигналы. На выходах блока 5 считывания в моменты поступления цикловых синхроимпульсов формируются значения выходных канальных символов.

По сравнению с прототипом предлагаемый декодер позволяет повысить достоверность декодирования двоичной информации за счет применения корректирующего кода с избыточностью в виде линейной рекуррентной последовательности с мажоритарнологическим декодированием последней, Если в прототипе вероятность ошибочной оценки передаваемого двоичного символа равна Р1, то в предлагаемом декодере эта вероятность снижается и равна

В предлагаемом декодере при формировании информационных символов каждого канала 2 используются, кроме проверочных символов кода, также информационные символы соседних каналов.

Эффективность мажоритарно-логического декодирования зависит от числа проверок I, организованных в блоке 3 каждого канала 2.

Так, при = 15 и оценке двоичного символа с вероятностью ошибки P1 = 0,1, вероятность ошибочного декодирования двоичного символа на выходе любого канала 2 равна

P2 = G,0013. Изобретение позволяет варьировать характеристиками декодера, так как снижение требований к величине Р2 приводит к сокращению числа проверок и, как следствие, к сокращению длины кода.

Формула изобретения

Декодер, содержащий регистр и основной канал цифровой обработки, выполненный на блоке сумматоров по модулю два и мажоритарном элементе, выходы блока сумматоров по модулю два соединены с соответствующими входами мажоритарного элемента, выходы регистра соединены с соответствующими входами блока сумматоров по модулю два основного канала цифровой обработки, отличающийся тем, что, с целью повышения достоверности декодера, в него введены блок считывания и дополнительные каналы цифровой обработки, каждый из которых выполнен аналогично основному каналу цифровой обработки, входы блоков сумматоров по модулю два дополнительных каналов цифровой обработки подключены к соответствующим выходам регистра, выходы мажоритарных элементов основного и дополнительных каналов цифровой обработки соединены с соответствующими информационными входами блока считывания, информационный вход и вход тактовой синхронизации регистра являются соответственно информационным входом и входом тактовой синхронизации декодера, управляющий вход регистра объединен с управляющим входом блока считывания и является входом цикловой синхронизации декодера, выходы блока считывания являются выходами декодера.

1624700

1624700

Составитель M. Никуленков

Техред M.Mîðãåíòàë Корректор Т, Палий

Редактор В. Ковтун

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 203 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5