Устройство для цифровой фильтрации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах технического диагностирования. Цель изобретения - повышение точности выделения трендов нестационарных по математическому ожиданию случайных процессов, содержащих серии резко отличающихся по амплитуде сигнала выбросов. Устройство для цифровой фильтрации содержит блок входной памяти, блок памяти обратной связи, блок памяти корректированных данных, блок памяти остатков мультиплексора , блок программного управления и выходной регистр, Новым в устройстве для цифровой фильтрации является то, что указанные блоки и их связи обеспечивают контроль входных данных на наличие в них выбросов сигнала, корректировку входных данных в случае присутствия в них выбросов сигнала и рекурсивную цифровую фильтрацию корректированных данных, что обеспечивает повышение точности выделения трендов нестационарных по математическому ожиданию случайных процессов, содержащих серии резко отличающихся по амплитуде сигнала выбросов. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9) (! !) (s!)s G 06 F 15/353

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4651354/24 (22) 13.02.89 (46) 07.02,91, Бюл. ЬЬ 5 (71) Ленинградский электротехнический институт им. В.И. Ульянова (Ленина) (72) А.В. Моэгалевский, В.П. Калявин, В.С. Воэнюк, К,А. Бессонов и А.Ю. Щербаков (53) 681.325(088.8) (56) Авторское свидетельство СССР

М 1336205, кл. Н 03 Н 21/00, 1987.

Алексеенко А.Г. и др. Разработка и отладка микропрограммного обеспечения цифровых систем на основе секционированных микропроцессоров. — Микропроцессорные средства и системы, 1987, N. 4, с. 40 — 43. (54) УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ

ФИЛЬТРАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано в системах технического диагностирования.

Цель изобретения — повышение точности

Изобретение относится к вычислительной технике и может быть использовано в системах технического диагностирования для выделения в реальном масштабе времени трендов.нестационарных случайных процессов, содержащих серии последовательных резко отличающихся по амплитуде сигнала выбросов.

Целью изобретения является повышение точности выделения трендов нестационарных процессов, что обеспечивает повышение точности диагностирования эа счет управляемой корректировки входных данных при рекурсивной цифровой фильтрации. выделения трендов нестационарных по математическому ожиданию случайных процессов, содержащих серии резко отличающихся по амплитуде сигнала выбросов, Устройство для цифровой фильтрации содержит блок входной памяти, блок памяти обратной связи, блок памяти корректированных данных, блок памяти остатков мультиплексора, блок программного управления и выходной регистр, Новым в устройстве для цифровой фильтрации является то, то указанные блоки и их связи обеспечивают контроль входных данных на наличие в них выбросов сигнала, корректировку входных данных в случае присутствия в них выбросов сигнала и рекурсивную цифровую фильтрацию корректированных данных, что обеспечивает повышение точности выделения ) трендов нестационарных по математическому ожиданию случайных процессов, содержащих серии резко отличающихся по амплитуде сигнала выбросов. 3 ил.

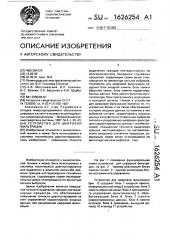

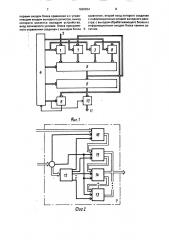

На фиг. 1 приведена функциональная схема устройства для цифровой фильтрации; на фиг. 2 — пример реализации блока памяти; на фиг, 3 — пример реализации блока программного управления.

Устройство для цифровой фильтрации (фиг. 1) содержит блок 1 входной памяти, информационный вход 2 устройства, блок 3 памяти обратной связи, блок 4 программного управления, мультиплексор 5, обрабатывающий блок 6, блок 7 памяти корректированных данных, блок 8 памяти остатков, блок 9 сравнения, выходной регистр 10 и выход 11 устройства.

1626254

Блок 7 памяти корректированных данных (фиг. 2) содержит дешифратор 12, регистры 13-16(блоки 1, 3 и 8 памяти выполнены аналогично). Блок 4 программного управления (фиг. 3) содержит формирователи 17 начального адреса, счетчики 18 адреса, узлы

19 постоянной памяти и регистры 20 микрокоманд, объединенные в формирователь 21 микрокоманд, формирователь 22 импульсов сдвига, элементы 23, генератор 24 импульсов и 0-триггер 25.

Устройство в соответствии с записанной в узлах 19 блока микропрограммой работает следующим образом.

Предыдущие значения входного сигнала x(n), выходного сигнала y(n), корректиpotBHHbIx данных хк(п) и остатков Л (n) хранятся в регистрах 16 соответственно блока 1 входной памяти, блока 3 памяти обратной связи. блока 7 памяти корректированных данных и блока 8 памяти остатков.

Остальные значения x(n — 1), у(п — 1), х (п-i), Л(п-i), 1- 1, М хранятся в регистрах 13 — 15 соответствующих блоков памяти, Коэффициенты a(l),l = О, М нерекурсивной в b(i), 1=

- 1, M рекурсивной частей цифрового фильтра, набор микрокоманд для управления блоками устройства записаны в узлах 19 формирователя 21 микрокоманд блока 4 программного управления. Генератор 24 импульсов формирует синхроимпульсы СИ, определяющие частоту следования микрокоманд микропрограммы, Формирователь

22 импульсов сдвига формирует импульсы сдвига СДВ, каждый из которых определяет начало очередного цикла обработки входного сигнала устройства. После окончания предыдущего цикла вычислений на прямом выходе 0-триггера 25 имеется сигнал низкого уровня, который, поступая на входы разрешения счетчиков 18 адреса всех секций формирователя 21, обеспечивает занесение в зти счетчики начального адреса микрокоманд. При подаче импульса сдвига СДВ, означающего начало очередного цикла вычислений, на информационный вход 0-триггера 25 на выходе триггера устанавливается сигнал высокого уровня, обеспечивающий запуск счетчиков адреса и, соответственно, запуск микропрограммы в целом. При этом во всех регистрах блока 1 входной памяти, блока 3 памяти обратной связи, блока 7 памяти корректированных данных и блока 8 памяти остатков происходит сдвиг записанной в них информации на один регистр вниз, Сдвиг осуществляется путем одновременной подачи разрешающих импульсов на тактовый вход регистра 16 и соединенные между собой тактовые входы регистров 135

15

15 соответствующих блоков памяти, Следующий управляющий импульс, поступая на тактовый вход регистра 16 блока 1 входной памяти, вызывает запись текущего значения x(n) через вход 2 устройства в данный регистр, В соответствии с микрокомандами, поступающими на вход, являЮщийся управляющим, блока 1 входной памяти. дешифратор 12 выдает сигнал высокого уровня на вход разрешения считывания регистра 15, что вызывает появление x(n) на выходе блока 1 входной памяти. Далее x(n) коммутируется через мультиплексор 5 на вход данных регистра 16 блока 7 памяти корректированных данных, где по приходу сигнала высокого уровня на тактовый вход записывается в данный регистр. Дешифраторы 12 начинают поочередно подавать сигналы высокого уровня на входы разрешения считывания

20 регистров 16, 15 и 14 блока 1 входной памяти и блока 3 памяти обратной связи, что вызывает поочередную выдачу на выходы укаэанных блоков сигналов x(n — I), I = О, М и у(п — I), I = 1, М с одновременной коммутацией

25 их через мультиплексор 5 на вход, являющийся счетным, обрабатывающего блока 6, где осуществляется вычисление текущего значения y(n) выходного сигнала по рекурсивной форме:

30 м м

y(n) = a(i)x(n — I)+ ) b(i)y(n — I).

l=O 1=1

Полученное значение y(n) записывается в регистр 16 блока 3 памяти обратной связи.

Начинается считывание сигналов х(п-i), I = О, М и y(n-(), 1 = О, М соответственно иэ блока 1 входной памяти и блока 3 памяти обратной связи, коммутация их через мультиплексор 5 на счетные входы обрабатыва40 ющего блока 6, где происходит вычисление текущего значения остатка Ь(п) по формуле

h,(п) = y(n) — x(n).

Полученное значение Л(n) выхода обрабатывающего блока 6 записывается в регистр

45 16 блока 8 памяти остатков., Происходит коммутация значений Л(п — I), 1 - О, М из регистров блока 8 памяти остатков через мультиплексор 5 на счетные входы обрабатывающего блока 6, где для контроля наличия выбросов во входном сигнале и исходит вычисление текущего значения Л„по формуле м л„= 1 л(о — i ) 1. полуненноо эначе55 ние Л„с выхода обрабатывающего блока 6 поступает на вход блока 9 сравнения, на управляющий вход которого поступают из узла 19 блока 4 программного управления

1626254 сигнал уставки Лпз,д и команда на выполХ ненио операции сравнения. При выполнеНИИ УСЛОВИЯ hn Лл дд, Что ГОВОРИТ 0

Х) Х наличии выброса во входных данных, на выходе блока 9 сравнения формируется сигнал высокого уровня, поступающий на вход элемента И 23, являющийся входом блока 4 программного управления. На второй вход элемента И продолжает поступать сигнал высокого уровня первого триггера регистра

20 микрокоманд первой секции формирователя 21 микрокоманд, Сигнал высокого уровня с выхода элемента И поступает на информационный вход 0-триггера 25, обеспечивая дальнейшее выполнение микропрограмм. При этом происходят считывание значения у(п) из блока 3 памяти обратной связи, коммутация его через мультиплексор

5 на вход данных блока 7 памяти корректированных данных и запись в регистр 16 этого блока. Осуществляется поочередная коммутация корректированных данных х, (ll-!), i =О, M и выходных значений у(п — I), I = О, М соответственно иэ блока 7 памяти корректировки данных и блока 3 памяти обратной связи через мультиплексор 5 на счетные входы обрабатывающего блока 6, где происходит вычисление корректированного значения у(п) по корректированным входным данным по формуле

y(n) = 5 a(i)x (n — I)+ Д, b(l)y(n — I). =о I 1

Полученное значение y(Ä) с выхода обрабатывающего блока 6 записывается в регистр

16 блока 3 памяти обратной связи. Одновременно управляющий сигнал с выхода блока

4 программного управления приходит на управляющий вход регистра 10, вызывая коммутацию сигнала у(п) с выхода обрабатывающего блока 6 на выход 11 устройства.

Последняя микрокоманда микропрограммы, имея в первом разряде, соответствующем . выходу первого триггера регистра микрокоманд 20 первой секции формирователя микрокоманд 21, сигнал низкого уровня, поступающий на вход элемента И 23 блока 4 программного управления, формирует на входе сброса и прямом выходе

0-триггера 25 сигнал низкого уровня, что вызывает остановку счетчика 18 адреса всех секций формирователя 21 микрокоманд блока 4 программного управления, занесение в счетчики 18 адреса начального адреса микрокоманд для следующего цикла вычислений и окончание выполнения микропрограммы, При выполнении условия Л„< Л,,д, Х Х чтО ГОВОрИт Об ОтСутетВИИ ВЫброСОВ ЕО ВХОДных данных сигнал у(п) rîììóòèðóåòcÿ из регистра 16 блока 3 памяти обратной связи через мультиплексор 5, обрабатывающий блок 6 и регистр 10 на выход 11 устройства.

Сигналом для прекращения выполнения микрокоманд без осуществления корректировки входных данных является появление сигнала низкого урсвня на выходе блока 9 сравнения, поступающего на вход элемента

И 23, являющийся входом блока 4 программного управления, вызывающего сброс

0-триггера 25, что приводит к остановке выполнения микропрограммы. записи в счетчики 18 начального адреса микрокоманд.

При этом до прихода следующего сигнала сдвига СДВ на выходе 11 устройства будет значение у(п), Число регистров в блоках памяти, число секций формирователя 21 микрокоманд блока 4 программного упрзвления, а значит и разрядность микрокоманд зависят от порядка M-цифрового фильтра.

Формула изобретения

Устройство для цифровой фильтрации, содержащее блок входной памяти, блок памяти обратной связи, блок программного управления, мультиплексор, обрабатывающий блок, выход которого соединен с информационным входом блока памяти обратной связи, управляющий вход которого соединен с управляющим входом блока входной памяти и с первым выходом блока программного управления, второй выход которого соединен с управляющим входом мультиплексора, первый и второй информационные входы которого соединены соответственно с выходами блоков памяти обратной связи и входной памяти, информационный вход которого соединен с информационным входом устройства, выход мультиплексора соединен с информационным входом обрабатывающего блока, управляющий вход которого соединен с третьим выходом блока программного управления, о т л и ч а ю щ е е с я тем, что, с целью повышения точности выделения трендов нестационарных процессов, в него введены блок памяти корректированных данных, блок памяти остатков, блок сравнения, выходной регистр, причем выход мультиплексора соединен с информационным вхОдОм б loK3 памяти KoppeKTMp083HHblx данных, управляющий вход которого соединен с управляющим входом блока памяти остатков и с четвертым выходом блока программного управления, пятый и шестой выходы которого соединены соответственно с

1626254

Риг.1 первым входом блока сравнения и с управляющим входом выходного регистра, выход которого является выходом устройства, вход логического условия блока программного управления соединен с выходом блока сравнения, второй вход которого соединен с информационным входом выходного регистра, с выходом обрабатывающего блока и с информационным входом блока памяти ос5 татков.

1626254

° °

° °

Составитель Логачева

Техред M.Ìîðlåíòàë Корректор Т.Палий

Редактор И.Горная

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 279 Тираж 405 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035., Москва, Ж-35, Раушская наб., 4/5