Устройство для преобразования двоичного кода в код системы счисления остаточных классов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для преобразования числа из двоичного кода в код системы остаточных классов. Устройство содержит сумматоры 2 унитарного кода по модулю и дешифратор 3 со связями. Причем сумматоры 2 унитарного кода по модулю выполняют посредстпм коммутации умножение на два значения первого слггаемого и прибавление значения второго слагаемого по модул ;. 2 ил

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (505 Н 03 M 7/18

ГОСУДАРСТВЕН.ЫИ КОМИТЕ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР,.;æèâ

i_#_Ilt". ,(. г .

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4690891/24 (22) 15.03.89 (46) 07.02.91. Бюл. М 5 (72) В.М.Шамардинов, Г.В.Сергиенко, Г.И.Клюквин и Н.С.Стученкова (53) 681.3 (088.8) (56) Авторское свидетельство СССР

М 1417192, кл. Н 03 M 7/18, 1987.

Авторское свидетельство СССР

М 241107, кл. Н 03 М 7/18, 1967.... Ж„„1626385 А1 (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА B КОД СИСТЕМЫ

СЧИСЛЕНИЯ ОСТАТОЧНЫХ КЛАССОВ (57) Изобретение относится к вычислительной технике и предназначено для преобразования числа из двоичного кода в код системы остаточных классов, Устройство содержит сумматоры 2 унитарного кода по модулю и дешифратор 3 со связями. Причем сумматоры 2 унитарного кода по модулю выполняют посредстг зм коммутации уь.чожение на два значения первого сл "rae oro и прибавление значения второго слагаемого по модул.. 2 ил.

1626385

Изобретение относится к вычислительной технике и предназначено для преобразования двоичных кодов в код системы счисления остаточных классов {CCOK) в высокопроизводительных вычислительных машинах, работающих в ССОК, Целью изобретения является упрощение устройства.

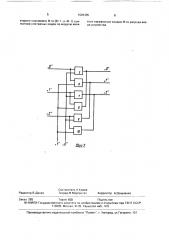

На фиг. 1 представлена схема устройства для преобразования двоичного кода в код ССОК; на фиг. 2 — схема сумматора унитарных кодов по модулю (для P=3).

Устройство {фиг.1) содержит регистр 1, (и — M — 1) сумматоров 2 унитарных кодов по модулю, дешифратор 3, выход 4 устройства, причем выходы M старших разрядов регистра 1 соединены соответственно входами разрядов входа дешифратора 3, выходы которого соединены с входами разрядов первого слагаемого (и — M — 1)-го сумматора 2 унитарных кодов по модулю. Вход первого слагаемого К-го сумматора 2 унитарных кодов по модулю соединен с выходом (Кi1)-ro сумматора 2 унитарных кодов по модулю, выход первого сумматора 2 унитарных кодов по модулю является выходом 4 устройства, выход К-го разряда регистра 1 соединен с входом вт рого слагаемого К-го сумматооа 2 унитарных кодов по модулю, вход устройства — с входом регистра 1.

Сумматор 2 унитарных кодов по модулю (фиг,2) содержит с первого по шестой элементы И 5-10. причем вход первого разряда входа первого слагаемого сумматора 2 унитарных кодов по модулю соединен с первыми входами элементов И 5 и 6, вход второго разряда входа первого слагаемого сумматора 2 уни-арных кодов по модулю — с первыми входами элементов И 7 и 8, вход третьего разряда входа первого слагаемого сумматора 2 унитарных кодов по модулю — с первыми входа ли элементов И 9 и 10, вход первого разряда входа второго слагаемого сумматора 2 унитарных кодов по модулю соединен с вторыми входами элементов И

5,7 и 9, вход второго разряда входа второго слагаеглого сумматора 2 унитарных кодов по модулю — с вторыми входами элементов И

6, 8 и I0, выходы элементов И 5 и 8 обьединены и являются выходом первого разряда выхода сумматора 2;нитарных кодов по модулю, выходы элементов И 6 и 9 обьединень, и являются выходом второго разряда выхода сумматора 2 унитарных кодов по модулю, выходы элементов И 7 и 10 объединены и являются выходом третьего разряда выхода сумматора 2 унитарных кодов по модулю. Следуег отметить. что обьсдинение выходов э; ементов И сумматора 2 выполняет функцию логического VIFiVI, а

50 нумерация разрядов дана в порядке возрастания их значений

Устройство работает следующим образом, В регистр 1 поступает в параллельном коде двоичное число Х:

Х=Ап2 + Ап-1 2 + ... Ao2, (1)

Величина модуля, по которому будет производиться преобразование, пусть будет P.

Для описания его в двоичном коде потребуется М разрядов, т,е.

Р=2 у (2)

М - !о9г(Р+ у ), (3) где у — величина, показывающая, на сколько модуль P меньше 2 .

Таким образом, длину входного слова дешифратора 3 можно найти иэ (3). В дешифраторе 3 осуществляется преобразование двоичного кода длиной M разрядов в унитарной код Далее преобразованное число поступает на сумматоры 2, где коммутацией разрядов осуществляется сдвиг числа влево на один разряд и прибавление единицы, если в разряде регистра 1, подключенном к второму входу соответствующего сумматора 2, единица. Результат преобразования снимается с выхода 4 устройства.

Разрядность двоичного кода не имеет значения, так как наращивание разрядности осуществляетсн простым добавлением сумматоров 2 к устройству, что повышает однородность устройства и может быть использовано при изготовлении его в интегральном исполнении.

Формула изобре ения

Устройство для преобразования двоичного кода в код системы счисления остаточных классов, содержащее (и — M -1) сумматоров унитарных кодов по модулю (празрядность числа, М-количество разрядов, необходимое для представления модуля), причем выход перво-о сумматора унитарных кодов по модулю является выходом устройства, вход первого слагаемого К-ro

{К=1...(!о9гп) -1) сумматора унитарных кодов по модулю соединен с выходом (К+1)-ro сумматора унитарных кодов по модулю, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит дешифратор, причем входы Мст,арших разрядов входа устройства соединены соответственно с входами разрядов входа дешифратора. выходы которого соединены соответственно с входами разрядов входа первого слагаемого (h-M-1)-го сумматора унитарных кодов по модулю, вход первого слагаемого à-.о (а= (!ogden)., и-M 2) сумматора унитарных кодов flo модулю сое-— динен с выходом (а - 1) - го сумматора унитарных кодов по модула . вход

1626385

1" .0"

ОЬГ 2

Составитель А.Клюев

Техред M.Ìîðãåíòàë

Корректор А.Осауленко

Редактор В.Данко

Эаказ 285 Тираж 450 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 второго слагаемого В-го (В=1...n-M -1) сумматора унитарных кодов по модулю является парафазным входом В-го разряда входа устройства.