Устройство для выделения ошибок из цифрового испытательного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к технике проводной связи. Цель изобретения - повышение достоверности выделения ошибок путем обнаружения проскальзываний и перерывов связи. Поставленная цель достигается путем введения блока обработки входного сигнала, который реализует функцию умножения на порождающий полином и фиксирует соответственно срывы синхронизма . Сигналы с блока поступают на входы блока обнаружения перерывов связи и блока обнаружения проскальзывания, которые формируют информацию о наличии проскальзываний и перерывов связи. Устройство отличается выполнением блока обработки входного сигнала. 1 з.п.ф-лы, 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з Н 04 В 3/46

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Qh

Ю

° ф

О

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4629271/09 (22) 30,12,88 (46) 07.02.91. Бюл. М 5 (72) А.Е. Кальной и Б.П, Алексеев (53) 621.395. 664(088,8) (56) Патент Англии М 1431218, кл. Н 4 Р, 1976, (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ

ОШИБОК ИЗ ЦИФРОВОГО ИСПЫТАТЕЛЬНОГО СИГНАЛА (57) Изобретение относится к технике проводной связи. Цель изобретения — повышение достоверности выделения ошибок

Изобретение относится к электросвязи, в частности к устройсвам выделения ошибок.

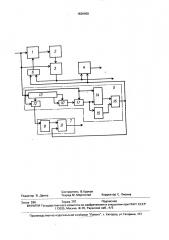

Цель изобретения — повышение достоверности выделения ошибок путем обнаружения проскальзываний и перерывов связи, На чертеже представлена электрическая структурная схема устройства.

Устройство содержит корректор 1 ошибок, генератор 2 псевдослучайной последовательности, компаратор 3, блок 4 обнаружения проскальзываний, блок 5 обработки входного сигнала, ключ 6, блок 7 обнаружения перерывов связи, включающий в себя счетчик 8 и триггер 9.

Блок 5 обработки входного сигнала содержит первый 10, второй 11 и третий 12 сумматоры по модулю два, регистр 13 сдвига, триггер 14, счетчик 15 и элемент ИЛИ 16.

Устройство работает следующим образом, В начале работы генератор 2 формирует последовательность, асинфазную с прихо„.,5U ÄÄ 1626400 A1 путем обнаружения проскальзываний и перерывов связи. Поставленная цель достигается путем введения блока обработки входного сигнала, который реализует функцию умножения на порождающий полином и фиксирует соответственно срывы синхронизма. Сигналы с блока поступают на входы блока обнаружения перерывов связи и блока обнаружения проскальзывания, которые формируют информацию о наличии проскальзываний и перерывов связи. Устройство отличается выполнением блока обработки входного сигнала, 1 з.п,ф-лы, 1 ил, дящей. Вследствие этого на выходе компаратора 3 выделяются ошибки даже при отсутствии ошибок в приходящем сигнале.

Регистр 13 сдвига и сумматоры 10, 11 по модулю два образуют узел умножения на порождающий полином.. На его выходе(выход суматора 11 по модулю два) вначале работы также выделяются ошибки из-за первоначального произвольного состояния рагистра 13 сдвига. Этими ошибками триггер 14 устанавливается в единичное состояние, а счетчик 15 — в исходное состояние с уровнем логической единицы на выходе.

Этот выходной сигнал счетчика 15 не может изменяться раньше чем произойдет заполнение безошибочной последовательностью регистра 13 сдвига, так как в этом случае интервал между любыми двумя соседними ошибками всегда меньше емкости счетчика

15. Поэтому на выходе элемента ИЛИ 16 также уровень логической единицы несмотря на то, что в промежутке между двумя. ошибками триггер 14 может устанавливаться в нулевое состояние, 1626400

55 лонной последовательностей. Эти ошибки у

Таким образом, с второго выхода блок э на управляющий вход ключа 6 ошибок поступает уровень логической единицы, раэрешзя прохождение каждой ошибки с компаратора через ключ 6 на корректор 1, где происходит инвертирование каждого символа приходящего сигнала, не совпадающего в текущем тактовом интеовале с символом эталонной последовательности, Таким образом, генератор 1 формирует последовательность с прежним фазовым сдвигом относительно приходящей, Такой режим работы устройства продолжается до тех пор, пока не произойдет заполнение регистра 13 безошибочным отрезком приходя ей последовательности.

После этого по выходному сигналу сумматора 11 триггер 14 устанавливается в нулевое состояние. На выходе счетчик 15 также установится в логический н ль, если интервал с отсутствием ошибок в приходящем сигнале будет больше, чем время заполнения счетчика. B з ом случае на выходе блока 5 будет сигнал с уровнем, равным логическому нулю, запрещающий коррекцию приходящего сигнала корректором 1. После чего на выходе генератора 2 формируется последовательность, синфазная с приходящей, и начинается процесс правильного выделения ошибок из проходящей последовательности. Каждая ошибка в приходящем сигнале выделяется также и на выходе второго сумматора 11, устанавливая уровень логической единицы на втором выходе блока 5, Эта единица разрешает корректировку ошибочного символа на входе генератора 2, тем самым сохраняется синхронизация генератора 2 при наличии ошибок в приходящем сигнале, В этом режиме работы устройства при наличии импульса ошибки на первом входе б ока 4 обнаружения проскальзывания на втором его входе обязательно б дет уровень логиче кой единицы, которая запрещает прохождение сигнала ошибки. Поэтому на его выходе и на выходе "Проскальзывание" устройства будет уровень логического нуля.

При наличии проскальзывания (нарушение синфаэности приходящей и эталонной последовательностей) происходит процесс восстановления синхронизации. Поэтому обязательно наступит момент, когда на втором входе блока 4 обнаружения проскальзывания будет уровень логического нуля (регистр 13 сдвига вновь заполнен безошибочной последовательностью и счетчик 15 переполнен). а на его первом входе — ошибки, из-за асинфазности приходящей и эта5

45 проходяг через блок 4 на выход Проскальзывание" устройства, сигнализируя о том, что имело место проскальзывание.

Перерыв связи в системах передачи может проявляться двояким образом, В первом случае это сигнал, не имеющий переходов (фронтов), причем это может быть как логический нуль, так и логическая единица. Во втором случае такой сигнал имеет место только вначале перерыва, а в остальное время перерыва за счет действия

APY появляется случайная последовательность импульсов, обусловленная шумами. В обоих случаях счетчик 8 срабатывает и выдает на выходе уровень логического нуля, так как при перерыве связи независимо от того, каков уровень сигнала на входе устройства (нуль или единица), на выходе сумматора 12 по модулю два будет обязательно уровень логического нуля и счетчик 8 досчитает до переполнения, Триггер 9 фиксирует перерыв связи, начало которого определяется нулевым уровнем сигнала со счетчика

8, а конец — уровнем логического нуля на втором выходе блока 5, потому, что во время перерыва связи на этом выходе обязательно будет уровень логической единицы. Действительно, при перерыве связи в виде логической единицы на входе устройства, после заполнения регистра 13 сдвига этим сигналом на выходе сумматора 11 по модулю два постоянно уровень логической единицы, а следовательно, такой же сигнал будет и на выходе элемента ИЛИ 16.

При перерыве в виде логичского нуля после заполнения этим сигналг м регистра

13 сдвига на выходе сумматора 11 по модулю два будет уровень логического нуля, однако на выходг элемента ИЛИ 16 по прежнему будет уровень логической единицы, т1к как при заполнении регистра 13 сдвига нулевым сигналом триггер 14 обязательно устанавливается в единичное состояние и буде-. оставаться в этом состоянии весь перерыв из-за запрета его установки в нулевое состояние логическим нулем на входе управления три, гера 14.

При перерыве связи в вида случайной последовательности импульсов логическая единица на выходе элемента ИЛИ 16 будет по,,держиваться логической единицей с выхода счетчика 15, так как в этом случае интервьл следования ошибок на выходе сумматора 11 по модулю два меньше времени заполнения счетчика 15. Таким образом, при перерыве связи в любом виде он будет зафиксирован в виде логической единицы на выходе триггера 9 и выходе прерывания стройства.

162 б400

При перерыве связи генератор 2 сохраняет свою фазу вследствие наличия логической единицы на втором входе корректора

1, Таким образом, и при перерыве связи происходит правильное выделение ошибок. 5

Устройство выделения ошибок работоспособно также и при испытательном сигнале в виде периодически повторяющейся произвольной комбинации из двоичных символов. В этом случае в блоке 5 исключается 10 сумматор 10 по модулю два, т.е. выход последнего (n-го) разряда регистра 13 сдвига соединен с первым входом сумматора 11 по модулю два. Таким образом, можно для случая периодической двоичной комбинации 15 иэ симвОлов считать, что узел умножения на порождающий полинам состоит иэ и-разрядного регистра 13 сдвига, информационный вход которого и выход последнего разряда соединены с соответствующими 20 входами сумматора 11 по модулю два.

Формула изобретения

1. Устройство для выделения ошибок из цифрового испытательного сигнала, содер- 25 жащее последовательно соединенные корректор ошибок, вход которого является входом устройства, генератор псевдослучайной последовательности. компаратор, второй вход которого объединен с входом 30 устройства, и ключ, выход которого соединен с вторым входом корректора ошибок, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности выделения ошибок путем обнаружения проскальзываний и 35 перерывов связи, введены блок обнаружения проскальзываний, выход которого явля ется выходом "Проскальзывание" устойства, а первый вход соединен с выходом компаратора. который является выходом ошибки устройства, последовательно соедингнные блок обработки входного сигнала, вход которого объединен с входом устройства, а второй выход соединен с вторым входом блока обнаружения проскальзываний и управляющим входом ключа, и блок обнаружения перерывов связи, второй вход которого соединен с вторым выходом блока обработки входного сигнала, а выход является выходом прерывания устройства.

2, Устройство по и, 1, о т л и ч а ю щ е е с я тем, что блок обработки входного сигнала содержит последовательно соединенные регистр сдвига, вход которого является входом блока обработки входного сигнала, первый сумматор по модулю два, второй вход которого соединен с соответствующим выходом регистра сдвига, второй сумматор по модулю два, второй вход которого соединен с входом регистра сдвига, триггер, второй вход которого соединен с входом регистра сдвига, и элемент ИЛИ, выход которого является вторым выходом блока обработки входного сигнала, а второй вход соединен с входом счетчика, управляющий вход которого соединен с выходом второго сумматора по модулю два, и третий сумматор по модулю два, первый, второй входы которого соединены соответственно с входом и соответствующим выходом регистра сдвига, а выход является первым выходом блока обработки входного сигнала.

1626400

Составитель В.Курков

Техред М. Моргентал Корректор С. Лисина

Редактор В. Данко

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 286 Тираж 382 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5