Устройство циклового фазирования для волоконно-оптических систем передачи

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИ4ЕСКИХ

РЕСПУБЛИК

„„gu„„f62821 2 (1)С Н 04 ?, 7/04

1„: „(»

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д BTGPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР (21) 4649815/09 (22) 22.02.89 (46) 15.02.91. Бюл. № 6 (72) А.П.Орлов, А.Х.Ганитулин, В.А,Куликов и И.А.Шилов (53) 621.394.662(088.8) (56) Авторское свидетельство СССР

¹ 1552392, кл. H 04 L 7/04, 1988. (54) УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ ДЛЯ ВОЛОКОННО-ОПТИЧЕСКИХ СИСТЕМ

ПЕРЕДАЧИ (57) Изобретение относится к электросвязи и может быть использовано в волоконно-оптических системах передачи с самосинхронизирующимися кодами для цикловой синхронизации. Целью изобретения является цикловое фазирование при использовании биимпульсного кода без введения избыточных символон,. Устройство содержит дифференцирующий блок 1, R-S-триггер

2, счетный триггер 3, линии 4 и 5 задержки, регистры 6 и 7 сдвига, дешифратор 8, элемент ИЛИ 9, преобразователь 10 импульсов по длительности, элементы И 11-14. Принимаемые

2 данные подаются на вход дифференцирующего блока 1. С помощью R-Ятриггера 2 и линии 4 задержки происходит выделение периодических импульсов дифференцирования. В момент приема последнего символа сообщения на выходе регистра 6 находится единичный сигнал, что обеспечивает запись импульса дифференцирования в нулевой разряд регистра 7, в результате чего происходит подтверждение синфазности работы. При нарушении структуры кода с помощью R-S-триггера 2, элемента И 11 и преобразователя 10исключается возможность нарушения работоспособности устройства. Появление ошибки также приводит к нарушению структуры кода и формированию сигнала ошибки на выходе элемента

И 14, который поступает потребителю.

Одновременно для исключения нарушения синхронной работы устройства происходит установка R-S-триггера 2 в нулевое состояние и запрет прохождения импульса дифференцирования через элемент И 12. 2 ил.

1628212

Изобретение относится к области электросвязи и может быть использовано в волоконно-оптических системах передачи с самосинхронизирующимися кодами для цикловой синхронизации.

Целью изобретения является цикловое фазирование при использовании биимпульсного кода без введения из- 10 быточных символов.

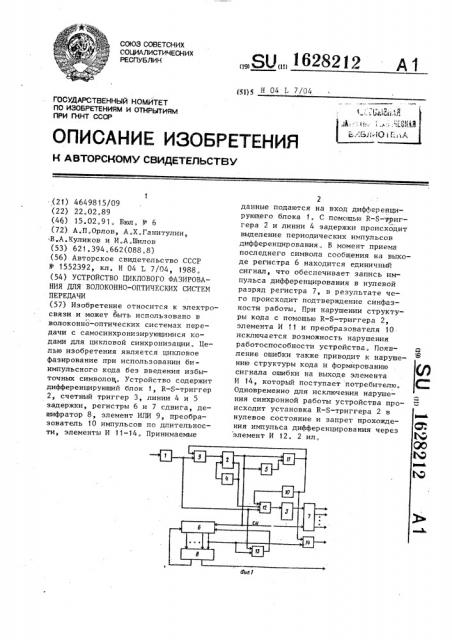

На фиг. 1 представлена структурная электрическая схема устройства циклового фазирования для волоконнооптических систем передачи; на фиг.2 - 15 временные диаграммы сигналов, поясняющие работу устройства циклового фазирования для волоконно-оптических систем передачи.

Устройство циклового фазирования 20 для волоконно-оптических систем пе редачи содержит дифференцирующий блок 1, R-S-триггер 2, счетный триггер 3, первую и вторую линии 4 и 5 задержки, первый и второй регистры 25

6 и 7 сдвига, дешифратор 8, элемент

ИЛИ 9, преобразователь 10 импульсов по длительности, первый и второй элементы И 11 и 12, первый и второй дополнительные элементы И 13 и 14. 30

Устройство циклового фазирования для волоконно-оптических систем передачи работает следующим образом.

Преобразование данных из биимпульсного кода в двоичный осуществляется следующим образом.

Принимаемые данные (фиг. 2а,б) (считается, что на вход устройства циклового фазирования для волоконнооптических систем передачи пбступают 40 восстановленные по форме и длительности биимпульсные сигналы) подаются на вход дифференцирующего блока 1 (фиг. 1), на выходе которого формируется последовательность дифферен 45 цирующнх импульсов, соответствующая смене значений посылок в принимаемых символах (фиг. 2в). С помощью К$триггера 2 и первой линии 4 задержки (ее длительность составляет примерно 0,7 Т, где Т вЂ” период следования биимпульсных сигналов) происходит вьделение периодических импульсов дифференцирования, посредством которых на прямом выходе R-S-триггера 2 . формируется последовательность синхроимпульсов (СИ) (фиг. 2д).

С помощью положительных импульсов, формируемых на инверсном выходе R-Sтриггера 2 (фиг. 2г) н второго элемента И 12, происходит селекция импульсов дифференцирования, вьделенных посередине битового интервала (моменты смены значений принимаемых символов (фиг. 2н)).

Эти импульсы поступают на счетный вход счетного триггера 3, обеспечивая последовательное изменение его состояния (фиг. 2о). Таким образом, на прямом выходе счетного триггера 3 формируются данные, представленные в двоичном коде.

Для преобразования последовательного формата данных в параллельный (используемый для обработки данных в

ЗВМ) применяется второй регистр 7 сдвига (фиг. 2п). После приема сообщения с выходов первого регистра 6 сдвига происходит его вьдача парал- . лельным кодом потребителю информации.

Организация цифровой синхронизации в устройстве циклового фазирования для волоконно-оптических систем передачи осуществляется следующим образом.

В момент приема последнего (и-го) символа сообщения на и-м выходе первого регистра 6 сдвига находится еди- . ничный сигнал (фиг. 2з), который обеспечивает прохождение импульса дифференцирования, вьделенного посередине n-ro биимпульсного. символа (фиг. 2в). Через третий элемент И 13 происходит асинхронная запись его в нулевой разряд второго регистра 7 сдвига (фиг, 2м), в результате чего происходит подтверждение синфазности работы и подтверждение наличия в данном биимпульсном сигнале (и-м) смены значений импульсов. Ввиду того что вьделение СИ осуществляется с задержкой © 0,7 Т (фиг. 2б,в,д), сдвиг единичного символа в первом регистре 6 сдвига происходит по СИ, вьделенному в предыдущем символе, т.е. сдвиг единицы относительно номера принимаемого символа осуществляется с опережением примерно на

0,3 Т (фиг. 2э).

При правильном функционировании устройства циклового фазирования для волоконно-оптических систем передачи в первом регистре 6 сдвига находится только один единичный символ, причем обязательна однозначная связь (со сдвигом Ф 0,3 Т) номера принимаемого в данный момент символа сооб — .

5 16 щения с номером разряда, в котором записан единичный символ.

В том случае, если наличие смены импульсов в и-м символе достигнуто за счет нарушения структуры кода (фиг. 2б), с помощью второй линии 5 задержки (ee длительность составляет примерно 0,3 Т) (фиг, 2е) и первого элемента И 11 (фиг. 2ж) происходит обнаружение факта нарушения структуры кода. На прямом выходе

R-S-триггера 2 за счет пропуска периодического импульса дифференцирования формируется импульс, длительность которого превышает 0,3 Т, что не может произойти при нормальной работе устройства циклового фазирования для волоконно-оптических систем передачи (фиг. 2д,е). По сигналу с выхода первого элемента И 11 происходит установка в нулевое состояние

R-S-триггера 2, что исключает возможность нарушения работоспособности устройства циклового фазирования для волоконно-оптических систем передачи (фиг. 2ж,д). Кроме того, происходит. запуск преобразователя

10, на выходе которого формируется управляющий импульс длительностью Т (фиг. 2к). По этому импульсу запрещается изменение состояния счетного триггера 3 при приеме п-го символа, т.е. в этом случае принимаемый символ имеет такое же значение, как и предыдущий (n-1) .

Сигнал цикловой синхронизации или сигнал на считывание сообщения из первого регистра 6 сдвига потребите- лю информации выдается с второго выхода дешифратора 8, который выделяет на выходах второго регистра 7 сдвига комбинацию вида 10„„.00, т.е. наличие единичного символа только в первом разряде первого регистра 6 сдвига (фиг, 2и), в этот момент времени закончен прием и-го символа сообщения и происходит подготовка к приему первого символа следующего сообщения (фиг. 2б,д).

В случае возникновения ошибки в принимаемых данных устройство циклового фазирования для волоконно-оптических систем передачи работает следующим образом.

Появление ошибки (фиг. 2б) также приводит к нарушению структуры кода, и следовательно, к пропуску импульса дифференцирования (фиг.. 2в), в

28212 6 результате чего на выходе первого элемента И 11 формируется единичный сигнал (фиг. 2ж), который поступает на первый вход второго дополнитель5 ного элемента И 14, на второй (инверсный) вход которого поступает нулевой потенциал с п-ro выхода первого регистра 6 сдвига (т. е. нарушение структуры кода произошло не в момент приема n-ro символа) . Сигнал ошибки, формируемый на выходе второго дополнительного. элемента И 14 (фиг. 2л), поступает потребителю информации для организации режима переспроса искаженного сообщения. В этом случае также для исключения возможности нарушения синхронной работы устройства циклового фазирования для

20 волоконно-оптических систем передачи происходит установка R-S-триггера 2 в нулевое состояние и запрет прохождения импульса дифференцирования, выделенного посередине биимпульсного

25 интервала через второй элемент И 12.

В случае нарушения синфазной работы устройства циклового фазирования для волоконно-оптических систем передачи происходит стирание. единично30 го символа в первом регистре 6 сдвига. Состояние регистра, когда в его разрядах записаны только нулевые символы, выделяется дешифратором

8, по сигналу с первого выхода кото35 рого происходит запись во все разряды первого регистра 6 сдвига единичных символов. Вследствие случайности смены значений символов в сообщении селекция периодического импульса диф4С ференцирования, выделяемого посередине битового интервала, будет осуществлена не более чем sa два-три сообщения.

45Формула изобретения

Устройство циклового фазирования для волоконно-оптических систем передачи, содержащее последовательно

5р соединенные R-S-триггер и первую линию задержки, выход которой подсоединен к S-входу R-S-триггера, последовательно соединенные вторую линию задержки, первый элемент И и. элемент

ИЛИ, а также дифференцирующий блок, второй элемент И и первый и второй регистры сдвига, тактовые входы которых объединены, а другой вход первого элемента И подключен к входу

1628212 второй линии задержки, причем вход дифференцирующего блока является входом устройства, о т л и ч а ю щ ее с я тем, что, с целью циклового фазирования при использовании биимпульсного кода без введения избыточных символов, введены преобразователь импульсов по длительности, счетный триггер, дешифратор и первый и второй дополнительные элементы И, при этом выход дифференцирующего блока подсоединен к другому входу элемента ИЛИ, объединенным входам второго элемента И и первого дополнительного элемента И, выход которого подсоединен к R-входу R-S-триггера, прямой выход которого подсоединен к другому входу первого элемента И и тактовому входу первого регистра сдвига, выход первого элемента И подсоединен непосредственно к входу второго дополнительного элемента И и через преобразователь импульсов по длительности к второму входу второго элемента И, третий вход которого подключен к инверсному выходу R-S-триггера, информационный и установочный входы первого регистра сдвига подключены соответственно к выходу первого дополнительного элемента И и первому выходу дешифратора, входы которого подключены к соответствующим выходам первого регистра сдвига, соответствующий выход, которого подсоединен к другим входам первого и второго дополнительных элементов И, причем второй выход дешифратора, выход второго дополнительного элемента И и выходы второго регистра сдвига являются соответственно выходом синхросигнала, выходом сигнала ошибки и информационными выходами.