Устройство измерения частотных характеристик группового времени запаздывания четырехполюсников

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано для измерения частотных характеристик группового времени запаздывания (ГВЗ) радиоустройств . С целью повышения точности и быстродействия измерения ГВЗ на вход исследуемого четырехполюсника 8 подают сигнал задающего генератора 1, модулированный в модуляторе 5 полигармоническим сигналом, опорный и измерительный сигналы (каналов 10 и 9) преобразуются на постоянную промежуточную частоту с помощью следящего генератора 2 и блока 3 синхронизации . С помощью избирательных усилителей 13 и 14 спектральные составляющие сигнала промежуточной частоты фильтруются и подвергаются двухканальной цифровой обработке с оценкой их амплитуды и фазы с помощью аналого-цифровых преобразователей 15 и 16, блоков 17 и 18 предварительной обработки, регистров 19 и 20 и соединенной с ними по системной магистрали вычислительной системы 22, содержащей микропроцессорный вычислитель 23, пульт 25 управления и блок 24 отображения (дисплей). Микропроцессорный вычислитель 23 работает по принципу дискретного преобразования Фурье, определяя амплитуду и фазу для каждой спектральной составляющей сглаженного за Р периодов сигнала промежуточной частоты. При этом используется для дискретизации К точек за период основной гармоники модуляционного сигнала.8 ил. Os OJ

СОЮЗ СОВЕТСКИХ

СОЦИАЛ И СТИЧ Е С К ИХ

РЕСПУБЛИК (si)s G 04 F 10/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4608766/21 (22) 25.11.88 (46) 28.02.91. Бюл, М 8 (71) Красноярский политехнический институт (72) А.С.Глинченко и В,В.Моисеенко (53) 621.317.373(088.8) (56) Приборы и техника эксперимента, 1988, М 5, с. 76.

Авторское свидетельство СССР

ФЬ 1064269, кл. 6 04 F 10/06, 1982. (54) УСТРОЙСТВО ИЗМЕРЕНИЯ ЧАСТОТНЫХ ХАРАКТЕРИСТИК ГРУППОВОГО

ВРЕМЕНИ ЗАПАЗДЫВАНИЯ ЧЕТЫРЕХПОЛ ЮСНИКОВ (57) Изобретение относится к измеритель.ной технике и может быть использовано для измерения частотных характеристик группового времени запаздывания (ГВЗ) радиоустройств. С целью повышения точности и быстродействия измерения ГВЗ на вход исследуемого четырехполюсника 8 подают сигнал задающего генератора 1, модулированный в модуляторе 5 полигармоническим, ЯЛ,, 1631511 Al сигналом, опорный и измерительный сигналы (каналов 10 и 9) преобразуются на постоянную промежуточную частоту с помощью следящего генератора 2 и блока 3 синхронизации. С помощью избирательных усилителей 13 и 14 спектральные составляющие сигнала промежуточной частоты фильтруются и подвергаются двухканальной цифровой обработке с оценкой их амплитуды и фазы с помощью аналого-цифровых преобразователей 15 и 16, блоков 17 и 18 предварительной обработки, регистров 19 и 20 и соединенной с ними по системной магистрали вычислительной системы 22, содержащей микропроцессорный вычислитель 23, пульт 25 управления и блок 24 отображения (дисплей). Микропроцессорный вычисли- - ) тель 23 работает по принципу дискретного преобразования Фурье, определяя амплитуду и фазу для каждой спектральной составляющей сглаженного за Р периодов сигнала промежуточной частоты. При этом . Я используется для дискретизации К точек за период основной гармоники модуляционно,рр дф го сигнала. 8 ил.

1631511

Изобретение относится к электрорадиоизмерениям и может быть использовано для построения измерителей частотных характеристик группового времени запаздывания (ЧХ ГВЗ) высокочастотных четырехполюсников.

Цель изобретения — повышение точности и быстродействия измерений.

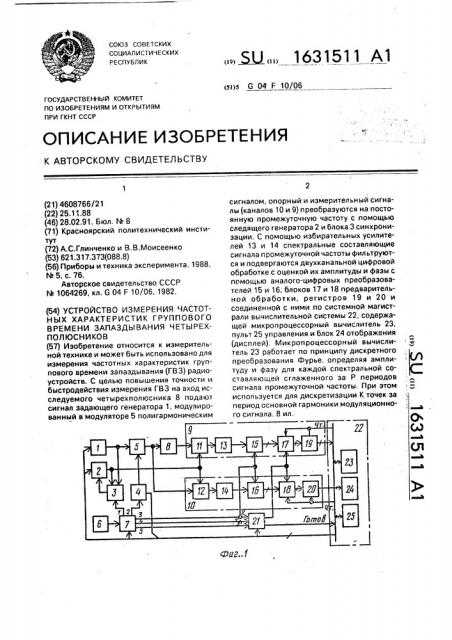

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — 6 — структурные схемы возможных вариантов реализации блока предварительной обработки, блока управления, блока синхронизации, формирователя полигармонического сигнала и формирователя сетки частот; на фиг. 7— схема алгоритма работы устройства; на фиг. 8 — временные диаграммы сигналов блока управления.

Устройство (фиг, 1) содержит задающий

1 и следящий 2 генераторы, блок 3 синхронизации, входами соединенный с выходами генераторов 1 и 2, а выходом — с входом автоподстройки следящего генератора 2, формирователя 4 полигармонического сигнала, модулятор 5, опорный генератор 6 с подключенным к нему формирователем 7 сетки частот, который подключен первым выходом к блоку 3 синхронизации, вторым выходом — к формирователю 4 полигармонического сигнала, соединенному выходом с модулирующим входом модулятора 5, сигнальный вход последнего подключен к выходу задающего генератора 1, à его выход— к входной клемме четырехполюсника 8, Устройство содержит также измерительный 9 и опорный 10 каналы, входы которых подключены. соответственно к выходной клемме четырехполюсника 8 и выходу модулятора 5. Каналы включают соответственно последовательно соединенные смеситель 11 (12), избирательный усилитель 13 (14), аналого-цифровой преобразователь (АЦП) 15(16), блок 17(18) предварительной обработки и регистр 19(20). Соединенные вторые входы смесителей 11 и 12, АЦП 15 и

16 и блоков 17 и 18 предварительной обработки подсоединены соответственно к выходу следящего генератора 2, третьему выходу формирователя 7 сетки частот и первому выходу блока 21 управления. Вычислительная система 22 содержит подсоединенные к ее.системной магистра. ли "Общая шина" (ОШ) микропроцессорный блок 23, блок 24 отображения и пульт 25 управления. Посредством системной маги„страли ОШ система 22 соединена также с входами "Чтение" блоков 17, 18 и регистров

19, 20, с информационными выходами регистров 19 и 20, выходом готовности блока 21 управления, а также с входами управления

55 генераторов 1 и 2, формирователей 4 и 7 и блока 21 управления.

Блоки 17 и 18 предварительной обработки (фиг. 2) содержит каждый первый регистр 26, сумматор 27, оперативный запоминающий узел (ОЗУ) 28, второй регистр 29, инвертор 30, счетчик 31 адреса и элемент ИЛИ 32, при этом 0-входы триггеров первого регистра 26 и выходы ОЗУ 28 являются соответственно информационными входами и выходами блока предварительной обработки, счетный вход первого регистра 26, вход инвертора 30, первый вход элемента ИЛИ 32, вход записи ОЗУ 28 и счетный вход второго регистра 29 соединены с первым управляющим входом блока, а входы сброса счетчика 31 адреса и второго регистра 29 соединены соответственно с вторым и третьим управляющими входами блока предварительной обработки. Второй вход элемента ИЛИ 32 является входом чтения блока, выход первого регистра 26 соединен с первым входом сумматора 27, второй вход которого соединен с выходом второго регистра 29, 0-входы которого соединены с выходом ОЗУ 28, соединенному информационным входом с выходом сумматора 27, входом чтения — с выходом инвертора 30 и входом адреса — с выходом счетчика 31 адреса, вход которого подключен к выходу элемента ИЛИ 32.

Блок 21 управления (фиг. 3) содержит

RS-триггер 33, первый и второй 0-триггеры

34 и 35, первый и второй элементы И 36 и 37 и третий и четвертый 0-триггеры 38 и 39, при этом первые входы первого 36 и второго 37 элементов И и объединенные С-входы первого 34 и второго 35 D-триггеров образуют соответственно первый, второй и третий входы блока, а выход первого элемента И

36, выход второго элемента И 37 с подключенными к нему С-входами третьего 38 и четвертого 39 D-триггеров и выход четверо того D-триггера образуют первый, второй и третий выходы управляющей шины блока 21 управления, которые соединяются с соответствующимЬ входами управления блоков

17 и 18 предварительной обработки. R-входы всех триггеров блока 21 управления соединены с входом начальной установки, а

S-вход RS-триггера 33 — с входом "Пуск", которые образуют входную управляющую шину блока. Прямой выход 0-триггера 35 является выходом готовности блока, инверсный выход этого триггера соединен с вторыми входами первого 36 и второго 37 элементов И, выход RS-триггера 33 соединен с 0-входом первого 0-триггера 34, выход которого соединен с 0-входами второго

35 и третьего 38 D-триггеров, который выхо1631511 дом соединен с D-входом четвертого 0триггера 39.

Блок 3 синхронизации (фиг. 4) содержит смеситель 40, входы которого образуют первый и второй входы блока, сОединенный с его выходом фазовый детектор 41, второй вход которого является опорным входом блока, а к выходу подключен фильтр 42, выход которого является выходом блока 3 синхронизации, Формирователь 4 полигармонического сигнала (фиг. 5) содержит последовательно соединенные элемент ИЛИ 43, счетчик 44 адреса, запоминающий узел (ЗУ) 45, регистр

46, цифро-аналоговый преобразователь (ЦАП) 47 и фильтр 48, выход которого является выходом формирователя 4 полигармонического сигнала, Первый вход элемента

ИЛИ 43 с подключенным к нему С-входом регистра 46 является тактовым входом, а объединенные второй вход элемента ИЛИ

43 и вход записи ЗУ 45, вход сброса счетчика 44 адреса и информационные входы ЗУ

45 образуют управляющие входы формирователя 4 полигармонического сигнала, Формирователь 7 сетки частот (фиг. 6) содержит пять последовательно включен.ных делителей 49 — 53 с переменным коэффициентом деления (ДПКД), выходы которых являются выходами формирователя, а вход первого ДПКД 49 — его входом, управляющие входы всех ДПКД образуют шину управления, соединенную с системной магистралью ОШ.

Устройство работает следующим образом.

Выходной гармонический сигнал задающего генератора 1 с частотой f< поступает на модулятор 5, где модулируется по амплитуде сигналов с выхода формирователя 4 полигармонического сигнала, который представляет собой сумму конечного числа гармоник частоты модуляции Q, = 2 л F><.

Um (t) - Q Um СОВ (К Д, т + Р ), где Um, фс — амплитуда и фаза гармоник модулирующего сигнала.

На выходе модулятора 5 образуется АМколебание, содержащее (2L+ 1) спектральных составляющих с частотами f; = f(: + Р, (i-(-1) и начальными фазами уъь i

-1,2,...(2L+1). Это колебание проходит через исследуемый четырехполюсник 8. Фазы спектральных составляющих на его выходе обозначим через р. С помощью смесителей

11 и 12 и следящего генератора 2 происходит перенос спектров сигналов, имеющихся

35

50 лы U(t) в последовательность цифровых ко55 дов 0(пТЯ) - U(t)t - пТц с частотой

2G

25 на выходе модулятора 5 и выходе четырехполюсника 8, на частоты(11 +. frl где frчастота следящего генератора 2. Примем, что частота fr равна fr - f(; — (L+1) Е (преобразование сниэу). Избирательные усилители 13 и 14 выделяют низкочастотные спектральные составляющие с частотами

Г(= iFM, i = 1,2... (2L+ 1); соответствующими высокочастотным составляющим fi, Их,начальные фазы в измерительном и опорном сигналах отличаются от фаэ (Ъ1, р ВЧ-составляющих на значения начальной фазы колебания следящего гетеродина 1/1 и фазОвых сдвигов, вносимых смесителями 11 и 12 (p ) и избирательными усилителями 13 и

14(<ру), которые в первом приближении можно принять одинаковыми для обоих каналов. Так как в дальнейшем полезная информация определяется по разности фазовых сдвигов измерительного и опорного каналов, то дополнительные сдвиги р, р м, ру в дальнейшем считаются равными и не учитываются, Таким образом. выходные сигналы избирательных усилителей 13 и 14 измерительного и опорного каналов можно записать в следующем виде:

2L +1

Uu(t) = g 0,,1 (о) cos (! Q» t+p).

1=1

Если измерить разности фаз одноименных спектральных составляющих измерительного и опорного каналов Ф1 = p — рок вычиСлить приращения разностей фаз между соседними составляющими А@ =

= ч1+ 1 — Ф(и поделить их на интервал частот между ними F>. то по одной реализации сигнала можно получить 2L оценок группового времени запаздывания t31 = ЬФi/F, соответствующих частотам (f(+ 5н1)/2. Эта задача решается с помощью АЦП 15 и 16, блоков 17 и 18 предварительной обработки, регистров 19 и 20 и вычислительной системы 22, осуществляющей двухканальную цифровую обработку полигармонических сигналов и оценку их параметров. При этом

АЦП 15 и 16 преобразуют аналоговые сигнадискретизации fg = 1/Тв, определяемой частотой тактовых импульсов f3, поступающих с.третьего выхода формирователя 7 сетки частот на тактовые входы АЦП 15 и 16. Частота дискретизации fg = f выбирается крат1631511

20

40

55 ной частоте сигнала f3 = KF< и удовлетворяющей условию fs 2Рмакс где Емакс максимальная частота в спектре сигнала; смаке

=(2L+1) F<, Это обеспечивает частотное разрешение (2L+1) спектральных составляющих.

Отсчеты сигналов поступают далее в блоки 17 и 18 предварительной обработки.

Функции этих блоков и их структура зависят от требуемой скорости обработки информации и быстродействия используемого микропроцессорного блока 23 или микроЭВМ.

Чем меньше быстродействие микроЭВМ, тем больший объем обработки выполняется блоками предварительной обработки и наоборот.

В данном случае алгоритм работы устройства показан на фиг. 7. Блоки 17 и 18 предварительной обработки (фиг. 2) осуществляют накопление К отсчетов сигнала за период К 2 (2L+1) и усреднение одноименных отсчетов сигнала за P периодов, что обеспечивает повышение точности измерения. Блоки 17 и 18 предварительной обработки управляются сигналами с шины управляющих сигналов блока 21 управления в соответствии со схемой блока, показанной на фиг. 3, и временной диаграммой на фиг. 8.

Управляющие сигналы в блоке 21 управления формируются из тактовых последовательностей 1з, f4, fs, поступающих с третьего, четвертого и пятого выходов формирователя 7 сетки частот на управляющие входы этого блока. Их частоты равны:

fa = KFp, f4 = Ь/K = м, fg= f4/P = Рм/P.

На фиг. 8 показаны временные диаграммы сигналов на входах и выходах блока 21. управления для частотного случая соотношений частот: fa = 8Ем, f4 = Ек, Ь = Рм/3.

Сигналы управления — "Чтение", "Запись", "Начальная установка", "Пуск" — формируются в интерфейсном модуле микроЭКМ 23 по совпадению сигналов выбора соответствующих внешних устройств и системных сигналов чтения и записи. Тактовые последовательности fa, f4 в течение измерительного цикла проходят через открытые элементы И 36 и 37 и поступают соответственно на первый и второй управляющие входы блоков 17 и 18 предварительной обработки. Под действием последовательности fz отсчеты сигнала в этих блоках записываются в регистр 26 и поступают затем в сумматор 27, на входы которого посту.пают коды с выхода регистра 29. Этот регистр в начале измерительного цикла в течение одного (первого) периода сигнала находится в сброшенном состоянии под, действием третьего управляющего сигнала с выхода О-триггера 39 блока 21 управления. При этом на информационный вход

ОЗУ 28 поступают отсчеты сигнала, которые во время второго полупериода тактовой последовательности fa записываются в его последовательные ячейки, адресуемые счетчиком 31 адреса, управляемым через открытый элемент ИЛИ 32 этой же последовательностью fa. В течение первого полупериода последовательности fa ОЗУ 28 через ин вертор 30 переводится в режим чтения и в регистр 29 записывается код и-го отсчета сигнала, соответствующего предыдущему периоду сигнала, Поэтому, начиная с второго периода сигнала, когда с регистра

29 снимается сигнал сброса, в сумматоре 27 суммируются отсчеты сигнала U(nTg) с одинаковыми номерами n = 1,2,...К в каждом периоде и записываются снова в те же ячейки памяти. После заполнения К ячеек счетчик 31 адреса по второму входу сбрасывается тактовой последовательностью fp и вновь адресует ячейки ОЗУ 28 с нулевого адреса. В результате за P периодов сигнала в К ячейках ОЗУ 28 оказываются записанными К усредненных отсчетов сигнала 0(пТ ) (при Р, кратном двойке, т.е, P =

2, среднее значение U(nTg) получается путем простого сдвига запятой суммарного кода 0(пТд) íà t разрядов влево), По истечении P периодов сигнала, т.е. в конце измерительного цикла, нулевым уровнем с инверсного выхода D-триггера 35 закрываются элементы И 36 и 37 блока 21 управления и тактовые последовательности

fg, f4 перестают поступать на первый и второй входы блоков 17 и 18 предварительной обработки, По окончании измерительного цикла 03У 28 переводится в режим чтения.

Одновременно на прямом выходе D-триггера 35 формируется единичный сигнал готовности, который с блока 21 управления по системной магистрали ОШ поступает в микроЭВМ 23.

МикроЭВМ 23 по прерыванию или путем программного опроса этого сигнала уведомляется о завершении цикла накопления измерительной информации и приступает к ее считыванию, Для этого по системной магистрали из микроЭВМ 23 поступают сигналы чтения регистра 19 и блока 17 предварительной обработки измерительного канала. Сигнал чтения через элемент

ИЛИ 32 последовательно увеличивает содержимое счетчика 31 адреса и переписывает содержимое К ячеек памяти ОЗУ 28 в регистр 19, из которого по системной маги1631511

5

10 страли считывается в микроЭВМ 23. Аналогично считываются К отсчетов сигнала опорного канала с блока 18 предварительной обработки через регистр 20.

Далее микроЭВМ 23 в соответствии с алгоритмом (фиг. 7) подготавливает измеритель к новому измерительному циклу, если ширина спектра испытательного сигнала относительно частоты fc не перекрывает всей полосы анализа исследуемого четырехполюсника 8. В этом случае микроЭВМ 23 выдает управляющие коды на изменение (увеличение) частоты сигналов задающего 1 и следящего 2 генераторов на величину (2 >

+ 1)FM. Затем на блок 21 управления подается сигнал начальной установки, сбрасывающий все триггеры этого блока в нулевое состояние. При этом открываются элементы

И 36 и 37, разрешая прохождение тактовых последовательностей fg, f4 на блоки 17 и 18 предварительной обработки, и нулевым уровнем по третьему выходу шины управления блока 21 управления регистр 29 устанавливается в нулевое состояние, что запрещает усреднение (суммирование) отсчетов сигнала в ОЗУ 28, т.е. работу в режиме накапливающего сумматора. В ОЗУ в .этом случае записываются только отсчеты каждого текущего периода сигнала. После начальной установки следует сигнал "Пуск".

Сигналом "Пуск" RS-триггер 33 блока 21 управления устанавливается в единицу и подготавливает 0-триггер 34, который первым тактовым импульсом fs устанавливается в единицу. Одновременно совпадающим с fg по времени первым тактовым импульсом f4 устанавливается в единицу и О-триггер 38, подготавливая D-триггер 39. С этого момента начинается цикл накопления измерительной информации, В течение первого периода сигнала в ОЗУ 28 записываются отсчеты этого периода, а затем вторым импульсом f4, соответствующим началу второго периода сигнала. устанавливается в единицу 0-триггер 39 и снимает сброс с регистра 29 блока 17(18) предварительной обработки, разрешая режим суммирования отсчетов. С приходом второго тактового импульса fs, т.е. по истечении P периодов сигнала, О-триггер 35 устанавливается в единицу и инверсным выходом закрывает элементы И 36 и 37, прекращая цикл накопления измерительной информации.

Возможен вариант реализации блоков

17 и 18 предварительной обработки, когда обеспечивается только запоминание К P отсчетов сигнала за P периодов и блоки выполняют роль быстрой буферной памяти. В другом случае отсчеты сигнала могут непосредственно вводиться в микроЭВМ 23 в

55 темпе их поступления, при этом блоки 17 и

18 упрощаются до уровня буферного регистра. Соответствующим образом меняется (упрощается) также структура блока 21 управления..

Во время накопления новой информации микроЭВМ 23 осуществляет обработку отсчетов сигнала предыдущего измерительного цикла, вычисляя спектр амплитуд и фаз полигармонических сигналов (для обоих каналов) с помощью дискретного преобразования Фурье:

U (jl Q,) = д и (п т,) (cos — +

2 %in и =1

К

2 7г!и

+! siп

Модуль Щ1 Q ) определяет оценку амплитуды спектральной составляющей. а аргумент, т.е. арктангенс, отношения мнимой и веще-. ственной части — оценку начальной фазы соответственно для опорного и измерительного каналов р,ь р.

По этим оценкам находятся измеренные значения ГВЗ для 2L частот или 2 точек

ЧХ ГВЗ за один измерительный цикл:

Ъ = Ô м = (Ф + 1 — Ф) Рм л..л

Кроме того, разносги фаз Ф = ро — р определяют отсчеты ФЧХ четырехполюсника, а отношение амплитуд спектральных составляющих измерительного и опорного каналов — его АЧХ. Для уменьшения времени обработки при вычислении спектра могут быть использованы алгоритмы БПФ, а также специализированные Фурье-процессоры.

После снятия ЧХ ГВЗ во всей полосе рабочих частот четырехполюсника 8 или а заданной ее области цикл измерения завершается. При этом результаты измерения выводятся микроЭВМ 23 через системную магистраль на блок отображения, где индицируются либо в виде цифровых данных, либо в виде графиков ЧХ ГВЗ, ФЧХ и АЧХ или неравномерности ЧХ ГВЗ. Одновременно может осуществляться документирование результатов измерений на бумажном или магнитном носителе микроЭВМ, Ручное управление измерителем производится с пульта 25 управления, через кото рый в микроЭВМ 23 вводятся начальные и конечные значения частот задающего 1 и следящего 2 генераторов, значения частоты модуляции, код которой из микроЭВМ 23 передается по системной магистрали на вход управления формирователя 7 сетки ча1631511

12 стот, С пульта 25 управления производится также начальный и повторный пуск измерителя. Перед началом работы или после завершения снятия полной ЧХ ГВ3 четырехполюсника 8 микроЭВМ 23 периодически опрашивает состояние пульта 25 управления и при подаче оператором соответствующей команды приступает к ее исполнениюю.

С помощью блока 3 синхронизации поддерживается постоянство разности частот задающего 1 и следящего 2 генераторов:

fc — fr - (L+ 1)F .

Вариант его возможной реаализации (фиг. 4) включает смеситель 40, на выходе которого выделяется колебание разностной частоты, и фазовый детектор 41, где оно сравнивается по фазе с сигналом с первого выхода формирователя 7 сетки частот, игра :ощего роль опорного сигнала. Напряжение с выхода фазового детектора 41 через фильтр 42 поступает на вход автоподстройки следящего генератора 2. При использовании высокостабильных задающего 1 и следящего 2 генераторов, например синтезаторов частоты, их можно синхронизировать просто от общего эталонного генератора, Сложный модулирующий сигнал образуется в формирователе 4 полигармонического сигнала, структурная схема которого приведена на фиг. 5. Его принцип основан на записи в ЗУ 45 одного периода вычисленных значений отсчетов сигнала. Число записываемых отсчетов за период сигнала

М может быть выбрано равным или большим числа отсчетов сигнала при аналогоцифровом преобразовании, т.е. M К. Для, удобства формирования M можно выбрать кратным К, т.е. М = q К, где р = 1, 2,...,С увеличением M уменьшается уровень высокочастотных составляющих в спектре сигнала на выходе ЦАП 47, который преобразует коды сигнала, записанные в ЗУ 45, в аналоговый сигнал, фильтруемый далее фильтром

48. Максимальное значение М ограничивается быстродействием 3У 45 и ЦАП 47. Для уменьшения влияния переходных процессов преобразуемые отсчеты сигнала из ЗУ

45 тактовой последовательностью fz с второго выхода. формирователя 7 сетки частот переписываются в регистр 46. Эта же последовательность частотой 2= MFv =Ц К FM через элемент ИЛИ 43 управляет счетчиком

44 адреса объемом М, обеспечивая последовательное считывание M ячеек ЗУ 45, Для изменения структуры модулирующего сигнала можно предусмотреть ряд

ПЗУ с соответствующими вариантами сиг30 рону превышения некоторых рассмотрен35 ных номинальных значений и могут быть взяты, например, равными:

55 нала либо использовать ОЗУ или ППЗУ, программируемые непосредственно от микро-;

ЭВМ 23, что повышает уровень функциональной гибкости измерителя, При этом на соответствующие входы управления подаются вначале сигнал сброса счетчика

44 адреса, а затем коды отсчетов сигнала, сопровождаемые сигналом записи ЗУ 45, который одновременно через второй вход элемента ИЛИ 43 модифицирует содержимое счетчика 44 адреса. Формирователь 7 сетки частот, формирующий синхронизирующие тактовые последовательности необ; ходимых для работы рассмотренных вариантов реализации формирователя 4 полигармонического сигнала, блока 21 управления и блоков 17 и 18 предварительной обработки, выполнен по структурной схеме (фиг. 6), содержащей пять последовательно соединенных делителей с переменным коэффициентом деления (ДПЩ49 — 53, осуществляющих деление частоты опорного генератора 6. ДПКД программируется через системную магистраль от микроЭВМ 23, При выборе коэффициентов деления можно исходить иэ значения частоты модуляции и числа L спектральных составляющих модулирующего полигармонического сигнала

Наиболее жестко привязана к ним частота

fi с первого выхода, являющаяся опорной частотой блока 3 синхронизации:

f1 - {1 + 1)F, Частоты fz u fa допускают отклонения в стоf3 = КРм = r 4 (L+ 1)Рм f2 = q К Рм

q г 4(1 +1)Гц, где r — целые числа.

Частота опорного генератора при этом должна удовлетворять условию f>r = Sf2, где S —, целые числа, Этому соответствуют коэффициенты деления: для ДПКД 49 — $; ДПКД 50 — q;ДПКД51 — 4 г;ДПКД52 — (L+1)иДПКД

53 — P.

В данном устройстве погрешности измерения сдвига фаз и косвенной оценки

ГВЗ зависят от разрядности АЦП, времени усреднения сигнала и точности вычислений микроЭВМ, Последние два фактора могут управляться программно, что позволяет программировать точность измерения измерителя в зависимости от решаемой задачи. Путем компромисса между точностью и временем измерения можно обеспечить погрешность измерения сдвига фаз порядка сотых долей градуса. Это позволяет пол13

1631511 учить требуемую точность измерения неравномерности ЧХ ГВЗ порядка единицы или доли наносекунды при малом шаге приращения частоты (порядка 20 — 30 кГц), необходимом при исследовании четырехполюсников со сложными многоэкстремальными частотными характеристиками ГВЗ, например фильтров, на ПАВ. Наличие микро3ВМ также позволяет повысить точность за счет программной компенсации систематических погрешностей измерителя, Структура известного устройства не обеспечивает такой точности для указанного класса четырехполюсников, так как погрешности фазовых детекторов составляют в лучшем случае десятые доли градуса, а точность численного дифференцирования

ФЧХ не может быть выше долей единиц процента.

Использование сложного испытательного сигнала в предлагаемом устройстве и цифровой спектральной обработки сигналов, обеспечивающих одновременную оценку нескольких отсчетов ЧХ ГВЗ по одной реализации сигнала, повышают не только точность измерения, но и быстродействие измерителя, Повышение быстродействия или уменьшение времени снятия ЧХ ГВЗ пропорционально количеству спектральных составляющих испытательного сигнала, Оно ограничивается только быстродействием используемой элементной базы.

Формула изобретения

Устройство измерения частотных характеристик группового. времени запаздывания четырехполюсников, содержащее входную и выходную клеммы для подсоединения четырехполюсника, блок управления. задающий и следящий генераторы, а также смеситель опорного канала, сигнальным входом соединенный с входной клеммой для подключения четырехполюсника, смес .òåëü измерительного канала, сигнальным входом соединенный с выходной клеммой для подсоединения четырехполюсника, гетеродинные входы обоих смесителей соединены с выходом следящего генератора, о т5

45 л и ч а ю щ е е с я тем, что. с целью повышения точности и быстродействия, в него введены опорный генератор, формирователь сетки частот, блок синхронизации, формирователь полигармонического сигнала, модулятор, вычислительная система, состоящая .иэ подключенных к системной магистрали микропроцессорного блока, блока отображения и пульта управления, а также в измерительном и опорном каналах подсоединенные к выходу соответствующего смесителя последовательно соединенные избирательный усилитель, аналого-цифровой преобразователь, блок предварительной обработки и регистр, при этом выход опорного генератора соединен с входом формирователя сетки частот. первый выход которого соединен с опорным входом блока синхронизации. второй выход — с тактовым входом формирователя полигармонического сигнала, третий выход — с объединенными тактовыми входами аналого-цифровых преобразователей и первым входом блока управления, вторые и третьи входы которого подключены соответственно к четвертому и пятому выходам формирователя сетки частот, а выходная шина блока управления подключена к входам управления обоих блоков предварительной обработки, выход следящего генератора соединен с первым входом блока синхронизации, выход которого соединен с входом автоподстройки следящего генератора, а второй вход — с выходом задающего генератора, к которому подключен также сигнальный вход модулятора, модулирующий вход которого соединен с выходом формирователя полигармонического сигнала, а выход — с входной клеммой для подключения четырехполюсника, системная магистраль вычислительной системы соединена с входами чтения регистров, входами чтения блоков предварительной обработки, выходами регистров и выходом готовности блока управления, а также с управляющими входами задающего и следящего генераторов, формирователя сетки частот, формирователя полигармонического сигнала и блока управления.

1631511

1631511

Фиг. I

1631511

ИППИПШЮ!ИППИППИПППИПИ

1631511

<- ъ .з н

Составитель Ю.Макаревич

Техред М,Моргентал Корректор С.Черни

Редактор М.Петрова

Производственно-издательский комбинат "Патент", r Ужгород, ул.Гагарина, 101

Заказ 545 Тираж 266 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5