Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на кмоп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к электронной технике и предназначено для применения в электрически программируемых ПЗУ, в которых инжекция горячих носителей используется для записи информации в ячейки памяти накопителя. Целью изобретения является уменьшение потребляемой мощности и повышение надежности формирователя . Авторегулируемый формирователь напряжения содержит шины напряжения программирования и сигнала разрешения программирования, нагрузочный транзистор р-типа, два ключевых транзистора п-типа и один ключевой транзистор п-р-п-типа, транзистор модуляции стокового напряжения записи, транзистор с плавающим затвором , два разрядных транзистора п-типа, эквивалент цепи,выборки, включающий группу из N последовательно соединенных транзисторов, идентичных транзисторам схемы выборки столбцовых шин накопителя ЗУ, при этом N равно числу ступеней дешифрации столбцовых шин, а также схему смещения , идентичную схеме подачи напряжения программирования на затворы элементов памяти накопителя, с соответствующими связями. 1 ил, (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 11 С 7/00, 17/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4454943/24 (22) 05.07.88 (46) 28.02.91. Бюл. N. 8 (72) B.Ï.Ñèäîðåíêo, Н,Б.Груданов и А.А.Хоружий (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

N1297114,,кл,,6 11 С 5/02, 1987.

Заявка ЕВП ¹ 0225441, кл. G 11 17/00, 1986. (54) АВТОРЕГУЛИРУЕМЫЙ ФОРМИРОВАТЕЛЬ НАПРЯЖЕНИЯ ЗАПИСИ ДЛЯ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМЫХ ПОСТОЯННЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ

НА КМОП- ТРАНЗИСТОРАХ (57) Изобретение относится к электронной технике и предназначено для применения в электрически программируемых ПЗУ, в которых инжекция горячих носителей используется для записи информации в ячейки памяти накопителя. Целью изобретения явИзобретение относится к вычислительной технике и предназначено для применения в электрически программируемых постоянных запоминающих устройствах (ПЗУ), в которых инжекция горячих носителей используется для записи информации в ячейки памяти накопителя.

Целью изобретения является уменьшение потребляемой мощности и повышение надежности формирователя..

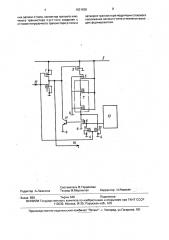

На чертеже представлена электрическая схема авторегулируемого формирователя. напряжения записи для электрически программируемых ПЗУ на КМОП-транзисторах, . Ы,, 1631606 А1 ляется уменьшение потребляемой мощности и повышение надежности формирователя. Авторегулируемый формирователь напряжения содержит шины напряжения программирования и сигнала разрешения программирования, нагрузочный транзистор р-типа, два ключевых транзистора и-типа и один ключевой транзистор п-р-п-типа, транзистор модуляции стокового напряжения записи, транзистор с плавающим затвором, два разрядных транзистора п-типа, эквивалент цепи выборки, включающий группу иэ N последовательно соединенных транзисторов, идентичных тоанзисторам схемы выборки столбцовых шин накопителя

ЗУ, при этом N равно числу ступеней дешифрации столбцовых шин, а также схему смещения, идентичную схеме подачи напряжения программирования на затворы элементов памяти накопителя, с соответствуюQMML1 CBR3RMVI. 1 ил, Предлагаемый формирователь напряжения записи включает нагрузочный транзистор 1 и первый ключевой транзистор 2, включенные последовательно между шиной

3 напряжения программирования и корпусной шиной 4, транзистор 5 модуляции стокового напряжения записи, второй ключевой транзистор 6, эквивалент 7 цепи выборки и транзистор 8 с плавающим затвором, включенные последовательно между шиной 3 напряжения программирования и корпусной шиной 4, первый 9 и второй 10 разрядные транзисторы, а также третий ключевой транзистор 11 и-р-и-типа. Затворы нагрузочного транзистора 1, первого ключевого транзистооа 2 и первого и второ1631606

50 го разрядных транзисторов 9 и 10 объединены и подключены к шине 12 сигнала разрешения программирования, Эквивалент 7 цепи выборки включает группу из N последовательно соединенных МОП-транзисторов, идентичных транзисторам схемы выборки столбцовых шин накопителя запоминающего устройства (ЗУ), где N — число ступеней дешифрации столбцовых шин, затворы которых объединены с затворами второго ключевого транзистора 6 и подключены к шине 3 напряжения программирования. Истоки разрядных транзисторов 9 и 10 подключены к корпусной шине 4. Сток первого транзистора 9 соединен с затвором транзистора 8 с плавающим затвором и подключен к выходу схемы 13 смещения, которая идентична схеме подачи напряжения программирования на затворы элементов памяти накопителя ЗУ. Сток второго транзистора 10 соединен со стоком транзистора

8 с плавающим затвором. Коллектор третьего ключевого транзистора 11 соединен со стоком первого ключевого транзистора 2 и затвором транзистора 5 модуляции стокового напряжения записи и подключен к шине

14, которая является выходом данного формирователя.

Авторегулируемый формирователь напряжения записи в режиме записи информации в ячейки памяти накопителя запоминающего устройства работает следующим образом, В режиме программирования на шину 3 напряжения программирования подается напряжение, достаточное для создания условий записи в элементах памяти. После этого на шину 12 разрешения программирования подается сигнал, обеспечивающий переключение нагрузочного транзистора 1 в открытое состояние и одновременно первого ключевого транзистора 2 в закрытое состояние. Напря>кение программирования с шины 3 через открытый нагрузочный транзистор передается на затвор транзистора 5 модуляции стокового напряжения записи, который переходит в проводящее состояние, и напряжение программирования передается на сток второго ключевого транзистора 6. Так как на затворы транзистора

6 и транзисторов эквивалента 7 цепи выборки воздействует напряжение программирования цепи выборки, т.е. они находятся в проводящем состоянии, а первый и второй разрядные транзисторы 9 и 10 закрыты сигналом разрешения записи (напряжение низкого уровня, примерно равное потенциапу корпусной шины 4), напряжение записи с истока транзистора 5 модуляции стокового напряжения записи передается на сток

40 транзистора 8 с плавающим затвором, Одновременно на управляющий затвор транзистора 8 подается напряжение программирования со схемы 13 смещения, которая выполнена идентично схеме подачи высоковольтного напряжения программирования на затворы ячеек памяти накопителя ЗУ.

Если напряжение на стоке транзистора 8 с плавающим затвором превышает величину напряжения лавинного пробоя стокового рп-перехода, происходит лавинный пробой данного перехода, в результате возникает инжекция дырок в области подложки,. которая приводит к положительному смещению локальной области подложки вблизи транзистора. Так как подложка транзистора одновременно является базой третьего ключевого транзистора 11, то последний переходит в проводящее состояние, B результате протекания тока в цепи транзистора 11 напряжение на истоке нагрузочного транзистора 1, а следовательно, и на затворе транзистора 5 модуляции стокового напряжения записи уменьшается до величины, при которой через транзистор 5 на сток транзистора

8 с плавающим затвором передается напряжение, равное напря>кению лавинного пробоя р-и-перехода стоковой области, Одновременно напряжение с коллектора транзистора 11 подается на шину 14 выходного сигнала, которая соединена с затвором соответствующих ключевых транзисторов (идентичных транзистору модуляции стокового напряжения записи), которые обеспечивают передачу через последующие цепи дешифрации столбцовых шин на сток выбранных ячеек памяти накопителя напряжения записи, равного по величине напряжению, воздействующему на сток транзистора 8 с плавающим затвором. Таким образом, стоковое напряжение записи ячеек памяти накопителя ограничивается на уровне, исключающем работу в области сильного лавинного пробоя.

В режиме считывания информации авторегулируемый формирователь напряжения записи практически не потребляет мощности — ток потребления определяется только токами утечки в МОП- структурах элементов, используемых в устройстве, которые пренебрежимо малы. В указанном режиме работы ЗУ на шину 12 разрешения программирования подается напряжение, примерно равное напряжению на шине 3 напряжения программирования (в режиме считывания напряжение на шине 3 равно напряжению питания ЗУ), При этом нагрузочный транзистор 1 закрывается, первый ключевой транзистор 2 переходит в проводящее состояние и на затворе транзистора 5 уста1631606 навливается напряжение, близкое к нулевому, т,е. транзистор модуляции стокового напряжения записи закрывается. Таким образом, блокируются цепи протекания тока между шиной 3 напряжения программирования и корпусной шиной 4 для исключения воздействия электрических полей на структуру транзистора 8 с плавающим затвором, что может привести к изменению его характеристик, затвор и сток первого и второго ключевых транзисторов 9 и 10. В схеме 13 смещения в режиме считывания осуществляется блокировка подачи воздействия на управляющий затвор транзистора 8, Третий ключевой транзистор 11 п-р-итипа изготавливается в едином технологическом цикле с изготовлением ячеек памяти накопителя и элементов функциональных узлов обрамления. Конструкция транзистора.11 включает подложку, которая является базой данного транзистора, одновременно подложкой кристалла ЗУ и транзистора 8 с плавающим затвором, а также диффузионную область и+-типа, схватывающую по периметру область подложки, в которой расположен транзистор 8, и является коллектором транзистора, Истоковая диффузионная область и+-типа одновременно является эмиттером третьего ключевого транзистора п-р-п-типа.

Преимущество авторегулируемого формирователя напряжения записи перед известными состоит в том, что в режиме считывания информации, который является основным эксплуатационным режимом электрически программируемых ПЗУ, в которых инжекция горячих носителей используется для записи информации, потребляемая устройством мощность практически равна нулю, так как цепи протекания тока блокируются, а токи утечки МОП-структур являются пренебрежимо малыми. Введение в устройство цепи обратной связи, выполненной на биполярном транзисторе и-р-и-типа с базой, объединенной с подложкой опорного транзистора с плавающим затвором, обеспечивает автоматическую регулировку стокового напряжения записи в зависимости от разброса технологических и электрофизических параметров, возникающих в процессе изготовления, что исключает программирование ячеек памяти накопителя в области сильного лавинного пробоя. В результате деградация характеристик записи и хранения информации ячеек памяти происходит в значительно меньшей степени, а отсутствие больших токов в подложку, что имеет место при работе в области сильного лавинного пробоя, повышает надежность

55 работы ЗУ в целом, так как повышается устойчивость КМОП-структуры к тиристорному эффекту.

Формула изобретения

Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах, содержащий нагрузочный транзистор р-типа и первый ключевой транзистор п-типа, затворы которых объединены и являются информационным входом формирователя, сток первого ключевого транзистора и-типа и исток нагруэочного транзистора р-типа обьединены, сток нагрузочного транзистора р-типа подключен к шине напряжения программирования, а исток первого ключевого транзистора п-типа — к шине нулевого потенциала, транзистор модуляции стокового напряжения записи п-типа, сток которого подключен к шине напряжения программирования, в арой ключевой транзистор п-типа, затвор которого подключен к шине напряжения программирования, транзистор с плавающим затвором и элемент согласования по току, состоящий из группы N последовательно соединенных МОП-транзисторов, идентичных транзисторам выборки столбцовых шин репрограммируемого постоянного запоминающего устройства, затворы которых подключены к шине напряжения программирования (N — число степеней дешифрации столбцовых шин), о т л и ч а юшийся тем, что, с целью уменьшения потребляемой мощности и повышения надежности формирователя, в него введены третий ключевой транзистор п-р-п-типа, эмиттер которого подключен к шине нулевого потенциала, а база соединена с подложкой транзистора с плавающим затвором, первый и второй разрядные транзисторы, истоки которых подключены к корпусной шине, затворы объединены с затворами нагрузочного р-типа и первого ключевого п-типа транзисторов и подключены к информационному входу формирователя, сток транзистора с плавающим затвором соединен с истоком выходного транзистора элемента согласования по току и со стоком первого разрядного транзистора, а исток транзистора с плавающим затвором подключен к шине нулевого потенциала, с ок второго разрядного транзистора соединен с управляющим затвором транзистора с плавающим затвором и подключен к шине напряжения смещения, сток первого транзистора элемента согласования по току соединен с истоком второго ключевого транзистора п-типа, сток которого соединен с истоком транзистора модуляции стокового напряже1631606

Составитель В.Гордонова

Техред M. Моргентал Корректор Н.Ревская

Редактор А.Лежнина

Заказ 550 Тираж 340 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, М-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 ния записи п-типа, коллектор третьего ключевого транзистора и-р-и-типа соединен с истоком нагрузочного транзистора р-типа и затвором транзистора модуляции стокового напряжения записи и-типа и является выходем формирователя,