Последовательный цифровой фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к технике цифровой обработки сигналов Цель изобретения - упрощение последовательного цифрового фильтра. Фильтр содержит кодер 1, преобразователь 2 кода, блок 3 памяти и сдвига, коммутатор 5, накапливающие сумматоры 7-9. Введены счетчик 4 и блок 6 постоянной памяти. В фильтре реализован алгоритм фильтрации с использованием дельта-модуляции повышенной информативности , а в качестве умножителя используется блок 3. 2 ил. 4 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 Н 17/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4498383/09 (22) 25.10.88 (46) 28.02.91. Бюл. М 8 (71) Ереванский политехнический институт им. К.Маркса и Ленинградский электротехнический институтсвяэи им.проф.M.А,БончБруевича (72) Л.М.Гольденберг, P.P. Бадаляни А.П,Епремян (53) 621.323 (088.8) (56) Авторское свидетельство СССР

% 1501260, кл, Н 03 Н 17/06, 1987.

„„. Ж„„1631706 А1 (54) ПОСЛЕДОВАТЕЛЬНЫЙ ЦИФРОВОЙ

ФИЛЬТР (57) Изобретение относится к вычислительной технике, в частности к технике цифровой обработки сигналов. Цель изобретения — упрощение последовательного цифрового фильтра, Фильтр содержит кодер 1, преобразователь 2 кода, блок 3 памяти и сдвига, коммутатор 5, накапливающие сумматоры 7 — 9. Введены счетчик 4 и блок

6 постоянной памяти. В фильтре реализован алгоритм фильтрации с использованием дельта-модуляции повышенной информативности, а в качестве умножителя используется блок 3. 2 ил. 4 табл.

1631706

Изобретение относится к вычислительной технике, в частности, к технике цифровой обработки сигналов.

Цель изобретения — упрощение последовательного цифрового фильтра за счет исключения блока памяти и сдвига.

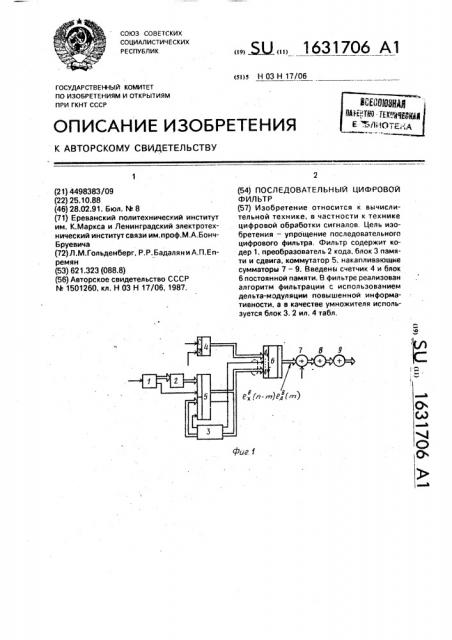

На фиг. 1 приведена электрическая структурная схема последовательного цифрового фильтра; на фиг. 2 — структура блока постоя н ной памяти.

Последовательный цифровой фильтр содержит кодер 1, преобразователь 2 кода, блок 3 памяти и сдвига, счетчик 4, коммутатор 5, блок 6 постоянной памяти, первый 7, второй 8 и третий 9-накапливающие сумматоры.

Предложенный последовательный цифровой фильтр (ЦФ) является ЦФ с адаптивной дельта-модуляцией (АДМ), в котором реализуется следующий алгоритм вычислений: .

N — k+1 M — 1

v (N» =, i g g x

k =1 ь =1 m =0 (1)

1ь („ ),ь ( где Y (N) — N-й отсчет выходного сигнала, ! представленного двоично-позиционным 1разрядным кодом;

М вЂ” порядок ЦФ; .1х (и - в) — (п - в)-й отсчет переменного шага квантования, формируемый при пре. образовании входного сигнала в сигнал

АДМ и представленного двоична-позиционным Ь-разрядным кодом;

4 (m) — m-й отсчет переменного шага ь квантования, формируемый при преобразовании весовых коэффициентов фильтра в

АДМ последовательность и представленного двоично-позиционным Ь-разрядным кодом, В качестве алгоритма адаптации дельта-модуляции используется дельта-модуляция повышенной информативности (ДМПИ), что снижает требуемое быстродействие.

Кроме того, специфика ДМПИ позволяет существенным образом уменьшить затраты ЦФ следующим путем, Пьои ДМПИ переменный шаг квантования 1х (n) изменяется пропорционально степени двойки 1хь(п) 2!, где i 6(0,1„... b-1), т.е. переменный шаг квантования выражается унитарным кодом. Представим 1х (и) следуь ющим образом:

Ь вЂ” 1

1хь(п) =ap(n) g а»{п) ° 2, (2) !

=о . где ap(n) — коэффициент знакового разряда и-го отсчета;

al(b! - коэффициент 1-го разряда п-го отсчета 1х (п), причем a!(n)g(0,1), Аналогичным образом представим 4 (n); ь

Ь вЂ”

5 4(п1) =Со(m) „Cy(m)2 (3)

y=o где Cp(m) и Су(е) — коэффициенты, аналогичные ap(n) и а»(п).

В рассматриваемом случае, когда nepejp менный шаг квантования выражается унитарным кодом, а»(п) и Cpm) для любых значений и и m отличны от нуля только для одного значения и, следовательно, из формул (2) и (3) получим:

@(и) =ap(n) а»(п) -2

4(m) =Со(m ) Cy(m) 2г. (4) ь

Для заданного и произведение

1х (n - m)4 (m) с учетом системы (4) можно ь

20 выразить следующим образом:

1х (и - m)4 (m) = Eo (n — m ) 6 (n — m ) 2 (5) при mQO,|„„M-!», r зр,1„„ 2b-з);

6, (n — m ) = ао (й — m ). О+ Со (m ), (6)

25 r=i+ у, (7) где е,(n-m) и я,(п-m) — коэффициенты, аналогичные ао(п), а;(п) и Со(п), Су(п).

Учитывая формулы (5), (6) и (7), перепишем алгоритм (1) следующим образом:

30 „»ч N — к+! у — 1

Y (n)= g g X

m =0 (8)

+

Из формул (5), (6) и (7) сле,п ует, что для

35 определения произведения !» (и-m) 4 (m) достаточно определить коэффициент знакового разряда в соответствии с формулой (6) и значение отличного от нуля разряда в соответствии с формулой (7). Следовательно, 40 при выполнении свертки в соответствии с алгоритмом (8) операция умножения перерождается в операцию "управляемого сдвига". о

Используемый унитарный код является

45 избыточным кодом и, следовательно, с целью уменьшения разрядности Ь он может быть преобразован в простой безизбыточный код. Уменьшение разрядности представления переменного шага квантования

50 позволяет упростить построение блоков па-. мяти и сдвига. При использовании предварительного преобразования весовые коэффициенты фильтра вводятся в блок памяти и сдвига уже в преобразованном виде, 55 а преобразование отсчетов входного сигнала осуществляется до цифрового коммутатора. Так как сумма безизбыточных кодов, соответствующих 1х (и-m) и 4 (m), указывает

Ы b номер единичного разряда произведения

1б31706

1, (n-m)ln (m). преобразование в безиэбыь ь точный код позволяет также упростить реализацию операции "управляемого сдвига".

Например пусть Ь = 4, для большего класса сигналов именно это значение Ь является оптимальным, тогда 1х (n-m) и in (m) беэ учеь ь та знакового разряда могут принимать только четыре значения (см. табл. 1).

В табл. 1 показаны кодовые комбинации безиэбыточных кодов, получаемых в резул ьтэте и редварител ь ного и рео6раэования gx"(n-m) и gn (m) соответственно.

Произведение Ix (n-m)In (m) может приь нимать 2b - 1 значений (см. табл, 2).

В табл, 2 приводятся все возможные значения ц, (и-m)+ gn (m), где с - количество разрядов.

Из табл. 2 видно, что номер кодовой комбинации gx (n-m) + gn (m) соответствует номеру единичного разряда произведения

Ix (и-m)In (m) Полученный результат не явь ь ляется неожиданным, так как безизбыточный код соответствует номеру единичного разряда сомножителей, а следовательно, сумма безизбыточных кодов в соответствии (7) указывает номер единичного разряда произведения сомножителей. В общем случае количество разрядов безизбыточного кода можно определить, воспользовавшись выражением с = intlogzb, (9) где функция "Int" — определяет ближайшее наибольшее целое число.

В случае ДМПИ, как правило Ь 8, следовательно, величина с может принимать значение два или три.

Рассмотренная выше специфика ДМПИ позволяет использовать блок постоянной памяти, выполненный на основе программируемых постоянных запоминающих устройств (ППЗУ), для выполнения операции умножения в выражении (8). B ППЗУ осуществляется предварительная запись результатов произведения с учетом знакового разряда.

Пусть существует некое запоминающее устройство ППЗУ с общим объемом памяти А = 2", где к — целое положительное число, и пусть необходимо синтезировать ,И

ЦФ с ДМПИ порядка М, причем M = 2 г д е,и — целое положительное число

/ (при M 2 объем памяти А будет использоваться неполностью). Коэффициенты фильтра In (m), m = 0;1;...; M-1 ь заранее определены и образуют множество {1,ь(m)).

Разобъем весь объем памяти А на абзацы Qm таким образом, чтобы каждому коэф5

55 фициенту фильтра In (m) отводился свой абь зац памяти Qm, тогда объем памяти абзаца будет составлять:

Qm = = =2 =2г. (10)

А 2 — с

М

2 где у = k —,и;,и = logz M; m = 0;1;.. „M-1;

В каждом m-м абзаце памяти Qm запишем все возможные значения результатов умножения m-го коэффициента фильтра на все возможные значения отсчетов входного сигнала, т.е, 1л (m) { Ix ), где {1х ) — множесть, ь ь во возможных значений отсчетов входного сигнала (i = 0,1,2,...,Ь). Адресной информацией для выборки абзаца может служить номер m коэффициента фильтра In (m), котоь рый совпадает с номером такта рециркуляционного цикла. В качестве адресной информации для выборки из m-го абзаца результата произведения Ix (n-m)ln (m) можь ь но испольэовать отсчеты входного сигнала

I„ь(n-m), пРеобРазованные в gx (n-m). СтРУктура памяти А приведена на фиг. 1. На фиг.

1 принято: Qm — отведенный m-му коэффициенту фильтра m-й абзац памяти; PIm— результат умножения m-го коэффициента фильтра на j-ю возможную реализацию отсчета входного сигнала на множества {1); ь.

Dm адресный сигнал выборки абзаца памяти Qr, равный номеру такта внутри рециркуляционного цикла, количество таких р сигналов равно M =2, т.е. для его представления двоично-позиционным кодом необходимо р разрядов; gx (n-m)— реализации отсчетов входного сигнала, используемых в качестве адресной информации для выборки Р1" из выбранного сигналом О, m-го абзаца памяти.

Как отмечалось с для большинства случаев, было равно двум, трем, С учетом знакового разряда примем c=4. Из выражения (10) следует, что j = с = 4 и Qm = 2 = 1б. Так

4 как объем общей памяти А = 2, то для большинства случаев количество обзацев Qm не превышает величины 2", Это значение определяет верхнюю границу порядка фильтра М, которое может быть реализовано при заданном объеме памяти А. Коэффициенты фильтра 1 (m) могут принимать с учетом знакового разряда только 2Ь различных значений. Ранее отмечалось, что b< 8, а следовательно, из М абзацев памяти Qm различными будут не более 16 абзацев.

Преобразование отсчетов входного сигнала 1хь(n) в gx (п) не является обязательным, однако оно обеспечивает вместе с уменьшением разрядности блока памяти и

1631706 сдвига M - 1 отсчетов входного сигнала более полное использование объема памяти абзаца Qm. Действительно, так как !» (п) ь представляется унитарным кодом, то из 2Ь возможных кодовых комбинаций информационными являются только Ь комбинаций, т.е. из обьема Qm = 2 используется объем, ь равный Ь, а при преобразовании в gx (n), где

С = IntlOg2b, ОбЬЕМ СОСтаВЛЯЕт Qm = Ь = 2 И используется полностью. Так как коэффициенты фильтра In (m) при обработке сигналов участвуют косвенным образом (они используются на уровне рассчетов, необходимых для программирования ППЗУ), то их преобразование в gn (m) не имеет смысла.

Для рассчитанного ЦФ с ДМПИ, т.е. для

ЦФ с определенными значениями: частоты

fg дискретизации; порядка М фильтра; частоты fT = M fg тактирования рециркуляционных циклов последовательности коэффициентов {In (m)); разрядности представления коэффициентов Ь и с фильтра и отсчетов сигнала, может быть предложена следующая методика программирования запоминающего устройства ППЗУ (в следующих перечисленных пунктах приводятся необходимые выкладки для гиппотетического ЦФ с ДМПИ при fg = 32 кГц, M = 64;

f - 2048 к Гц; Ь = 4; с = 2).

Записывают все возможные, различные значения коэффициентов фильтра In (m) и отсчетов сигнала !» (n) и gx (n)

gn ), p=0,1,...,2Ь-1 ! а (п1)0 0.0001 Iп (п1)4 I.0001 ! п (П1)1 0.0010 ln (m)5 1.0010

In (пт)2 0.0100 In (m)6 1.0100

In (m)3 0.1000 In (m)7 1.1000

{Ix ) и {g;i) - 0,1„..., 2b - 1

lxь(п)о 0.0001 .- gx (n)o 0,00 !

> "(n)1 0.0010 - g» (п)1 0.01 !

» (п)2 0.0100 — - gx (n)2 0.10

Ix (п)30;1000 - - gx (n)30.11

IxЬ(П)4 1.0001 — gx (П)4 1,00

Ix (П)5 1.0010 -- gx (n)5 1.01 ! х (п)6 1.0100 "— - gx (п)6 1,10

Ix (n)7 1.1000 = gx (n)7 1,11

Слева от точки — знаковый разряд, причем "0" — соответствует положительному числу, а "1" — отрицательному.

Рассчитывают несовпадающие абзацы памяти Qm, Как отмечалось, количество несовпадающих абзацев памяти Qm равно количеству несовпадающих коэффициентов фильтра

„{Inp ).

Для определения р-го абзаца памяти

Qm необходимо р-й коэффициент фильтра из множества {Inp умножить на все возь. можные значения !» (n) из множества (Ix ), ь

Dm дзндс — 1дс — 2 д1 дО

45 с

Я» где в показателях степени указаны номера разрядов (их веса) при представлении номера такта l3m внутри рециркуляционного цикла и преобразованных отсчетов переменных шагов квантования входных сигналов gx . двоична-позиционным, соответствен но ус и с-разрядным кодом.

Выбор типа ППЗУ осуществляется в зависимости от требуемой организации памяти, т.е, в зависимости от требуемого объема памяти и длины информационных кодов, методика определения которых рассмотрена.

Техническая реализация предлагаемого устройства.

В табл, 3 и 4 в качестве примера приведены кодовые комбинации, соответствующиеь результатам произведения In (m)6{Ixi )

И In (П1)ф» } т.Е, ЗаПИСаННЫЕ В абэаЦаХ Па5 мяти Qm u Qm где результаты умножения

5 приведены в дополнительном коде, при этом учтено, что результатом умножения двух Ь-разрядных двоично-позиционных чисел, представленных унитарными кодами, 10 является (2Ь-1)- разрядное двоично-позиционное число, также представленное унитарным кодом; д» вЂ” адреса, по которым внутри абзацев памяти должны быть записаны требуемые кодовые комбинации.

15 Для определения знакового разряда произведения необходимо придерживаться следующего правила; если знаки сомножителей в произведении In (п-m)In (m) совпадаь ь ют, то произведению присваивается знак

20 "+" и в знаковый разряд вписывается "0", а . если знаки не совпадают, то произведению присваивается знак "-" и в знаковый разряд вписывается "1", Аналогичным образом определяются и

25 остальные абзацы памяти; Qm, Qm, Qm, О. 1, 2.

Оп Qm .

3. 4

Расчитанные абзацы памяти образуют множество {Qm }, где i = 0;1;...;2 + - 1.

В рассматриваемом примере с = 2, следова30 тельно I =О;1;2;...;7, Составление материала необходимого для программирования запоминающего устройства.

Для каждого коэффициента фильтра из

35 множенства {! (m)}, где m = 1;2;....;М, в заь висимости от их значений выбирается абзац памяти Qm из множества {Qm ) и записываi ется по адресу: ,и — 1

O»" =O n ...O2, О1

163 t706

Блок 3 должен обеспечивать хранение и сдвиг М-1 значений с-разрядных двоичнопозиционных чисел выражаемых значения

lx (n-m). ь ь

Для реализации произведения

lx (и-m)ln (m) используется предварительно запрограммированный блок 6, Для построения преобразователя 2 в зависимости от значений b необходимо составить таблицу, аналогичную табл. 1, и в соответствии с ней синтезировать цифровое устройство, Принцип построения и анализ кодера 1 известен.

В исходном состоянии в блоке 3 должны быть записаны накапливающие сумматоры

7, 8 и 9, которые должны быть обнулены.

Остальные элементы схемы должны находиться в заторможенном состоянии.

Работа фильтра состоит из рециркуляционных циклов с длительностью Тц

Т„=

fg (11)

Каждый рециркуляционный цикл делится на M тактов с длительностью Тт

Тт =

1 (12)

Я

В начале каждого рециркуляционного цикла в блок 3 вводится очередное, преобразованное в преобразователе 2 значение переменного шага квантования g, (n) и знаковый разряд ap(n), соответствующие входному сигналу.

Работа ЦФ начинается с формирования в кодере 1 знакового разряда ap(n) и переменного шага квантования!». {и), преобразуь емого при помощи преобразователя 2 в

gx (и). При этом коммутатор 5 подключает к .блоку 3 преобразователь 2 и кодер 1, в результате в блок 3 записываются полученные значения gx (и) и ао(п). После записи в блок

3 коммутатор 5, переключаясь, подключает друг к другу вход и выход блока 3, т.е. обеспечивает рециркуляционный режим его работы. Коммутатор 5 сохраняет свое состояние е течение всего рециркуляционного цикла до введения очередных новых значений переменного шага квантования и знакового разряда входного сигнала. Одновременно с записью в блок 3 значения о» (n) и ao(n) подаются на адресные входы А „,.А блока 6, чем осуществляется установка адреса, по которому производится выборка результата произведения Ix {и-m)ln (m) в заь ь висимости от gx (n) и ат(п). Выборка абзаца памяти Ое в зависимости от коэффициента фильтра In (пт) осуществляется подачей на ь с +,И адресные входы Я ...А - двоична-позиционного,и -разрядного числа соответствующего номеру такта внутри

55 рециркуляционного цикла. Это число формируется на выходе счетчика 4, на тактовый вход которого подаются импульсы с частотой Mfg, используемые в фильтре для тактирования внутри рециркуляционных циклов, Сформированная таким образом адресная информация обеспечивает считывание из блока 6 результата произведения

1» (n-m)ln (m), соответствующего данному ь ь

gx (n-m) и ao(n) и номеру такта m, или, что тоже самое; коэффициенту In (тп). С выхода ь блока 6 результат произведения!» (n-m)ln (m) ь поступает на первый накапливающий сумматор 7, в котором осуществляется постоянное цифровое суммирование на интервале рециркуляционного цикла. На остальных тактах рециркуляционного цикла производится сдвиг на один такт информации, записанной в блок 3, и увеличение на единицу номера такта, формируемого на выходе счетчика 4, т,е. для данного и при изменении

m от 0 до М определяется новая адресная информация по выборке абзаца памяти Оп и выборке результата произведения

Ix (n-m)l (m) из этого абзаца памяти Qm. ь ь

Следовательно, в течение рециркуляционного цикла для данного и при изменении и от 0 до М определяются остальные значения lx (и-m)ln (m). В конце каждого рециркуляционного цикла полученная в первом накапливающем сумматоре 7 сумма передается во второй накапливающий сумматор 8, а сумматор 7 обнуляется, Обнуляется также и счетчик 4. Для данного и все M значений произведения Ix (n-m)I (m) опреь ь деляются в течение последних М рециркуляционных циклов. В момент ввода переменного шага квантования 4 {n+ М -1) ь значение переменного шага квантования

I» (п) теряется. Сумматоры 8 и 9 в соответсть вии с алгоритмом (1) реализуют постоянное цифровое суммирование. На выходе сумматора 9 формируется выходной сигнал Y (N), выраженный двоична-позиционным I-разрядным кодом и имеющий частоту дискретизации, равную частоте дискретизации сигнала ДМПИ.

Таким образом, кодер 1, преобразователь 2 и сумматоры 8, 9 тактируются с частотой дискретизации ДМПИ, а остальные узлы схемы тактируются с повышенной частотой.

Формула изобретения

Последовательный цифровой фильтр, содержащий кодер, вход которого является входом последовательного цифрового фильтра, преобразователь кода, вход которого соединен с выходом шага квантования кодера, коммутатор, информационные и знаковый разряд первого входа которого соединены с выходом преобразователя ко1631706

Таблица 1

Таблица 2 да и выходом знакового разряда кодера ооответственно, блок памяти и сдвига, выход информационных и знакового разрядов которого соединен с информационными и знаковым разрядами второго входа коммутатора соответственно, информационные и знаковый разряды выхода которого соединены с информационными и знаковым разрядами входа блока памяти и сдвига соответственно, и последовательно соединенные первый, второй и третий накапливающие сумматоры, выход третьего из которых является выходом последовательного цифрового фильтра, входом сброса которого является вход сброса первого накапливающего сумматора, о т л и ч а юшийся тем, что. с целью упрощения последовательного цифрового фильтра за счет исключения блока памяти и сдвига, введены счетчик, тактовый вход которого явля5 ется тактовым входом последовательного цифрового фильтра, и блок постоянной памяти, первая группа разрядов адресного входа которого соединена с разрядами выхода счетчика, вход сброса которого

10 соединен с входом сброса первого накапливающего сумматора, вход которого соединен с выходом блока постоянной памяти, вторая группа разрядов адресного входа которого соединена с информационными и

15 знаковым разрядами выхода блока памяти и сдвига.

1631706

Qm

Таблица 3

Таблица 4

1631706

Составитель С.Музычук

Техред M.Ìîðãåíòàë Корректор М.Демчик

Редактор М.КФлемеш

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 555 Тираж 443 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5