Устройство для измерения частоты

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 5 G 01 R 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ îÊ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4398693/21 (22) 29.03,88 (46) 07.03.91. Бюл. М 9 (71) Харьковский авиационный инсти— тут им. Н.Е.Жуковского (72) В.А.Писарев, Л.А.Краснов, В.И.Шульгин и A.Ï.Карюк (53) 621 317(088.8) (56) Авторское свидетельство СССР

Ф 1013867, кл. Г 01 R 23/ОО, 1983.

Авторское свидетельство СССР

Ф 868690, кл Г 04 F 10/00, 1981. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАГТОТЫ (57) Изобретение относится к радиоизмерительной технике и может быть использовано для измерения час-.оты при анализе радиолокационной информации в системах связи, телеметрии, „„SU„„1 3365 А1 системах радионавигации и технике траекторных измерений. Целью изобретения является повышение достоверности, Устройство для измерения частоты содержит формирователь 1 пересечений нуля, формирователь 2 чисея, соответствующих командам пересечений нуля, последовательно соединенные блок 3 управления, блоки 4 и 5 памяти,последовательно соединенные буферный регис1р б,решающий блок 7и накапливающий сумматор 8. Повышение достоверности достигается тем, что оценка периода (частоты) измеряемого сигнала формируется по приходу каждого сигнала пересечения нуля. При этом уменьшается смещение оценки информационного параметра, повышается частота среза, 4 ил.

1633365

30 тоты.

Блок 4 памяти (фиг.2) содержит

55 следовательно соединенные счетчик 9 адреса и оперативное запоминающее устройство (ОЗУ) 10, первый вход которого является вторым входом блока 4 Изобретение относится к радиоизмерительной технике и предназначено для измерения частоты при анализе радиолокационной информации в систе5 мах связи, телеметрии, системах радионавигации и технике траекторных измерений.

Цель изобретения — повышение достоверности. 1О

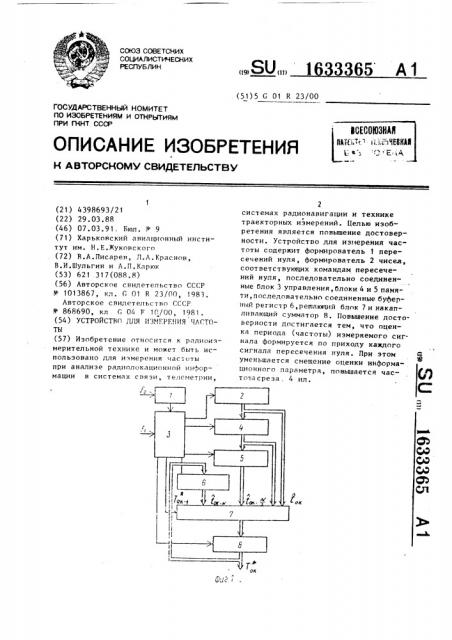

На фиг. 1 представлена блок-схема устройства для измерения частоты, на фиг. 2 — расширенная блок-схема устройства, раскрывающая структуру ее составных частей, на фиг. 3 принципиальная схема блока управления, на фиг. 4 — временные диаграммы, поясняющие работу устройства.

Устройство для измерения частоты содержит формирователь 1 нуль-пересечений, формирователь 2 чисел, соответствующих моментам нуль пересечений, последовательно соединенные блок 3 управления, блоки 4 и 5 памяти, последовательно соединенные 25 буферный регистр 6, решающий блок 7 и накапливающий сумматор 8, Выход накапливающего сумматора 8 является выходом устройства и соединен с первым входом буферного регистра 6, второй вход которого подклю— чен к четвертому выходу блока 3 управления, второй выход которого через формирователь 2 чисел, соответствующих моментам нуль-пересе- 35 чений, подключен к второму входу блока 4 памяти и третьему входу решающего блока 7, второй вход которого подключен к ныходу блока 5 памяти, четвертый вход решающего бло- 40 ка 7 соединен с выходом блока 4 памяти, второй вход которого подключен к третьему выходу блока 3 управления, пятый и шестой выходы которого соединены соответственно с пятым 45 входом решающего блока 7 и вторым входом накапливающего сумматора 8.

Вход формирователя 1 нуль-пересечений является нходом устройства, а выход формирователя 1 нуль-пересече50 ний соединен с первым входом блока 3 управления, второй вход которого соединен с шиной сигнала эталонной часпамяти, а выход — выходом блока 4 памяти. Второй вход ОЗУ 10 и вход счетчика 9 адреса представляют собой первый (групповой) вход блока 4 памяти.

Блок 5 памяти (фиг.2) содержит последовательно соединенные счетчик 11 адреса и ОЗУ 12, первый вход которого является первым входом блока 5 памяти, а выход — выходом блока 5 памяти. Вход счетчика 11 адреса и второй вход ОЗУ 12 представляют собой второй (групповой) вход блока 5 памяти.

Решающий блок 7 (фиг2) содержит регистр 13 и арифметико-логические устройства (АЛУ) 14-16, выход АЛУ 15 является выходом решающего блока 7, а первый и второй входы соединены соответственно. с ньжодом регистра

13 и выходом АЛУ 14, первый вход которого является четвертым входом решающего блока 7, а второй вход соединен с выходом АЛУ 16, первый и второй входы которого являются соответственно вторым и третьим входами решающего блока 7, первый вход которого является первым входом регистра 13, второй и третий входы которого представляют собой пятый (групповой) вход решающего блока 7, Накапливающий сумматор 8 (фиг.2) содержит последовательно соединенные

АЛУ 17 и регистр 18, выход которого является выходом накапливающего сумматора и соединен с первым входом

AJIY 17, второй вход которого является первЫм входом накапливающего сумматора. Второй и третий входы регистра 18 представляют собой второй (групповой) вход накапливаю@его сумматора 8.

Блок 3 управления (фиг.3) содержит блок 19 начальной установки, выполненный на элементах 2И-НЕ 20-22, триггере 23 и счетчике 24, и блок 25 управления устройством, выполненный на счетчике 26, дешифраторе 27, триггере 28 и элементах 2И-НЕ, 29 и 30.

Инверсный выход триггера 23, выход элемента 2И-НЕ 29 и четвертый выход дешифратора 27 представляют собой второй (групповой) выход блока 3 управления. Третий выход деп|ифратора 27 является первым и четвертым выходом блока 3 управления. Второй выход лешифратора 27 является третьим выходом блока 3 управления. Первый выход

33365 6

4 "- и и

-л-— и

Блоки 4 и 5 памяти рел IH 1уют запись типа "очерель" по принципу первый пришел — первый ушел и имеют объем N/2. Счетчики 9 и 11 ллресл счетчики делителя va N/2. Поскольку АЛУ вЂ” этом комбинлционные логиче5 16 дешифраторл 27 является пятым выходом блока 3 управления. Прямой выход триггера 23 является шестым выходом блока 3 управления.

Первые входы элементов 2И-НЕ 21 и 22 являются первым и вторым входами блока 3 управления.

Устройство для измерения частоты работает следующим образом.

Измеряемая частота f поступает о на формирователь 1 нуль-пересечений, где преобразуется в поток коротких импульсов, соответствующих моментам нуль-пересечений, поступающий на блок 3 управления Кроме этого, на блок 3 по шине сигнала эталонной частоты поступает частота эталонного генератора f1, которля значительно (на 3-4 порядка) выше частоты f

По приходу импульса, соответствующего очередному k-тому моменту нуль-пересечения (фиг.4), срабатывает триггер 28 (фиг.3). Он запирает ключ 29 и прекрлщлет подачу частоты f (сигнлл У ) на вход счет1 чика, составляющего формирователь 2 (фиг.2), в результате в счетчике 2 фиксируется оценка очередного ин1 тервала

В этот же момент нл выходе бло1 ка 4 памяти действует оценка

1 на выходе блокл памяти 5 t k, в регистре 13 хрлнится резульч лт пред% последнего измерения Т „, а в регистрах 6 и 18 последнего, т.е.

Ф

TOk 1 °

Здесь N — число-нуль-пересечений, л Ф вЂ” t

k - pj

j=1

Я л где t = t — t — оценка интерва0} 1 )-1 ла между двумя соседними нуль-пересечениями, Н = k-H f2+ i

k-—

2 о о

=k-К+<

Ю

55 ские схемы, то практически в этот же момент с задержкой только на время, необходимое для прохождения »ерез них электрического сигнала, на выходе АЛУ 17 образуется очередная оценка Т,1,. Умножение на два оценок

Ф

1 и g реализовано подключением выхоо k-2 дов блока 4 памяти и регистра 18 к соответствующим входам АЛУ 14 и 17 со сдвигом на один разряд в сторону старших разрядов.

Инвесрным выходом триггер 28 разблокирует счетчик 26. Частота f» поступает на счетчик 26 и через элемент 2И-НЕ 30 — на стробирующий вход дешифратора 27.

В течение последующих четырех импульсов частоты f» на выходе дешифратора 27 формируются четыре сдвинутых во времени управляющих импульса Y -Y (фиг.4). Последний импульс

Y < возвращает триггер 28 в исходное состояние и подготавливает его к приему следующего (k-1)-го нуль-пересечения.

Под действием управляющих сигналов У2-У в устройстве для измерения частоты rыполняются следующие операции.

По сигналу Y в регистр 18 запи2

Ф сывается очереднля оценка Т О, образовавшаяся нл выходе АЛУ 17.

По сигналу У> оценка Т б1,, переносится из буферного регистра 6 в регистр 13. Этим же сигналом оценка

1 дейс т в ующая нл выходе блока 4 (Э

2 памяти, записывается в блок 5 памяти л на место оценки t

П1 сигналу У < оиенкл Т из регисток ра 18 записывается в буферный регистр 6 (в регистре 18 онл сохраняется). Этим же сигналом в блок 4 пал мяти нл место оценки t kH заносится л оценка t „k с выхода формирователя 2 чисел, соответствующих моментам нуль-пересечений.

По сигналу У> увеличивается на единицу адрес в счетчиках 9 и 11.

Соответственно нл выходе блоков 4 и

5 памяти появляются оценки

О1- — +1

» z. и 1О . Поскольку счетчики 9 и 11 представляют собой делители нл И/2, то записанные в блоки 4 и 5 памяти

А л оценки С и t,1 появляются на выходах зтих блоков через Х/2 нульпересечений и уже соответствуют

1633365 л и оценкам t N u t 1, N для пришед0 шего в этот момент нуль-пересечения. Кроме, того по сигналу У в счетчик-формирователь 2 чисел, соответ- 5 ствующих моментам нуль-пересечений, вместо оценки г.01, записывается константа "4", которая распаяна на его установочных входах. Этим компенсируются те четыре импульса частоты f, которые использованы для формирования управляющих сигналов У -У5.

Сигналом Y триггер 28 приводит5 ся в исходное состояние, открывает элемент29 и на счетный вход счетчика 2 поступает частота f, начиная формировать следующую оценку t < в новом цикле измерения.

Схема начальной установки срабатывает по сигналу "Начальная установка" при первоначальном запуске устройства или при повторных запусках при обнаружении сбоев в его работе.

По сигналу Начальная установка" происходит запись константы 4 (N+1) в счетчик 24 и срабатывает триггер

23, которьп1 формирует управляющие сигналы Y<, Y и, переключая элементы 21 и 2?, подает на вход триггера 28 вместо измеряемой частоты о более высокую частоту f< . Сигнал У< подается на вход установки нуля К регистров 6, 13 и 18, à Y7 — на вход установки нуля счетчика 2. Поскольку эти входы управляются потенциалом, 35 а не фронтом, то на выходе счетчика

2 и регистров 6, 13, 18 будет ноль независимо от других управляющих сигналов до тех пор, пока не будут сняты сигHBJlb1 Y6 H Y7 °

Через шлемеHT 22 частота f посту1 пает на вход "-1" счетчика 24, а через элемент 20 — на вход триггера 28 до тех пор, пока в счетчике 24 не останется "ноль". Тогда сигналом " c 0" 45 ан приведен в исходное состояние триггер 23 и окончит цикл начальной установки. В счетчик 24 занесена константа 4 (N+1), поэтому схема управления выполняет описанньп1 N+1 раз цикл пе- 50 резаписи, формируя каж,.,ый раз па 4 управляющих сигнала У -У, но так как счетчик 2 и регистры 6, 13, 18 находятся в состоянии "ноль", то нули записываются во все ячейки блоков 4 55 и 5 памяти, чем и ocóãI»còâëíåтся Hÿчальная установка устройства.

Поскольку част<>та f< значительно выше частоты fo, цикл начальной ус— тановки протекает достаточно быстр 1, абьп1до менее чем за один нериод часто1ы fo.

Таким образом, в устройстве для измерения частоты ралиэован алгори1м

+ N 1 N У— Т = 2 — Т вЂ” — Т +

4 ok 4 ok1 4 ok z

A A t ok — 2 й+"

ok — 0

2 который позволяет получать скользяМ щую оценку Т <по приходу каждого k-го нуль-пересечения.

Для реализации алгоритма необходимо запоминать две предыдущие а <ики периода измеряемого сигнала Т

%

ak-1 и Т „а также N последних оценок л инт»Рвалов tîk- „. . .tîk

Таким образом, в устройстве для измерения частоты повышена достоверность эа счет того, что оценка периоМда (частоты) Т k измеряемого сигнала f формируется в нем по приходу каждого нуль-пересечения, при этом уменьшается смещение оценки информационного параметра и повьпнается частота среза.

Ф о р м у л а и з о б р е т е и и я

Устройство pJIsl измерения частоты, содержащее формирователь нуль †п»сечений, формирователь чисел, соотвеIствующих момен1ам нуль-пер»сечений, последовательно соединенные буферный регистр, решающий блок и накапливающий сумматор, а также первый блок и;1 мяти, выход которого соединен с вторым входом решающего блока, выход Н1 капливающего сумматора является выходом устройства и подключен к первому входу буферного регистра, о тл и ч а ю щ е е с я тем, чта с 11»лью повышения достоверности, т1 него введены последовательно соедин»нные блок управления и второй блок памяти

) выход формирователя чисел, сооз ветствующих моментам нуль-пересечений, соединен с вторым входом второго блока памя1и и третьим входом р»шан1щего блока, выход второго блока па— мяти подключен к первому входу и»рвога блока памяти и к четвертому входу решакщега блока, выход формирователя нуль-пересечений подключен перво:1у входу блока управления, н1орой, третий, четвертый, пятый и

1633365

io шестой выходы которого соответственно к входу чисел, соответствующих пересечений, к второму под ключ ены, формир она теля моментам нульвходу первого блока памяти, второму входу буферного регистра, пятому входу решающего блока и второму входу накапливающего сумматора.

1633365 уП

Фиг

4u(Ф

Составитель Ю.Минкин

Текред A.Êðàâ÷óê

Редактор О.Головач

Корректор В.Гирняк

Заказ 616 Тираж 426 Подписное

БНИИПИ Государстве. ного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, K-35, Раушская наб,, д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101