Многоканальное устройство для ввода информации

Иллюстрации

Показать всеРеферат

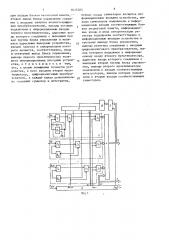

Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и в устройствах цифровой обработки сигналов. Цель изобретения - повышение точности устройст- Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и в устройствах цифровой обработки сигналов. Целью изобретения является повышение точности устройства. На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема блока управления, . на ва. Цель достигается тем, что в устройство , содержащее п каналов 1i лвода аналоговой информации, каждый из которых содержит блок 21 аналоговой памяти и аналого-цифровой преобразователь 31, а также первый мультиплексор 4, регистр 5 и блок 6 управления , введены второй мультиплексор 9 и цифроаналоговый преобразователь 10, а в каждый канал 11 ввода аналоговой информации - сумматор 71 и интегратор 81„ Повышение точности многоканального устройства ввода достигается за счет частотного разделения полезного сигнала помехи. Коррекция сигнала помехи осуществляется независимо от основного сигнала и происходит одновременно с работой канала преобразования информации. Применение контура коррекции в низкочастотной области передаточной характеристики канала позволяет исключить погрешность напряжения смещения аналоговых блоков канала преобразования информации и тем самым повысить точность устройства. 3 ил. ю (Л фиг.З - временная диаграмма работы устройства. Многоканальное устройство ввода узкополостных сигналов содержит п каналов Н ввода аналоговой информации (), каждый из которых содержит блок 2 аналоговой памяти и ана- . лого-цифровой преобразователь 3, мультиплексор 4, регистр 5 и блок 6 управления , а в каждом канале дополни- О СО СО СО 00 со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1633383 А 1 (51) 5 .С 06 Р 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АSTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTNPbfTHRM

ПРИ ГКНТ СССР (21) 46754О5/24 (22) 11. 04. 89 (46) 07,03. 91. Бюл. Р 9 (71) Особое конструкторское бюро

"Миус" при Таганрогском радиотехническом институте им. В.Д.Калмыкова (72) Б.М.Строцкий (53) 681.327(088-.8) (56) Авторское свидетельство СССР

Р 1339892, кл. Н 03 N 1/60, 1985.

Патент США Р 4651131, кл. Н 03 М 1/20, 1984.

Чернов В.Г. Устройства ввода-вывода аналоговой информации для цифровых систем сбора и обработки данных. — М.: Машиностроение, 1988, с. 184. (54) МНОГОКАНЛПЬНОЕ УСТРО11СТВО ДЛЯ

ВВОДА ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и в устройствах цифро" вой обработки сигналов. Цель изобретения — повышение точности устройстИзобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и в устройствах цифровой обработки сигналов.

Целью изобретения является повышение точности устройства.

На фиг.1 представлена структурная схема устройства; на фиг.2 — структурная схема блока управления, . на

2 ва. Цель достигается тем, что в устройство, содержацее п каналов 1д .ввода аналоговой информации, каждьп1 из которых содержит блок 2i аналоговой памяти и аналого-цифровой преобразователь 3i а также первый мультиплексор 4, регистр 5 и блок 6 управления, введены второй мультиплексор 9 и цифроаналоговый преобразователь 10, а в каждый канал 1i ввода аналоговой информации — сумматор 7i и интегратор Hi. 11овьппение точности многоканального устройства ввода достигается за счет частотного раздел:.:ч.ия полезного сигнала помехи. Коррекция сигнала помехи осуществляется независимо от основного сигнала и происходит одновременно с работой канала преобразования информации. Применение контура коррекции в низкочастотной области передаточной характеристики канала позволяет исключить погрешность напряжения смещения аналоговых блоков канала преобразования информации н тем самым повысить точность устройства. 3 ил. фиг.3 — временная диаграмма работы устройства.

Многоканальное устройство ввода узкОПОЛОстных сигналОв coof pæèò и каналов 1i ввода аналоговой информации (i=1n), каждый из которых содержит блок 2 аналоговой памяти и аналого-цифровой преобразователь 3, мультиплексор 4, регистр 5 и блок 6 управления, а в каждом канале дополни1633383 тельно — сумматор 7 и интегратор 8, устройство содержит дополнительно второй мультиплексор 9 и цифроаналоговый преобразователь 10.

В блоке 6 управления выход тактового генератора 11 подключен к первым входам первой 12 и второй 13 схем И, вторые входы которых соединены соответственно с прямым и инверсным выходом триггера 14, выход первой схемы И 12 соединен .со счетным входом первого счетчика 15, выходы которого подключены к входам первого дешифратора 16, а выход второй схемы И 13 соединен со счетным входом второго счетчика 17 и через линию

18 задержки и формирователь 19 поступает на выход блока 6 управления

11 II

»»;l с»»с»»у За»н»сь в оперативную память

Первый выход первого дешифратора 16 является первым ныходом блока 6 управления, второй выход первого дешифратора 16 является вторым выходом блока 6 управления, а третий через второй сюрмс»рователь 20 подключен к установочному входу триггера 14, еди. ничньп» вход которого соединен с устассоночссьсь»»с входами первого 15 и второго 16 счетчиков, со счетно входом третьего счетчика 21 и подкссючен к выходу третьего формирователя 22, вход которого соединен с выходом третьей схемы И 23, первый вход которой соединен с выходом второго дешиф35 ратора 24, а второй является управляющим входом блока 6 управления. Выход второго счетчика 17 является выходной»»пс»»ос» адреса блока 6 управления, а также соединен с входом второго дешис»ратора 24 и с первым входом схемы 25 совпадения кодов, выход которой является третьим выходом блока 6 управления, а второй нход соединен с группой старших разрядов тре 4 тьего счетчика 21, которая одновременно является второй выходной ши ной адреса блока 6 управления.

Устройство работает следующим образом.

При наличии разрешающего потенциала на управляющем входе блока 6 управления (фиг.3) на ее первом выходе формируется импульс управления выборкои блоков 2 аналоговой памяти одновременно по всем каналам ввода анало55 говой информации. Осуществляется выборка уровня аналоговых сигналов по всем каналам. Причем аналоговые сигналы поступают на входы блоков 2 через суиматорь» 7 н каждом канале, гце к узкополосному нходному сигналу добавляется постоянное напряжение

1 равное приведенному к нходу напряжению смещения тракта преобразования, но с обратным знаком.

После завершения процедуры выборки с второго выхода блока 6 управления вырабатывается сигнал запуска аналого-цифровых преобразователей, который подается на управляющие входы всех аналого-цифровых преобразователей 3 одновременно всех каналов ввода аналоговой информации. После процедуры кодирования на выходной адресной шине блока 6 управления последовательно начинают формироваться адреса каналов многоканального устройства ввода данных. Эти адреса управляют мультиплексором 4, который последовательно подключает выходы аналогоцифровых преобразователей 3 каналов ввода апалогоных данных к выходной пп»не данных устройства„ Одновременно блок 6 управления формирует синхроимпульс сопровождения адреса канала на выходкой шине адреса и данных по каналу на»зьсход»»ой шине данных. Таким образом осуществляется процедура чтения да»псих. После проце" дуры чтения цикл работы устройства повторяется.

Параллельно с механизмом преобразонапия и чтения данных по каналам работает механизм коррекс»»си погрешности сиещения по каналам. Сущность работы механизма коррекции погрешности смещения заключается в следующем. По адресу на второй адресной шине блока 6 управления второй мультиплексор 9 последовательно подключает выход цифроаналогового преобразователя 10 к входам интеграторов 8 в каналах ввода аналоговой информации. Причем время подключения каждо-. го канала значительно превосходит цикл работы устройства преобразования и ввода. Например, за время подключения интегратора Bi i-ro канала долкно осуществиться не менее

1024 кодирований по кана»су. Одновременно с третьего выхода блока 6 управления осуществляется запись данных в регистр 5 только с выхода того канала, интегратор которого в данньп» момент подключен к выходу второго мультиплексора 9. Таким образом, вы1» 33383

35 с»»язи бран»ппr и да«»пп» момент канал ввода аналоговой информации по адресу на нторой адресной шине блока 6 упранления оказывается некоторое время охваченным отрицательной обратной связ зью через цифроаналоговьп» преобразователь 10 и интегратор 8 канала. Реализация такой обратной связи позволяет устранить на низких частотах 10 погрешность смещения с точностью цепи обратной связи, т.е. свести ее к уровню погреш»»ост»»»тифроа»»а»»огового преобразователя 10 и интегратора 8.

Ио так как цепь работает на низкой частоте, то позволяет достигать высокого уровня точ»»ости„ . Зто позволяет значительно снизить требования к широкополосным узлам по стабильности напряжения смещения н канале ннода 20 аналоговой »п»формации, т,е. к сумматору 7, блоку 2 аналоговой памяти и аналого-цифровому преобразонателю 3.

Второй мультиплексор 9 последовательно но времени подключает входы 25 интеграторов 8 различных ка»»алов ввода аналоговой информации к выходу цифроаналого«ого преобразователя 10.

Сигнал на, третьем »»ьгходе блока 6 управления формируется « такой мо- 30 мент цикла чтения, что н регистр 5 осуществляется запись данных того канала н«ода аналоговой информации, который и данный момент находится « состоянии коррекции„Те же кг»«а гь», интеграторы 8 которых и данный момент отключены «торым мут»ьт»»»шексором 9, сохраняют на входах суьп<ато— рон 7 величину корректирующего . . аг»ряжения так как»»»»тегра то рь» с От:Jr»<> 40 ченными входами ньп»олняют н дан«< м случае роль аналоговых эапомш»аю»н»х устройств. Соответственно числу каналов многоканального устройства ввода аналогоной информации снижается 4 частота корректируемого напряжения смещения.

Иногока»»а.<»ь»<ая цепь коррекции не влияет на частотную обт»асть пропускания каналов ввода аналоговой »п<формации, н которой:<ежпт спектр частот преобраэуемь»х устропст«ом у«r«»r<>J!n<— ных аналогоньгх сиг »ra;rorr ° I I so< r; rrpo цедуры преобраэо«ания и коррекции протекают»»еэав»»с»»»»о друг от друга и одновременно.

Блок управления 6 работает следуюцим образом

Генератор 11 работает непрерывно и после»»остуш»ения разрешающего сигнала на схему И 23 сброса первого 15 и второго 17 счетчиков соответ. стненно и установки триггера 14 первоначально начинает заполнять первыи счетчик 15 червэ первую схему И 12.

С выхода первого счетчика 15 через первьп» дешифратор 16 фор»а»руются сигналы на первом и втором выходах блока 6 управления, а через формирователь 20 — сигнал сброса триггера

14. После сброса триггера 14 через вторую схему П 13 от генератора 11 начинает заполняться второй счеткик 17,с «ыхода которого формируются адреса опроса каналов в процедуре чте»»»»»». С выхода второй схемы И 13 через Jmrrr!»оса опрашинаемогo канала н режиме ч! < ния и адреса к<Гнала, находящегося в режим» коррекции, формирует на своем «ыходе си«хроимггульс записи с.»о«а данных « регистр цифроаналогового преобраэо«ателя цепи обратной

Ф о р м у л а и э о б р е т е н и я

Иногока»»аль»»ое устройство для ввода информации, содержащее первый му:»ьт»пглек<.оp, регистр, блок управления, а в каждом канале — блок аналогонои памяти, arraJ!o! o-цифровой преобраэо«атель, Ir>r

16333Я3 аншшлиииапдддддддидддщш ..

Don

Сос гавитель Л Видякин fur. 0

Техред А.Кравчук Корректор С.Муска

Редактор И.Дербак

Заказ 616 Тираж 404 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, И-35, Раушская нзб., д. 4/5

Производственно-издательский комбинат Патент", г. Ужгород, ул. Гагарина, 101