Устройство для умножения s-ичных цифр в позиционно- остаточной системе счисления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть испольчовано для построения быстродействующих арифметических устройств, работающих в позиционно-остаточной системе счисления. Цель изобретения - повышение быстродействия и уменьшение объема оборудования. Устройство содержит два блока 1 и 2 хранения констант , два сумматора 3 и 4, четыре блока 5-8 умножения, элемент 9 задержки , шесть блоков 10-15 элементов И, два коммутатора 16 и 17 и соответствующие связи, которые обеспечивают за счет выбора коэффициента 4s избежать возникновения сигнала переноса из сумматора 4 в сумматор 3, а также получить более регулярную структуру устройства за счет применения более современного алгоритма. 1 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Sl)5 G 06 F 7/72

, j "я30И я1:."- .;, :". cgÄiy i(P !! (ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ fHHT СССР

К А BTOPCKOMV СВИДЕТЕЛЬСТВУ (21) 4694508/24 (22) 22.05.89 (46) 07.03.91. Нюл. P- 9 (72) В.Г.Евстигнеев,А.Н.Кошарновскнй, С.Е.Ревзин и A.Á.ÊóçíåöîB (53) 68 1.325(088.8) (56) Авторское свидетельство СССР

962942, кл. Г 06 Г 7/73, 1980.

Авторское свидетельство ГГСР

Р 1236472, кл . Г 06 F 7/7?, 1984. (54) УСТРО!!СТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНИХ ! р р В ЦОяициОннО-or. òÀ o÷HÎÐ систГме

СЧИСЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использонано для построения быстродейству„„SU„„1633401 А 1

2. ющих арифметических устройств, работающих в позиционно-остаточной системе счисления. Цель изобретения — повышение быстродействия и уменьшение объема оборудования. Устройство содержит два блока 1 и 2 хранения констант, два сумматора 3 и 4, четыре блока 5-8 умножения, элемент 9 задержки, шесть блоков 10-15 элементов И, два коммутатора 16 и 17 и соответствующие связи, которые обеспеп.вают за счет выбора коэААициента 7 избежать возникновения сигнала переноса из сумматора 4 в сумматор 3, а также получить более регулярную структуру устройства за счет примене- : ния более современного алгоритма. I ил.

1633401

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействуюших арифметических устройств, работающих в позиционно-остаточной сис5 теме счисления.

Цель изобретения — уменьшение объема оборудования и увеличение быстродействия.

1О

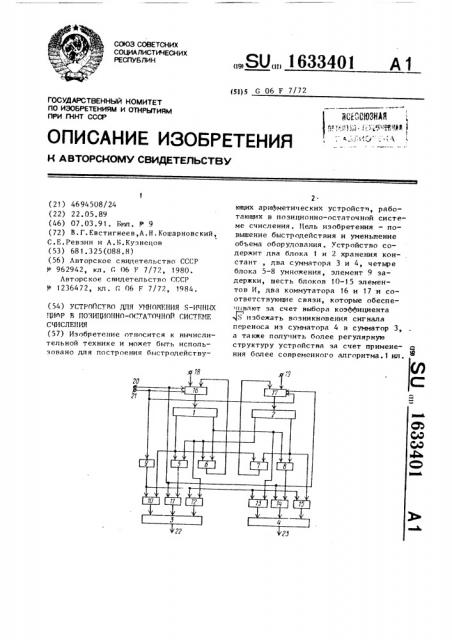

На чертеже показана функциональная схема устройства.

Устройство содержит два блока 1 и

2 хранения констант, два сумматора

3 и 4, четыре блока 5-8 умножения, элемент 9 задержки, шесть блоков

10-15 элементов И, два коммутатора

16 и 17, входы первого 18 и второго

19 операндов устройства, первый 20 и второй 21 тактовые входы устройства,выходы старшего 22 и мпадшего

23 разрядов произведения устройства.

В основу работы устройства для умножения S-ичных цифр в позиционноостаточной системе счисления положе+ ао Ьо < 8 + о 8 ! 0 (1) Второе и третье слагаемые имеют вид

a>" bo S

+-- — — — -=c, S+с + а ° Ь! S

40 о (2) где а, Ь вЂ” значения S-ичных цифр сомножит еп ей; основание внешней позиционной системы счисления, 45

f1= à, +Ь,+с, +d

f,Ь,+ co+do

b = rest (Ь gS)>

Ь, = ent (Ь/ Б) а rest (а/ Я), о а ent (а/ S

1). о = rest (аа Ь, / S) йо = rest (а, Ь)Щ) i с = епс ((а ° b|/QS(/ S > но следующее.

Произведение двух S-ичных цифр имеет вид аешь = (а, PS + ао) (Ь /" 8 + bî)

30 а, Ь,/$ а, Ъ,/Д + à, b / Á + а,. = епг. ((as bo/ S)/PS) (3) где rest(x/у) — остаток от деления х на у; епс(Х/у) — целое число от деления х на у.

Известно, что цифры в S-ичной позиционно-остаточной системе счисления представляются по модулям системы остаточных классов (СОК) я виде а - (N,,Ñ(,, ° ° .,И„), ь = (Р, yPz Рк), где 0(= rest (а/P ), (4) P = гезг (b/Р )

7, К; Р— модули СОК, удовлетворявг ре условию

Г1Р » -S

j=1 где P — взаимно просты.

Для согласования с устройствами, работающими в двоичной системе счис-! ления, в позиционно-остаточных устройствах обычно выбирают S = 2 .УдnáФ нее всего принять m =8 и соответственно S = 2 .= 756 а среди модулей

СОК иметь один, равный Б,в частном случае пусть Р, = .1756 = 16. Это позволяет при аппаратной реализации блоков 1 и 2 хранения констант получить экономичные решения.

Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления работает следующим образом.

По первому тактовому сигналу,поступающему на устройство по входу 20, операнды а = (0(,, 0(,..., b ) и Ь (P,, Pz,...,PK), представленные кодом СОК по модулям Р1, Р .....Р по входам 18 и 19 поступают на коммутаторы 16 и 17, с выходов которых передаются на входы соответствующих блоков 1 и 2 хранения констант, Эти блоки конструктивно представляют собой блоки постоянной памяти на S

2 ° 1-разрядных слов каждьп1, где

К

1 = 1 ; 1 — двоичная разрядность

3 J вычета 0(или P„. В этих блоках в соответствии с выражениями (3) формируются величины а,; а и Ь|, Ь соответственно, которые поступа5 1633401 6 ют на первые и вто ые вхо ь торого соединен с первь»»п» управляющи5-8 умножения. 1» 5 и 8 н ум . лок» 5 и 8 умноже- ми входами первого и второго коммутания фор1»ируют соответственно величины торов и первыми входами первого и а Ь S и л Ь S кот

I д, которые через бло- второго блоков элементов И, второй ки 1! и 14 элементов И пост м в И поступают в

5 тактовый вход устройства соединен с соответствую»>»»»е первьп» 3 и вто ой вторыми управляющими входами первого сумматоры. Одновременно блоками р . д р менно блоками 6 и второго коммутаторов и входом элеи 7 у»»ножения An ми тся вел рмируются величины мента задержки, вь»ход котОРогn сОециа Ь, Я и а, 1,-ф которые пост а- 10 нен с пеРвыми входами тРетьего, четют на вторые ин,»)ормационные входы со- вертого, пятого и шестого блоков элеответственно первого 16 и второго 17 ментов И, выходы пеРвого и второго ком утаторов. Иа этом первый тя т коммУтатоРОВ соеДиненьl соответственботы устройства заканчивается. но с входами первого и второго блоков

Второй такт Работы устройства хранения констант, входы первых со начинается снятием с первого тактово- множителей пеРвого и втоРого 6>локов го вх да 20 сиги а и подачей сигна- УмножениЯ и второй вход тРетьего ла на второй тактовый вхо» 71. По блока элементов И объединены между со этому сигналу величины а ° Ь . -„ В> и бой, второй вход четвертого блока о а, Ь (через вторые и»»ДОР »лц 20 элементов И объединен с входом втовходы коммутаторов 16 и 17 проходят рого сомножителя перв го блока умноня выходы последних, а с их выходов жения и входом первого сомножителя в виде величины с ° " с»1 S u третьего блока умножения, выход котоо поступают ня входы блоков 5-8 умноже Рого соелинен с вторым ин> )ОРмЯЦионнь»м ния, вторые входы блоков 12 и 10 эл 25 входом пеРвого коммутатора, вход втоментов И и перья»е входы 6)локов 13 и рого сомножителя третьего блока ум15 элементов И. Величины с S и »1 S ножения соединен с первым вь»ходом через 6znri»» 10 H 1p 11 с — первого 6znK» хр поступают на сумматор 3 величины с и »1 дом первого сомножителя четвертого > и 0 через блоки 13 и 15 эле„енто„И по 30 блока УмножениЯ, вход второго сомноступают ня суммзтор 4. Перед появлежителя которого соединен с первым нием ня вьг»о1»ях блоков 6 и 7 умножевыходом второго блока хранения конния величии с 4 и с rl сигнал с о» -» о стант, выход второго блока умножения второго тактового входа 21 снимаетсоединен с RTnph)M инА»лц»»о»»нь»м вхося В результате к ьтяте коммутлторы 16 и 1 дом BTopnI ко1»мутатора, выходь» Ilep закрываются. вого и четвертого блоков умножения

1 соединены соответственно с вторыми

Время задержки элемента 9 выбирает- входами первого и второго блоков ся таким, чтобы после снятия сигнала элементов И, выходы третьего перноУ с входа 21 элемента и блоков 10, 13 и го и четвертого блоков элементов И

1 о тавались открытыми до окончания

15 с соединены соответственно с входами процесса суммирования в сумматорах первого, второго ll третьего слагаемых

3 и 4, в результате работы которых первого сумматора, выход которого соедиобразуются старший (с весом S ) и нен с выходом старшего разряда произвемладший (с весом Ы 1 разряды произве- 45 дения устройства, выход мпадшего разряда произведения которого соединен с дения. выходом второго сумматора, входы перФ о рмуля из обретения вого, второго и третьего слагаемых которого соединены гоотвеTcTI>eнно с стройство длЯ УмножениЯ S-ичных 50 выходами пятого, вт 1 г выходами пятого, второго и шестого цифр в позиционно-остаточной г. стеме

Э счисления, содержащее два блока хра- тем, >»TO, с цел ьк) уменьшенения констант, двя сумматора, четыРе ния объема оборудования и увеличения блока умножения ум ния, элемент задержки, быстродействия, вторые вь»ходы первошесть блоков элементов И и два комму- го и второго блоков х»лпе)и татора,первые информационные входы стант соединены соответственно с вхокоторых соединены соответствено с вхо- дами первого и второго сом ожителей дами первого и второго операндов о о локл умноже.ля, первый выход устройства, первый тактовы)» вход ко- первого блока хрлнеьп»я констант со1633401

Составитель F..Èóðýèíà

Редактор А. Козориз Техред И.Дидык Корректор М.Демчик

Заказ 617 тираж 396 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГЕНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæroðîä, ул. Гагарина,101 единен с вторым входом пятого блока элементов И, первый выход второго блока хранения констант соединен с входом второго сомножителя второго блока умножения и вторым входом шестого блока элементов И.