Многоканальное устройство для распределения заданий процессорам

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах для распределения заданий между процессорами. Цель изоб2 ретения - расширение функциональных возможностей за счет учета занятости процессоров и перераспределения заданий по каналам с учетом их занятости. В устройство введены в каждый канал два блока элементов И, два триггера, по два элемента И, ИЛИ, НЕ и три элемента задержки, а в каждый узел арбитража группа элементов И - НЕ и группа элементов НЕ. Устройство обеспечивает перераспределение заданий как при неисправности процессора канала , так и при его занятости решением задач по предыдущему запросу. Любой канал вправе выставить заявку на переадресацию задания, а первый свободный от решения задач исправный канал принимает задание для исполнения. I ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5I)5 G 06 F 9 46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4690118/24 (22) 04.04.89 (46) 07.03.9!. Бюл. № 9 (72) В. А. Невский (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 1124309, кл. G 06 F 9/46, 1983.

Авторское свидетельство СССР № 1427368, кл. G 06 F 9/46, 1987. (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО

ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЯ

П РОЦЕССОРАМ (57) Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах для распределения заданий между процессорами. Цель изобИзобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах для распределения заданий между процессорами.

Цель изобретения — расширение функциональных возможностей за счет учета занятости процессоров и возможности перераспределения заданий по каналам с учетом их занятости.

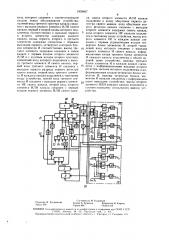

На чертеже представлена функциональная схема устройства.

Устройство содержит регистры I и 2, блоки элементов И 3 — 6, триггеры 7 — 9, элементы И 10 — 12, элементы 13 — 15 задержки, элементы ИЛИ 16 и 17, элементы НЕ 18 и 19, вход группы 20 информационных входов устройства, тактовый вход 21 устройства, информационные выходы 22 устройства, вход

23 неготовности устройства, вход 24 готовности устройства, вход 25 конца обслуживания устройства, общую кодовую шину 26 устройства, узлы арбитража 27 и 28, эле„„SU„.1633407 А 1 ретения — расширение функциональных возможностей за счет учета занятости процессоров и перераспределения заданий по каналам с учетом их занятости. В устройство введены в каждый канал два блока элементов И, два триггера, по два элемента

И, ИЛИ, НЕ и три элемента задержки, а в каждый узел арбитража группа элементов И вЂ” НЕ и группа элементов НЕ. Устройство обеспечивает перераспределение заданий как при неисправности процессора канала, так и при его занятости решением задач по предыдущему запросу. Любой канал вправе выставить заявку на переадресацию задания, а первый свободный от решения задач исправный канал принимает задание для исполнения, I ил. менты И вЂ” НЕ 29, элементы НЕ 30, элемент

ИЛИ 31, сигнальный выход 32 устройства.

Готовность канала к приему кода очередного прерывания фиксируется только при наличии исправного и свободного от решения задач проце;сора.

В первую очередь обслуживаются запросы «своего» канала. При отсутствии

«собственных» запросов формируется Hf нал готовности к принятию информации из общей кодовой шины — кода прерывания «чужого» канала.

При неисправном или занятом решением задач процессоре канал с поступлением запроса получает право занять очередь на переадресацию запроса другим процессорам.

Первый из свободных каналов принимает переадрессованный запрос на обслуживание.

В предлагаемом варианте устройства канал с младшим порядковым номером имеет преимущественное право на переадресацию своего запроса. Это цозволяет ориен1633407

1О

3 тировать каналы с младшими номерами на решение более приоритетных задач.

Устройство работает следующим образом.

Запрос от М-го источника запросов (абонента) заносится в регистр 1 по входу 20.

Причем в первый разряд заносится собственно сигнал запроса, а в остальные — код прерывания. Если М-й процессор, закрепленный для обслуживания запросов от М-го абонента, исправен, о чем свидетельствует единичное состояние триггера 7, и не занят решением задач по предыдущему запросу, о чем свидетельствует единичное состояние триггера 8, то на выходе элемента И 10 будет сигнал единичного уровня. Этот сигнал поступает на управляющие входы блока элементов И 3, Но входу 21 с определенной периодичностью поступают стробирующие сигналы единичного уровня. С приходом на управляющие входы блока 3 стробирующего сигнала информация из регистра 1 через блок 3 передается на информационный выход 22 и далее в систему прерывания процессора. Сигнал запроса через первый элемент И блока 3 поступает на вход элемента 13 задержки. Время задержки выбирается достаточным для принятия кода прерывания процессором. С выхода элемента 13 задержки сигнал запроса через элементы

И;1И 16 и 17 поступает на обнуление триггера 8 и регистра 1 соответственно. Одновременно с обнулением регистра 1 по выходу

32 выдается сигнал о готовности канала принять очередной запрос.

С переходом триггера 8 в нулевое состояние (это означает — процессор занят) на выходе элемента И 10 сигнал нулевого уровня. (То же самое происходит и в том случае, когда процессор оказывается неисправным триггер 7 будет обнулен по входу 23). Сигнал нулевого уровня на выходе элемента И 10 свидетельствует о неспособности процессора данного канала принимать и обрабатывать запросы. С поступлением очередного запроса канал выставляет заявку на переадресацию. Происходит это следующим образом. На первый вход элемента И 12 поступает стробирующий сигнал по входу

21, на второй вход — сигнал запроса с выхода первого разряда регистра 1, а на третий — сигнал единичного уровня с выхода элемента HE 19, на вход которого поступает сигнал нулевого уровня с выхода элемента И 10. Сигнал с выхода элемента И 12 устанавливает триггер 9 в единичное состояние.

Сигнал единичного уровня с выхода триггера 9 поступает на М-й вход М-го элемента

И вЂ” НЕ 29 узла 28. Если предшествующие каналы не нуждаются в переадресации своих запросов, то на выходе М-го элемента И вЂ” НЕ 29 узла 28 появляется сигнал нулевого уровня, который поступает на М-е входы последующих элементов И вЂ” НЕ этого узла, запрещает выставление запросов на переадресацию со стороны последующих каналов, Сигнал нулевого уровня с выхода

4

М-го элемента И вЂ” НЕ 29 поступает на вход

М-го элемента НЕ 30. Сигнал единичного уровня на выходе М-ro элемента НЕ 30 узла

28 означает наличие заявки М-го канала на переадресацию запроса.

Если процессор некоторого канала исправен и не занят решением задач, то данный канал выставляет заявку на загрузку. Происходит это следующим образом. Сигнал единичного уровня с выхода элемента НЕ

10 М-ro канала поступает на М-й вход М-го элемента И вЂ” НЕ 29 узла 27. М-й канал захватывает право на загрузку, так как сигнал нулевого уровня с выхода М-го элемента И†НЕ 29, поступая на М-е входы последующих элементов И вЂ” НЕ 29, блокирует заявки на загрузку последующих каналов. Сигнал нулевого уровня с выхода М-го элемента И вЂ” НЕ 29 поступает на вход М-го элемента НЕ 30. Сигнал единичного уровня на выходе М-го элемента НЕ 30 узла 27 означает наличие заявки М-го канала на загрузку.

Право на переадресацию запроса предоставляется только в том случае, когда хотя бы один из каналов готов к принятию «чужого» запроса. Эта готовность определяется следующим образом. Сигналы единичного уровня с выходов элементов И 10 всех каналов поступают на входы элемента ИЛИ 31 узла 27. Сигнал единичного уровня на выходе элемента ИЛИ 31 означает — есть канал, готовый принять «чу кой» запрос.

Переадресация запроса осуществляется следующим образом. Сигнал единичного уровня с выхода элемента HF. 30 (соответствующего каналу, имеющему право на переадресацию) узла 28 поступает на первый вход элемента И 11 соответствующего канала, на второй вход которого поступает сигнал единичного уровня с выхода элемента ИЛИ 31 узла 27. Сигнал единичного уровня с выхода второго элемента И 11 поступает на управляющие входы блока элементов И

4. Канал не готов к обслуживаию «своего» запроса — на выходе элемента И 10 сигнал нулевого уровня. Этот сигнал поступает на вход элемента HE 19, с выхода которого сигнал единичного уровня поступает на управляющие входы блока элементов И 4. С поступлением по входу 2! очередного стробирующего сигнала единичного уровня на управляюгцие входы блока элементов И 4 информация запроса из регистра 1 через блок элементов И 4 передается в общую кодовую шину 26. Сигнал единичного уровня с выхода первого элемента И блока 4 через элемент 15 задержки поступает на вход элемента ИЛИ 17 и вход обнуления триггера

9. Переход триггера 9 в нулевое состояние означает снятие заявки на переадресацию запроса со стороны данного канала.

Сигнал единичного уровня с выхода элемента ИЛИ 17 поступает на вход обнуления регистра 1. Одновременно с обнулением регистра по выходу 32 объекту выдается

1633407

5 сигнал о готовности канала принять очередной запрос. Время задержки элемента 5 з адерж ки выбирается достаточным дл я ос уществления процедур, связанных с переадресацией, но меньшим, нежели время до прихода очередного стробирующего сигнала еди5 ничного уровня по входу 21. Сигнал единичного уровня с выхода элемента НЕ 30 (ссютветствующего каналу, готовому принять «чужой» запрос) узла 27 поступает на управляющие входы блока элементов И 5 соответ- 10 ствующего канала. Информация запроса из общей кодовой шины 26 через блок 5 поступает в регистр 2. Сигнал единичного уровня с выхода элемента И IO (канал готов к обслуживанию очередного запроса) поступает на управляющие входы блока элементов И 6.

По окончании стробирующего сигнала единичного уровня сигнал нулевого уровня по входу 21 поступает на вход элемента НЕ 18.

Сигнал единичного уровня с выхода элемента НЕ 18 поступает на управляющие входы 20 блока элементов и 6 и информация запроса («чужого») из регистра 2 через блок 6 передается на выходы 22. Сигнал единичного уровня с выхода первого элемента И блока

6 через элемент 14 задержки поступает на вход элемента ИЛИ 16 и на вход обнуления

25 регистра 2. Сигнал единичного уровня с выхода 16 элемента ИЛИ 16 поступает на вход обнуления триггера 8. Нулевое состояние триггера 8 означает канал занят. Время задержки элемента 14 задержки выбирается

30 достаточным для принятия кода прерывания процессором, но меньщим, нежели время до прихода по входу 21 очередного стробирующего сигнала единичного уровня.

Таким образом, предлагаемое устройство организует перераспределение заданий про35 цессором с учетом не только их исправности, но и занятости решением задач по предыдущему запросу. Организация (и реализация) очереди запросов вынесена на уровень всего устройства — занятый канал выставляет заявку на переадресацию очередного запро- 40 са, а любой свободный канал принимает этот запрос на обслуживаие. Такая организация способствует повышению производительности вычислительной системы.

Формула изобретения

Многоканальное устройство для распределения заданий процессорам, содержащее два узла арбитража, каналы, каждый из которых содержит первый и второй регистры, первый и второй блоки элементов И, первый триггер, первый элемент И, причем в каждом канале каждая группа информационных входов устройства соединена с группой информационных входов первого регистра одноименного канала, выходы первого регистра подключены к информационным входам первого и второго блоков элеменгов И, в каждом канале первые управляющие входы первого и второго блоков элементов И подключены к тактовому входу устройства, второй управляющий вход первого блока элементов И соединен с выходом первого элемента И, выходы первых блоков элементов И каналов через монтажное ИЛИ соединены с группой информационных выходов устройства, выходы второго блока элементов И каждого канала соединены с общей кодовой шиной устройства, первый вход первого элемента И подключен к выходу первого триггера своего канала, единичный и нулевоЙ входы первого триггера каждого канала соединены соответственно с входами готовности и неготовности устройства, orëèчающееся тем, что, с целью расширения функциональных возможностей за счет учета занятости процессоров и возможности перераспределения заданий по каналам с учетом их занятости, каждый канал дополнительно содержит третий и четвертый блоки элементов И, второй и третий триггеры, второй и третий элементы И, первый, второй и третий элементы задержки, первый и второй элементы ИЛИ, первый и второй элементы НЕ, а каждый из узлов арбитража содержит группу элементов И вЂ” НЕ и группу элементов НЕ, кроме того первый узел арбитража содержит элемент ИЛИ, причем выход каждого элемента НЕ группы первого блока арбитража подключен к управляющему входу третьего блока элементов И одноименного канала, вход каждого элемента НЕ группы первого арбитража соединен с выходом одноименного элемента И вЂ” НЕ первого блока арбитража и с соответствующими входами всех последующих элементов И вЂ” НЕ первого узла арбитража, выход второго триггера каждого канала соединен с первым входом одноименного элемента И вЂ” НЕ группы второго узла арбитража, другие входы которого подключены к выходам всех предшествующих элементов И вЂ” НЕ второго узла арбитража, выход каждого элемента И вЂ” НЕ группы второго арбитража соединен с входом одноименного элемента HE группы второго узла арбитража, выход каждого элемента

НЕ группы второго узла арбитража соединен с первым входом второго элемента И одноименного канала, выход первого элемента И каждого канала соединен с соответствующим входом одноименного элемента И—

НЕ второго узла арбитража, с входом первого элемента НЕ своего канала и с ссютветству— ющим входом элемента ИЛИ первого узла арбитража, выход элемента ИЛИ первого узла арбитража подключен к вторым входам вторых элементов И всех каналов, выход второго элемента И в каждом канале подключен к второму управляющему входу второго блока элементов И, третий управляющий вход второго блока элементов И канала подключен к выходу первого элемента НЕ своего канала, второй вход первого элемента И канала соединен с выходом третьего триггера своего канала, единичный

1633407

С оста внтел ь М. Кудря шев

Редактор В. Бугренкова Техред А. Кравчук Корректор Н. Король

Заказ 618

Тираж 400 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 1О!

7 вход которого соединен с соответствующим входом конца обслуживания устройства, нулевой вход третьего триггера канала соединен с выходом первого элемента ИЛИ своего канала, первый и второй входы которого подключены соответственно к выходам первого и второго элементов задержки данного канала, входы первого, второго и третьего элементов задержки соединены с первыми выходами первого, четвертого и второго блоков элементов И соответственно, выход третьего элемента задержки соединен в своем канале с первым входом второго элемента

ИЛИ и с нулевым входом второго триггера, единичный вход которого подключен к выходу третьего элемента И своего канала, первый вход третьего элемента И соединен с выходом первого разряда первого регистра своего канала, второй вход третьего элемента И каждого канала подключен к тактовому входу устройства, третий вход третьего элемента И соединен с выходом первого элемента НЕ своего канала, второй вход второго элемента ИЛИ канала соединен с первым входом первого элемента ИЛИ своего кана8 ла, выход второго элемента ИЛИ канала подключен к входу обнуления первого регистра своего канала, вход обнуления второго регистра канала соединен с выходом второго элемента задержки своего. канала, вход второго элемента НЕ каналов подключен к тактовому входу устройства, выход второго элемента НЕ в каждом канале соединен с первым управляющим входом четвертого блока элементов И, второй управлений вход которого соединен с выходом первого элемента И своего канала, информационные входы третьего блока элементов

И каждого канала подключены к общей кодовой шине устройства, выходы третьего блока элементов И в каждом канале соеди15 иены с информационными входами второго регистра, выходы которого подключены к информационным входам четвертого блока элементов И, выходы четвертых блоков элементов И каналов соединены с информационными выходами устройства, выход второго элемента ИЛИ каждого канала подключен к соответствующему сигнальному выходу устройства.