Цифровое устройство фазовой синхронизации

Иллюстрации

Показать всеРеферат

Июбретение относится к технике связи. Цель изобретенияповышение точности синхронизации за счет уменьшения фазовых девиаций выходного сигнала. Устройство содержит опорный генератор 1, формирователь 2 импульсов, блок 3 добавления-вы читания импульсов, блок 4 выделения фронтов , счетчик 5, сумматор 6, регистр 7, блок 8 принятия решений и блок 9 формирования знака. Сигнал с генератора 1 через формирователь 2 и блок 3 поступает на счетчик 5 и далее на сумматор 6. На него поступают гакже сигналы с регистра 7 при смене ровня сигнала в блоке 4. При переполнении матора 6 блок 8 дешифрирует код и выдает сигнал на исключение или добавление импульса на входе счетчика 5 блоком 3, а блок 9 производит коррекцию знака числа в регистре 7 Цель достигается введением блоков 4, 8 и 9 и счетчика 5. 4 ил

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 04 L 7 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (2l) 4694578/09 (22 ) 23. 05. 89 (46) 07.03.91. Вюл. л(е 9 (7l ) Научно-производственное обьедине»»ие

«Автоматика» (72) А. И. Сивожелезов и А. Н. г)евда»»ск»»й (53) 621.394.662 (088.8) (56) Системы фазовой автоподстройки частоты с элементами дискретизации / Под ред.

В. В., Шахгильдяна,— М.: Связь, 1979, с. 152, рис. 4.29.

Авторское свидетельство СС(Р

¹ 1116545, кл. H 04 l 7/02, 1984. (54) ЦИФРОВОЕ УСТРОЙСТВО ФАЛОВОА СИНХРОНИЗАЦИИ (57) Изобретение относится к технике связи.

Цель изобретения повыше»»ие точности

„„SU„. 1633506 А 1

2 синхронизации за счет умсньш»ния фазовыi девиаций выходного сигнала. Устро(» TH() содержит опорный генератор 1, формирователь 2 ил»пульсов, блок 3 добавления-вычитания импульсов, блок 4 выделения фронтов, счетчик 5. сумматор 6, регистр 7, A.í>ê 8 принятия решений и блок 9 формирования знака. Сигнал с генератора 1 через формирователь 2 и блок 3 поступает на счетчик 5 и;»3ëåñ на сул»матор 6. На него постуиакп также сигналы с регистра 7 при смене уровня сигнала в блоке 4. !1ри переполнении сул»матора 6 блок 8 дешифрирует код и выдаеT сигнал на исключение или добавление импульса на входе счетчика 5 блоком 3, а блок

9 производит коррекцию знака числа в р»гисгре 7 Цель достигается введен»»ел» блоков 4, 8 и 9 и счетчика 5. 4 ил.

1633506

Изобретение от(косится к технике связи и может быть использовано для выделения

Т3 K1 оВоН частОты из при пима(<м01 О с иГ113.13. !!ель изобретения — повышение точности синхронизации çd счет ученыпения фазовых дс виаций выхо.(ногo oиг(га 13.

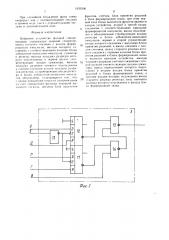

Hd фиг. 1 представлена с грл ктл!>Ная схема цифрового устройства фазовый си(хронизации; на фиг. 2 6;IOK .(обавления-вычитания; на фиг 3 — 6.(ок принятия решений; на фиг. 4 — 6.И>к формирования знака.

Цифровое усгройсгво фазовой синхронизации со.(ерж(гг опорный I енератор 1, формирователь 2 импульс<)B, блок 3 добавленияВ ы ч и т 3 н и я H M I I Ú . 1 üñ o B, 6.10 K 4 в ы;1(. л е и и я фронтов, с етчик 5, сумматор 6, регистр 7, блок 8 принягия решс ний и 0.10К !1 форл(ирования зн;)ка.

Ьлок 3 .(обанления-вычитания импулы ов содержит три(i (. pbi 10 и 11, эл«мент Г(Е 12 и элементы 211-НЕ !3 и 14.

Б. Iîк ч Ipèt(HTèÿ решений сод«ржиT деIIIII(f>P3TOP 11) IBOHЧНО(О К<().13.

Ь.10 к 1 фор 41 и poB

>.(Сл1СHI 11Е 16 и мажоритарный элемент 17.

Форчи рова ге.(1. им пуль!Ов представляет собой сч< тчик с .1("цифра г<>ром, формир tol1lHH сдвину тыс по(I(. (онат<С(ьнос ги ичпульсон А,Ь,Б,ГН

1>. lOK 4 Bt>l, l(.1(. НИ;1 фронтов lip(. t . тан;(Я(T собой lB(. гри(герньк ступ IIH за;(ержки с э,(ел(енточ I I(.I(., 1К1 1ЛК>1!!ЕЕ И, !И на ныЪ 0 I Е, сч ройство pit(>(>1 3(. t следующим 06Р(1 (ОЧ. с игнал с Oilopll<)I(> ГсH(pdTopd I ц рез формирователь 2 и блок 3 (063B.IBHHH-Bhlчит;(ния посту паеT 1(3 в. о,(<. (етчика 5.

1ло эффи ци(н I II(p(. 0

t;,=— - T Ä I l l

Где Т, lit. РиОд с. I(,lонани Я H»111>,льс Ов; т„- длительносгь входнои э.течент3рll< > lt НОС ЫЛ К И.

Текущее (н()ченис кода с выходов млаlших разрядов счетчика 5 поступает Hd группу соответствую(цих входов сумматора 6, на,(ругую группу входов которого поступает код с выходов младших разрядов регистра 7.

Б момент смены уровня Oигна.lа н3 первом входе блока 4 Btl »åë(.ння фронтов по сitl Hd.ti с гроб пру ю(цеBo и л(1(у. I h(а блока ре (лл гаг сум миров,(ния содержимого регистра 7 и теку(пего зн;(чения кода с выходов м 13;(IIIHx ра(рядов счетчика 5 перепи-! ывается н регH(гр 7. (1днонрел(енно в него з,)писывается новое зн,)чсни <Иаков<и.о разряда, котор<зс формируется 6 IOKov () формирования (пака И("<0.(ной инфорл(ацией, не<>бходил(01 для ра(>оты блока 9 формироB3 II1t Я .(113 K it, Я B. l Я(. TÑ Я Л1i 3 I< II È(. <. Òdt) IIIBÃО

p;l (ряда («(гчик,t 5, (II;IHBIIII« старн)его разряда регистра 7 и значение разряда перец<)лнения сумматора 6. Те же исходные данные используются блоком 8 принятия решений для решения вопроса о необходимости .(обавления или исключения импульса на входе счетчика 5 блоком 3 добавления-вычитания импульсов.

В об(цем случае возможны следующие фазовые соотношения между входным и выходным сигналом устройства, а именно:

10 выходной сигнал устроиства опережает

iio фазе входной, при этом в момент времени

1, прихода стробирующего импульса на стробируюьций вход регистра 7 на выходах младших разрядов счетчика 5 записаны коды К

15 1 H(ел, лежащие в интерва 1Р (де h коэффициент пересчета счетчика 5, причем в указанном интервале код на выхо20 дах чладших разрядов счетчика,> рассматринаюг как положительное число, записанное в прямом коде, IlpH этом старший разряд с I(гчика 5 выполняет функцию знакового разряда и в данном конкретном случае, на

«10 выходе устанавливается значение .чогического нуля; выходной си(нал устройства отстает по филе o) входного. при этом в момент времени

<,, прихода стробирующего импульса на стробирукнций вход регистра 7 на выходах млад>О (пих p33psrдов счетчика 5 записаны коды К чисел, .(ежащих в интервале, Ст JtG IV + » 2 !

50 с, i.1е К „абсо.чютное значение числа на выходах младших разрядов счетчика 5 в момент времени t. прихода стробируюшего импульса;

Ki — абсолютное значение числа на выходах младших разрядов регистра 7 в момент времени 1„прихода стробируюгцего импульса.

55 причем в этом случае код на выходах млад35 ших разрядов счетчика 5 рассматривают к IK отрицательное число, записанное в дополнительном коде, знак числа определяется значением старшего разряда счетчика 5, 3 именно, в данном интервале старший раз40 ряд счетчика 5 имеет значение логической единицы; выходной сигнал устройства совпадает по фазе с входным, в этом случае в момент прихода стробирующего сигнала на стробируlolllий вход регистра 7 на выходах счетчи45 ка 5 записывается нулевой код.

Корректируюгцее воздействие возникает только нри сложении кодов чисеч одинакового знака B случае, если выполняется слезук>(цее неравенство

1633506

Алгоритм формирования знакового сигнала на выходе блока 9 формирования знака следующий: если на входы блока 9 поступают одинаковые уровни с выхода старшего разряда счетчика 5 и с выхода старшего разряда регистра 7, выходной сигнал блока 9 равен уровню этих сигналов. Если уровни сигналов с выходов старших разрядов счетчика 5 и регистра 7 не совпадают, сигнал на выходе блока 9 формирования знака имеет значение, равное инверсии значения сигнала на выходе разряда переполнения сумматора 6.

Рассматривают числовые примеры, поясняющие механизм подстройки фазы выходного сигнала, на примере четырехразрядного счетчика, регистра и сумматора, причем старшие разряды счетчика 5 и регистра 7 являются знаковыми.

Пусть в регистр 7 записано число плюс 4, т. е. на выходах младших разрядов записан код 100, старший разряд имеет значение О, а в момент времени 1 прихода стробирующего импульса с выхода блока 4 выделения фронтов на выходах счетчика 5 было записано число плюс 3 (на выходы младших разрядов — 011, старший выходной разряд — О), тогда без учета знаковых разрядов на выходах сумматора 6 имеют

100+011 — 0.111, где на выходах младших разрядов имеют код 111, а на выходе разряда переполнения О.

По стробируюшему импульсу в регистр 7 запишется код числа плюс 7, соответственно младшие разряды 111; и знаковый разряд О.

Поскольку при сложении положительных чисел не выполняется условие (2), а именно

4+3(16/2, то никаких корректирующих воздействий не происходит.

В момент времени 4 прихода стробирующего импульса сумматор 6 произведет суммирование числа плюс 3 с выходов счетчика 5 и числа плюс 7 с выходов регистра 7, т. е. без учета знаковых разрядов в двоичном коде можно записать

011+111= 1.010.

В данном случае поскольку выполнено условие (2)

3+7)8.

Блок 8 принятия решений выдает сигнал на исключение импульса и блок 3 добавления-вычитания импульсов производит исключение одного импульса из импульсной последовательности, поступающей с его выхода на вход счетчика 5 (фиг. 2, сигнал И) .

Таким образом, если получен сигнал переполнения на выходе разряда переполнения сумматора 6 (в нашем случае получено значение ), а на выходах счетчика 5 и регистра 7 сохраняются положительные числа (старшие разряды имеют значение О), блок 8 принятия решений дешифрирует код 4 и выдает сигнал на исключение.

Блок 9 производит коррекцию знака числа по ранее описанному алгоритму и выдает на вход знакового разряда регистра 7 значение О и в регистр 7 по стробирующему им5 пульсу переписывается код положительного числа, который без учета знакового разряда может быть выражен следуюгцей зави Hмостью

gG /

2 (3) 10

МО где К вЂ” значение кода без учета знакового разряда;

К вЂ” код числа на выходах сумматора, при котором произведена коррек15 ция;

Л вЂ” коэффициент пересчета счетчика 5.

Следовательно, в регистр 7 записано число плюс 2 (О OIO, т. е. 010 значение младших разрядов, Π— значение старшего разряда.

Рассматривают работу устройства с отрицательными числами, записанными в дополнительном коде. Ilo аналогии в момент времени t код на выходах регистра 7 равен минус 3 (1101), код íà выходах счетчика 5—

25 минус 4 (1100), тогда в сумматоре 6 без учета знаковых разрядов имеют

100+ 100= 1.001.

Двоичный код 1001 соответствует числу минус 7, записанному в дополнительном коде. При этом корректирующего воздействия на фазу выходного сигнала не происходит (минус 7 ио абсолютному значению меньше 8)

В момент времени 1. код на выходах регистра 7 равен минус 7 (1001), а код на выходах счетчика 5 равен минус 4 (1100), счеЗ5 довательно, в сумматоре имеют

100+001=0. 101.

В данном случае на выходе переполнения сумматора 6 имеют значение 0 (исчез сигнал переноса), а на выходах регистра 7 и счет40

0 чика 5 — отрицательные числа в дополнительном коде (знаковые разряды имеют значение 1) блок 8 принятия решений дешифрирует код 3 и выдает сигнал на добавление (фиг. 5, сигнал 0), блок 3 добавления-исключения импульсов производит коррекцию

45 фазы путем добавления одного импульса в импульсную последовательность, поступающую на вход счетчика 5 (фиг. 2, сигнал И).

Корректирующее воздействие произведено, поскольку абсолютное значение суммы

50 чисел минус 4 и и минус 7 больше, чем число 8, таким образом выполнено условие (2).

Блок 9 производит коррекцию знака числа и выдает на вход знакового разряда регистра 7 значение 1, на выходе младших разрядов которого подается остаток К (3) ж и в регистр 7 записывается число минус 3, представленное в дополненном коде (выходы младших разрядов !О!. выход старшего разряда 1 ).

163350б

При случайном блуждении фазы схема оперирует как с положительными числами в прямом коде, так и с отрицательными числами в дополнительном коде.

Формула изобретения

Цифровое устройство фазовой с инхронизации, содержащее опорный генератор, выход которого соединен с входом формирователя импульсов, выходы которого соединены с соответствующими входами блока добавления вычитания импульсов, сумматор и регистр, выходы младших разрядов которого подсоединены к первой группе соответствукпцих входов сумматора, выходы мл адш их разрядов которого подсоединены к соответствующим входам младших разрядов регистра, а стробирующие входы регистра и блока добавления-вычитания импульсов объединены, отличаюи ееся тем, что, с целью повышения точности синхронизации за счет уменьшения фазовых девиаций выxодного сигна.lа, введены блок выделения фронтов, счетчик, блок принятия решений и блок формирования знака, при этом первый вход блока выделения фронтов является входом устройства, второй и третий входы соединены с ссютветствующими выходами формирователя импульсов, выход подсоединен к объединенным стробирующим входам регистра и блока добавления-вычитания импульсов, первый и второй управляющие входы которого соединены с выходами блока принятия решений, а выход соединен с входом счетчика, выход старшего разряда которого соединен с первыми входами блока принятия решений и блока формирования знака и является выходом устройства, выходы младших разрядов счетчика соединены с второй группой соответствующих входов сумматора, выход переполнения которого подсоединен к вторым входам блока принятия решений и блока формирования знака, к третьим входам которых подсоединен выход старшего разряда регистра, вход знакового разряда которого подсоединен к выходу блока формирования знака.

l633506

Составитель В. Микуцкий

Редактор Н. Рогулич Техред А. Кравчук Корректор М. Самборская

Заказ 623 Тираж 386 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ (.(.СР

I 13035, Москва, Ж 35, Раушслая наб., д. 4, 5

Производственно-издательский комбинат «Патент», r. Ужгород, ул. Гагарина, II) I