Устройство для вычисления модуля вектора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях, в частности при цифровой обработке сигналов с квадратурными составляющими для вычисления модульного значения сигнала в реальном масштабе времени. Цель изобретения - уменьшение аппаратурных затрат. Поставленная цель достигается за счет изменения логики формирования аппроксимирующей зависимости, лежащей в основе вычислительной процедуры. Для этого в устройство, содержащее блок выделения максимума, преобразователь многорядного кода, состоящий из п+1 одноразрядных сумматоров, и сумматор, введены схема сравнения, коммутатор, состоящий из групп элементов И, ИЛИ и регистров. 1 з.п. ф-лы, 2 ил. Ј2 в

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„16351

А1 (gg)g G 06 F 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И (ЛКРЫТИЯМ

ПРИ ГННТ СССР (21) 4703552/24 (22) 09.06.89 (46) 15.03.91. Бюп. ¹ 10 (72) В.E. Козлов (53) 681.325(088.8) (56) Авторское свидетельство СССР № 1429112, кл. G 06 F 7/552, 1987.

Авторское свидетельство СССР № 1559344, кл. G 06 F 7/552, 1988. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ

ВЕКТОРА (57) Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях, в частности при

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях.

Цель изобретения — уменьшение аппаратурных затрат.

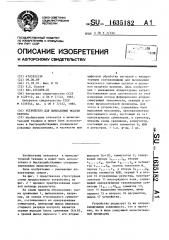

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 — процесс преобразования кодовой матрицы результата.

На схеме приняты обозначения: схема сравнения 1, выполненная, например, на основе и-разрядного сумматора, составленного из одноразрядных сумматоров, инверсный выход переноса старшего разряда которого является первым выходом блока сравнения (АЬ В), а прямой выход переноса — его вторым

2 цифровой обработке сигналов с квадратурными составляющими для вычисления модульного значения сигнала в реальном масштабе времени. Цель изобретения — уменьшение аппаратурных затрат.

Поставленная цель достигается эа счет изменения логики формирования аппроксимирующей зависимости, лежащей в основе вычислительной процедуры. Для этого в устройство, содержащее блок выделения максимума, преобразователь многорядного кода, состоящий из и+1 одноразрядных сумматоров, и сумматор, введены схема сравнения, коммутатор, состоящий иэ групп элементов И, ИПИ и регистров. 1 з.п. ф-лы, 2 ил. выходом (А(В), коммутатор 2, содержащий первую 3,...,Зд, вторую

4«,...,4„, третью 5,«,...,5, и четвертую 6 «...,,6, группы элементов И, первую 7«,...,7 «и вторую 8«,...,8 « группы элементов ИЛИ, первый 9 и второй 10 и-разрядные регистры, преобразователь 11 многорядного кода, содержащий одноразрядные трехвходовые сумматоры 12,...,12„,,, сумматор 13, блок 14 выделения максимума, шины первого 15 и второго 16 аргументов, выход 17 устройства.

Устройство реализует ту же аппроксимирующую зависимость, что и прототип, но в виде следующей вычислительной процедуры

3 1635182 4! (а Уаи„Iz(z!ее!У/ц)(((i еоРиУланаооРетеннн

/ Х/ при Х (f Yl; (У(при Х/с(Y(; оон !(! . | у (т пр» Х r Y (.

Устройство функционирует следующим образом. (;инхронизирующие сигналы подаются на управляющие входы регистров 9,10 15 и блока 14 выделения максимума (не показаны).

Но шина.", i и 16 на вход коммута-! ! т ра ° »ос у»аюг рчл(«(е коды (Х/ и

/ ((. На первь., «ход ..хеиы 1 посгупа- 20

:(»верон (з(код a. --.---1ента /Х „а на

<= (! «горой «ход — ир» (ои код Yt . В резу (s rar((л(жени» «с.соме 1 инверс.-»е о код (/ Х (пРЯл ым коДОМ /Y/ прямом выходе переноса старшего ,;зряда сумматора - втором выходе =хе— образуется сигнал единично:о уро«ня в случае, если / Х f с / Y /. .. "тот с((гнал разрешает запись аргумента j Y) в р гистр 9 через группы элементов 30

И ., 5„,ИЛИ7, 7„,аарумент» (Х вЂ” через группы элементов

И ((,...y4qy ИДИ 8(8Р, в регистр (О. Н случае 1Х/ tY/ сигнал единичного уровня образуется на инверсном выходе переноса старшего разряда сумматора — первом выходе схемы

По этому сигналу аргумент f Х / записывается в регистр 9 через И 3,,...,3, ИПИ 7,...,7, а /У) - в регистр 10 40 через И б <,...,б h, 1ШИ 8,...8 .

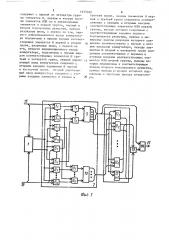

На входы преобразователя 11 поступают коды / Е1/ и (Z f/8 с выходов регистра 9 и код Е /2 с выходов регистра 10. Образованная трехстрочная 45 кодовая матрица В=1 Z

Значения кодов (l 1/ и К сравнива- 55 ются в блоке 14, в результате чего на выходе 17 образуется значение

1. Устройство для вычисления модуля вектора, содержащее блок выделения максимума, сумматор и преобразователь многорядного кода, содержащий и+1 одноразрядных трехвходовых сумматоров (где и-разрядность аргументов), первые ьхо,(ы, с первого по и-й, которых соединены с соответствующими разрядами третьего входа преобразователя, вторые входы сумматоров, со второго по (и+1)-й, соединены с соответствующими разрядами первого входа преобразователя, а третьи входы сумматоров, с первого по (n-3)-й, подключены соответ(.твенно к разрядам, с третьго по (»-1)-й, второго входа преобразователя, и-й разряд которого подключен к

wретьему входу сумма(оров, с (и-2)-z o

»о (и+()-й, выходы суммы сумматоров, кроме первого, подключены к первому выходу преобразователя, к второму выходу которого подключены выходы переноса сумматоров преобразователя, первый и второй выходы преобразователя многорядного кода соединены соот(етс.= венно с первым и вторым входами сумматора, о т л и ч а ю щ е е с я тем, что, с целью уменьшения аг(паратурних затрат, оно содержит схегу сравнения и коммутатор, причем шипа инверсного кода первого аргумента и шина прямого кода второго аргумента подключены со" ответственно к первому и второму вхо" дам схемы сравнения, шины прямого кода первого и второго аргументов соединены соответственно с первым и вторым информационными входами коммутаора, первый и второй управляющие входы которого подключены соответственно к первому и второму выходам схемы сравнения, первый выход коммутатора подключен к первому входу блока выделения максимума и первому.входу преобразователя многорядного кода, второй н третий входы которого соединены соответственно с шиной второго выхода коммутатора со сдвигом на три разряда в сторону младших разрядов и шиной третьего выхода коммутатора со сдвигом на один разряд в сторону младших разрядов, выход сумматора подключен к второму входу блока выде" ления максимума, выход которого является выходом устройства, 2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что, коммутатор

163518 содержит с первой по четвертую группы элементов И, первую и вторую группы элементов ИЛИ по и двухвходовых элементов в каждой группе, первый и

5 второй и-разрядные регистры, причем разрядные шины, с первой по п-ю, первого информационного входа коммутатора подключены к первым входам соответствующих элементов И первой и второй 1р групп, разрядные шины, с первой по п-ю, второго информационного входа коммутатора, подключены к первым Входам соответствующих элементов И третьей и четвертой групп, первый управляющий вход коммутатора соединен с вторыми входами элементов И первой и четвертой групп, второй управляющий нход коммутато1 а соединен с вторыми входами элементов И второй и 20

2 6 третьей групп, выходы элементов И rtepной и третьей групп соединены соответственно с первыми и вторыми нходами соответствующих элементов 1НИ первой группы, выходы которых соединены с соответствующими входами первого и-разрядного регистра, прямые и инверсные выходы разрядов которого соединены соответственно с первым и вторым выходами коммутатора, выходы элементов И второй и четвертой групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ второй группы, выходы которых подключены к соответствующим входам второго и-разрядного регистра, прямые выходы разрядов которого подключены к третьему выходу коммутатора.

1635182

° ° ° °

IEz) /2

° ° 4 ° lzg! p ylz) /8 е е е ° ° ° ° -)Eg! (пжж) 2 (емl

1 ф ° ° ° ° Og

Составитель В. Козлов

Техред Л.Олийнык Корректор С. Черни

Редактор А. Долинич

Эаказ 756 Тирам 393 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Уигород, ул. Гагарина, 101