Устройство для регенерации информации динамической памяти

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) 521 А1 (51) 5 С 11 С 11/40 "-)kP i мр;ЯЯ 5

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

IlPH ГКНТ СССР (21) 4455403/24 (22) 18.07 ° 88 (46) 15.03.9 1. Бюл . У 1О (72) С.Л.Улыбин, A.È.Ëÿõîâ и Н.Н.Крайнова (53) 38 1.327.66 (088.8) (56) Авторское свидетельство СССР

Ф 1 152034, кл. С 11 С 7/00, 1985. (54) УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть испольИзобретение относится к вычислительной технике и может быть использовано для регенерации динамической памяти.

Целью изобретения является повышение быстродействия устройства.

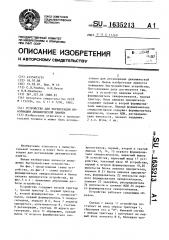

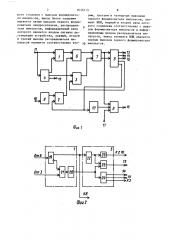

На фиг. 1 представлена схема устройства, на фиг.2 — схема первого формирователя синхросигналов и блока анализа приоритетов устройства, на фиг.3 и 4 — временные диаграммы ра"боты устройства.

Устройство содержит второй триггер

1, третий триггер 2, первый триггер

3, второй формирователь 4 синхросигналов, первый формирователь 5 синхросигналов, элемент И 6, блок 7 анализа приоритета, мультиплексор 8, счетчик

9 регенерации, счетчик 10 адреса регенерации, вход 11 обращения, первый выход 12 второго формирователя син2 зовано для регенерации динамической памяти. Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство введены второй формирователь синхросигнапов, третий триггер. Блок анализа приоритетов содержит первый и второй формирователи импульсов. Первый формирователь синхросигналов содержит формирователь импульсов, элемент ИЛИ, распределитель импульсов, элемент задержки.

2 з.п. ф-лы, 4 ил.

I хросигналов, первый, второй и третий выходы 13, 14, 15 первого формироватепя синхросигналов, адресный выход

16 устройства, адресный вход 17 устройства, тактовый вход 18 устройства, первый и второй формирователи 19,20 импульсов блока анализа приоритетов, элемент И 21 блока анализа приоритетов, формирователь 22 импульсов первого формирователя синхросигналов, элемент 23 задержки, распределитель

24 импульсов и элемент ИЛИ 25 первоFo формирователя синхросигналов.

Устройство работает следующим образом.

Сигнал с вхоца 1 1 ус тройс тва поступает на вход сброса триггера 1, сбрасывая его в "О". Нулевой сигнал с выхода триггера 1 поступает на первый вход элемента И 6, блокируя про1635213

to tip tn

Т

Т=--- Т и Й

35

55 хождение на блок 7 запроса на регенерацию с выхода триггера 2.

Кроме того, сигнал с входа 11 устройства поступает на вход формирователя 4, При поступлении сигнала на вход формирователя 4 на его трех выходах последовательно формируются единичные сигналы. Время между появлением сигналов на первом и втором выходах формирователя 4 (t<) определяется временем, необходимым для приема, контроля и преобразования, если надо, информации, приходящей в устройство памяти из процессора. Время между появлением сигналов на втором и третьем выходах формирователя 4 (t ) определяется из следующего соотношения: где t — длительность цикла регенеГ рации динамической памяти, t — длительность цикла обращеЦ ния к динамической памяти.

Сигнал с формирователя 4 поступает на выход 12 устройства и организовывает прием, контроль и при необходимости преобразование информации, приходящей в устройство памяти из процессора.

Сигнал с второго выхода формирователя 4 поступает на вход установ кк триггера 3 и устанавливает его в единичное состояние.

Сигнал с выхода триггера 3 поступает на вход обращения блока 7, организованный по принципу Раньше пришел — раньше обслужился".

Сигнал с входа формирования сигнала обращения блока 7 (фиг. 2) поступает на второй вход элемента И 21.

Элемент И 21 при отсутствии сигнала на первом входе вырабатывает на выходе сигнал "1", который поступает на формирователь 20, выход которого является вторым выходом блока 7.

Сигнал с третьего выхода формирователя 4 поступает на вход установки триггера 1 и устанавливает его в единичнсе состояние. Таким образом снимается блокировка с запроса на генерацию. Сигнал с второго выхода блока 7 поступает на вход распределителя 24 импульсов и на второй вход элемента ИЛИ 25.

Распределитель 24 импульсов имеет три выхода, на которых последовательно пс является сигнал " 1" (фиг.3).

5 !

О

С выхода элемента 25 сигнал поступает на первый выход формирователя 5. Сигналы с первого, второго и третьего выходов распределителя 24 поступают соответственно на второй, третий и четвертый выходы формирователя 5. Выходы 13, 14, 15 являются соответственно выходами выборки строки, записи и выборки столбца. Четвертый выход формирователя 5 соединен с входом сброса триггера 3. На выходе 16 устройства устанавливается адрес обращения к устройству памяти (на фиг.1, 2 не показано).

По окончании обслуживания запроса обращения на четвертом выходе формирователя 5 формируется сигнал, сбрасывающий триггер 3 в состояние "0 .

На вход 18 счетчика 9 регенерации поступают тактовые импульсы. При переполнении счетчика 9 регенерации на его выходе появляется сигнал запроса на регенерацию, который вырабатывается через время равное где Т вЂ” период регенерации динами1 ческой памяти, п — число строк динамической памяти, Т g — время обслуживания устройством обращения от процессора.

Сигнал с выхода счетчика 9 регенерации поступает на вход установки триггера 2 и устанавливает его в единичное состояние. Единичный сигнал с выхода триггера 2 поступает на второй вход элемента И 6, Если на первом входе элемента И 6 находится

"1", то на era выходе появляется сигнал, который поступает на блок 7 анализа приоритета и далее на формирователь 19 импульсов. Формирователь 19 формирует на своих прямом и инверсном выходах соответственно единичный и нулевой импульсы> длительность которых равна длительности цикла регенерации (t ) динамической памяти. Нулевой сигнал с инверсного выхода формирователя 19 импульсов поступает на первый вход элемента И 21, блокируя прохождение через этот элемент сигнала от триггера 3. Единичный сигнал с прямого выхода формирователя 19 поступает на первый выход блока 7 анализа приоритета и далее на мульти35213

10

20

5 l6 плексор 8 и формирователь 5. Мультиплексор 8 при этом пропускает на свой выход, а следовательно, и на выход 16 устройства адрес регенерируемой строки, приходящей на его второй вход с выхода счетчика 10 адреса регенерации.

Единичный сигнал с первого выхода блока 7 поступает на формирователь 22, который формирует на своем выходе сигнал, длительность которого равна длительности сигнала выборки строки (фиг, 3) . Сигнал с выхода формирователя 22 поступает на вход элемента 23 задержки и первый вход элемента ИЛИ 25. С выхода элемента ИЛИ

25 сигнал поступает на выход 13 устройства. Сигнал с выхода элемента 23 задержки пос тупа ет на пятый выход формирователя 5. Сигнал на втором, третьем и четвертом выходах формирователя 5 не формируется. По завершении цикла . регенерации на пятом выходе формирователя 5 формируется сигнал, который поступает на вход сброса триггера 2 и вход счетчика

10 адреса регенерации. При этом триггер 2 сбрасывается в "0", а на счет— чике 10 адреса регенерации устанавливается адрес следующей строки, подлежащей регенерации. Таким образом, предлагаемое устройство позволяет проводить регенерацию в моменты пауз между обращениями к памяти, за счет чего повышается эффективное быстродействие.

Ф о р м у л а и з о б р е т е н и я

1, Устройство для регенерации информации динамической памяти, с одержащее первый триггер, блок анализа приоритетов, выгод обращения которого соединен с выходом первого триггера, первый формирователь синхросигналов, вход обращения и вход регенерации которого соединены соответственно с первым и вторым выходами блока анализа приоритетов, первый, второй и третий выходы первого формирователя синхросигналов являются соответственно выходами выборки строки, разрешения записи и выборки столбца устройства, четвертый выход первого формирователя синхросигнала соединен с входом сброса первого триггера, счетчик адреса регенерации, мультиплексор, первый, второй адресные входы которого соединены соответственно с выходом счетчика адреса регенерации, первым выходом блока анализа приоритетов и с выходом счетчика адреса регенерации, адресный вход и выход мультиплексора являются адрес— ным входом и адресным выходом устройства, счетчик регенерации, вход которого является тактовым входом устройства, элемент И, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит второй формирователь синхросигналов, вход обращения которого является входом обращения устройства, первый выход первого формирователя синхросигналов является тактовым выходом устройства, вход установки и вход сброса которого соединены соответственно с третьим выходом и входом обращения второго формирователя синхросигналов, выход второго триггера соединен с первым входом элемента И, третий триггер, вход установки и вход сброса которого соединены соответственно с выходом счетчика регенерации и пятым выходом второго формирователя синхросигналов, выход третьего триг гера с оединен с вторым входом элемента И, вход счетчика адреса регенерации соединен с пятым выходом второго формирователя синхросигналов, вход обращения блока анализа приоритетов соединен с выходом элемента И.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок анализа приоритетов содержит первый формирователь импульсов, вход регенерации и прямой выход которого являются соответственно входом обращения и первым выходом блока анализа приоритетов, элемент И, первый вход которого соединен с инверсным выходом первого формирователя импульсов, второй вход элемента И является входом формирования сигнала обращения, второй формирователь импульсов, вход обращения которого соединен с выходом элемента

И, а выход является выходом блока анализа приоритетов.

3. Устройство по и. 1, о т л и ч аю щ е е с я тем, что первый формирователь синхросигналов содержит формирователь импульсов, вход регенерации которого является входом регенерации первого формирователя синхроимпульсов, блок задержки, вход кото1635213

f3

19

1б

Фиг2 рого соединен с выходом формирователя импуль.ов, выход блока эадержки является пятым выходом первого формирователя синхросигналов, распределителя импульсов, информационный вход которого является входом сигнала ре,генерации устройства, первый, второй и третий выходы распределителя импульсов являются соответственно вто- 10 рым, третьим и четвертым выходами первого формирователя импульсов, элемент ИЛИ, первый и второй вход которого соединены соответственно с выходом формирователя импульсов и информационным входом распределителя импульсов, выход элемента ИЛИ является первым выходом первого формирователя импульсов.

1635213 дхоо1 рорти ZZ дылд роре 22

Ibad оо

ИЛИ 25

8ьюод

sn.3 23

8/од р.и. Ze

2-и йод

ИЛИ 25

-u Ьд

ДИ. 24

Г" 0 Рб/юР

РИ. 24

3-и @иод

Р.k 24

Фиг. Л

ВЬеФ

Состави гель Б. Венков

Редактор М.Циткина Техред М.Дидык Корректор M,Äåì÷èê

Заказ 758

1ираж 348

Подписное

ВНИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101