Элемент памяти

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9) (И) (51)5 С 11 С 11/40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

5 "1

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4687147/24 (22) 05. 05.89 (46) 15.03.91. Бюл. )! 10 (72) А.М. Копытов, А. Г.Солод и В,О.Киреев (53) 681.327.66 (088.8) (56) ЕЕЕЕ Journal of Solid-State Circuits Ч. SC-22, )1- 5, 1987, с ° 712—

720, рис.2.

?ЕЕЕ journal of Solid-State Circuits, V. SC-22, N 5, 1987, с. 712720, рис. 4. (54) ЭЛЕМЕНТ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть применено в различных запоминающих устройствах, регистрах, стеках, ОЗУ.

Изобретение относится к вычислительной технике и может быть примено в различных запоминающих устройствах, регистрах, стеках, ОЗУ.

Целью изобретения является повышение надежности элемента памяти.

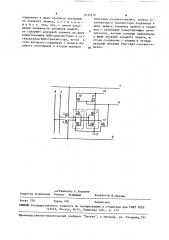

На чертеже представлена электрическая схема элемента памяти.

Элемент памяти содержит триггер на

КМДП-транзисторах, выполненный на двух инверторах 1, 2, два элемента выборки на МДП-транзисторах 3, 4, две разрядные шины 5, 6, две шины

7, 8 выборки, шину 9 нулевого потенциала, первый и второй коммутирующи транзисторы 10, 11, установочный

Целью изобретения является повышение надежности элемента памяти. Это дос тигаетс я тем, что элемент памяти содержит ключевой элемент на двух коммутирующих транзисторах 10, 11 и установочном транзисторе 12 с соответствующими связями. В режиме записи сигналом по шине 13 закрываются транзисторы 10, 11 и открывается транзистор 12, Это обеспечивает закрытое состояние обоих транзисторов первого инвертора 1, что приводит к отсутствию сквозного тока в элементе памяти. В результате запись информации в элемент памяти происходит независимо от соотношений сопротивлений каналов транзисторов элементов памяти. 1 ил. транзистор 12, шину 13 записи, шину

14 питания.

Элемент памяти является двухпор тов6!м, Двухпортовый элемент памяти работает следующим образом.

В режиме чтения на шину 13 подается потенциал 0". При этом р-канальные коммутирующие транзисторы 10, 11 открыты и подключают первый и второй инверторы 1, 2 к шине 14 питания. По одному ацресу возбуждается шина 7 выборки и на разрядную шину 5 первого порта считывается информация, записанная в элементе памяти. По другому адресу возбуждается шина 8 выборки

16352 1 4 второго погта и через транзистор 4 разрядная инна 6 второго порта подключается к выходу первого инвертора

1, на ней устанавливается потенциал, записанный в элементе.

Таким образом происходит чтение информации из элемента памяти по одному адресу на первый порт и чтение из другого элемента памяти по другому адресу на второй порт. При возбуждении шин 7 8 первого и второго портов по одному общему адресу разрядные шины 5,6 первого и второго портов подключаются к выходу первого инвертора 1 через транзисторы 3, 4 и информация, записанная в элементе памяти, счигывается на разрядные шины 5, 6 первого и второго портов.

В режиме записи на шину 13 подается положительный импульс записи.

При этом р-канальные коммутирующие транзисторы 10, 11 закрываются и выходы первого и второго инверторов

1, 2 отключаются от шины питания 14.

Транзистор 12 открывается, и на выходе второго инвертора 2 устанавливается уровень "0" ° При этом выход первого инвертора 1 отключается также от шины 9, т.е. находится в третьем состоянии °

При возбуждении шины 7 выборки первого порта выход первого инвертора 1 подключается через транзистор 3 выборки первого порта к разрядной шине 5 первого порта и на выходе первого инвертора 1 записывается потенциал разрядной шины 5, при этом не протекает сквозной ток при записи, так как выход первого инвертора 1 находится в третьем состоянии. При этом возможно, возбуждая, шину 8 выборки второго порта по тому же адресу, на разрядную шину 6 второго порта считывать информацию с разрядной шины 5 первого порта.

Рассмотрим подробнее запись уровня "1" и "0" в элемент памяти.

Предположим, на выход первого инвертора 1 записывают уровень "1", Выход второго инвертора 2 подключен к шине 9 через открытый транзистор

12. Выход первого инвертора 1 находится в третьем состоянии, и через транзистор 3 выборки выход первого инвертора 1 подключается к разрядной шине 5 первого порта, находящейся в состоянии "1", происходит заряд параэитной емкости выхода первого

1О

45 инвертора 1 до "1", По окончании импульса записи коммутирующие транзисторы 10 и 11 открываются и подключают входы питания триггера к шине 14 питания, закрывается транзистор 12, выход первого инвертора подключается к шине 14 питания и через открытый р-канальный транзистор первого инвертора 1 на его выходе устанавливается напряжение, равное напряжению питания.

Предположим, на выход первого инвертора 1 записывается уровень "0".

Выход второго инвертора 2 подключен к шине 9 через открытый транзистор

12, выход первого инвертора 1 находится в третьем состоянии, происходит разряд паразитной емкости выхода первого инвертора 1 до "0". По окончании импульса записи коммутирующие транзисторы 10 и 11 открываются и подключают нагрузочные транзисторы первого и второго инверторов 1, 2 к шине 14 питания, закрывается транзистор 12, выход первого и второго инверторов 1, 2 подключается к шине

14 питания и через открытые р-канальные транзисторы первого и второго инверторов 1, 2 происходит заряд паразитной емкости первого и второго инверторов 1, 2, Длительность строба записи меньше длительности импульса выборки шин 7, 8, следовательно, к выходу первого инвертора 1 подключена емкость разрядной шины 5 или 6, на два порядка превышающая паразитную емкость выхода второго инвертора 2.

Выход второго инвертора 2 за 1-2 нс заряжается до уровня напряжения питания, на выходе первого инвертора 1 устанавливается напряжение, равное уровню "0", замыкается цепь положительной обратной связи, обеспечивающая хранение информации в элементе памяти.

Формула изобретения

Элемент памяти, содержащий триггер на ЕИДП-транзисторах, два элемента выборки на МДП-транзисторах, истоки которых соединены с первым выходом триггера, затворы подключены к первой и второй шинам выборки элемента памяти соответственно, а стоки — к первой и второй разрядным шинам элемента памяти соответственно, вход нулевого потенциала триггера составитель С.Королев

Редактор М.Циткина Техред М.Дидык Корректор N.Äåì÷èê

Заказ 758 Тираж 348 Подпис ное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101 подключен к шине нулевого потенциала элемента памяти, о т л и ч а ю— шийся тем, что, с целью повышения надежности элемента памяти, он содержит ключевой элемент на двух коммутирующих МДП-транзисторах и установочном МДП-транзисторе, исток и сток которого соединены с входом нулевого потенциала и вторым выходом

635214 6 триггера соответственно, затвор установочного транзистора подключен к шине записи элемента памяти и соеди5 нен с затворами коммутирующих транзисторов, истоки которых подключены к шине питания элемента памяти, а стоки соединены с первым и вторым входами питания триггера соответст1p венно °