Накапливающий сумматор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)5 G 06 F 7/50, 7/60

ГОСУДАРСТВЕННЦЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ -1

ПРИ ГКНТ СССР г,%, 1 У

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 46374!5/24 (22) 13.01.89 (46) 07о04 ° 91 ° Bran. М 13 (72) В.А.Миндалев и С.Н.Субботин (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 1043638, кл. G 06 F 7/50, 1982.

Угрюмов Е.П. Проектирование элементов и узлов ЭВМ вЂ” М.: Высшая школа .1987, с.195 196, рис. 11, 14. (54) НАКАПЛИВАНщИй СУММАТОР (57) .Изобретение относится к вычислительной технике и может быть исполь„„90„, 1640685 А 1

2 зовано в устройствах передачи информации. Целью изобретения является повышение точности накапливающего сумматора при использовании его в качестве устройства усреднения входного числа для схем фазовой подстройки. Накапливающий сумматор содержит регистр

1, комбинационный сумматор 2, два . мажоритарных элемента 3,4, элемент Н7. 5, элемент Иб, триггер 7, элемент ИСКЛОЧИО11ЕЕ.И1П1 8, шину 9 синхронизации и шину

10 входного числа, соединенные между собой функционально. I ил.

1640685 4

Изобретение относится к вычислительной технике и может быть исполь- зовано в устройствах передачи информации.

Цель изобретения — повышение точности накапливающего сумматора при использовании его в качестве устройства усреднения входного числа для схем фазовой подстройки. !

О

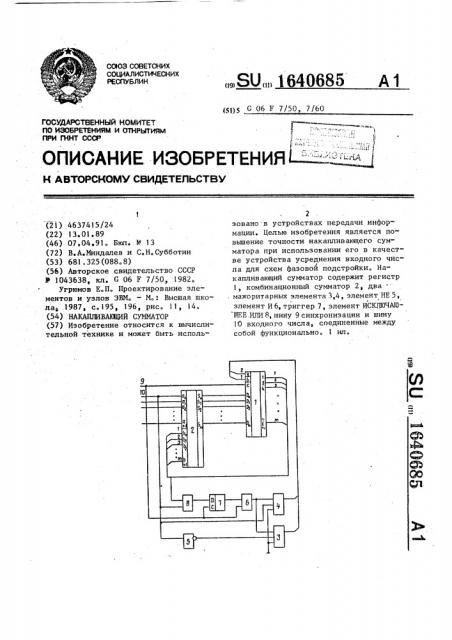

На чертеже представлена функциональная схема накапливающего сумматора.

Накапливающий сумматор содержит регистр 1, комбинационный сумматор 2, !5 первый 3 и второй 4 мажоритарные элементы, элементы НЕ 5 и И 6, триггер 7, элемент ИСКЛЮЧАКВ!ЕЕ ИЛИ 8, шины синхронизации 9 и входного числа

10, соединенные между собой функционально.

Накапливающий сумматор в качестве устройства усреднения входного числа работает следующим образом.

Код первого слагаемого хранится в регистре 1, а код второго слагаемого поступает по шине 10.

В комбинационном сумматоре 2 производится сложение двух чисел, из которых первое поступает по шине 10, а второе — с выходов регистра 1. Образованная сумма по импульсу синхронизации, поступающему по шине 9 синхронизации, записывается в регистр 1.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8 сравнивает знаки входного и выходного чисел. Если значения знаковых разрядов на выходе накапливающего сумматора и входного числа одинаковые (происходит накопление положительных или отрицатель.40 ных чисел), то с выхода элемента ИСКЛЮЧАКЩЕЕ ИЛИ 8 уровень логического нуля поступает на информационный вход триггера 7 и записывается в него по импульсу синхронизации. 45

Данный уровень логического нуля умножается элементом И 6 на длитель° ность импульса синхронизации и поступает на первые входы мажоритарных элементов 3 и 4, на вторые .входы ко- 50 торых поступает уровень логического нуля, и, независимо от уровня на третьих входах, на выходах мажоритарных элементов 3 и 4 присутствует уровень лбгического нуля, который поступает на установочные входы регистра 1, не влияя на них. Накапливающий сумматор в этом случае суммирует входные числа и результат накапливает в регистре 1, замещая предыдущее содержание.

Если знак входного числа изменился и значения знаковых разрядов на выходе накапливающего сумматора и входного числа разные ("0" и "1" или

"1" и "0" соответственно), это означает, что накопление необходимо прекратить, так как тактовая частота на приеме схемы фазовой подстройки сравнялась с тактовой частотой на передаче и накапливающий сумматор в этом случае необходимо обнулить или установить в единичное состояние в зависимости от знака входного числа.

1!ри разных знаках входных и выходных чисел накапливающего сумматора на выходе элемента ИСКЛЮЧАК!!!ЕЕ ИЛИ 8 формируется уровень логической единицы, поступающий на информационный вход триггера 7. По импульсу синхронизации уровень логической единицы записывается в триггер,7 и с его выхода поступает на первый вход элемента

И 6, на выходе которого формируется импульс длительностью, равной импуль су частоты синхронизации. Данный импульс поступает на первые входы мажоритарных элементов 3 и 4. Если на входе накапливающего сумматора положительное число, то на третий вход мажоритарного элемента 3 поступает уровень логической единицы, а на третий вход мажоритарного элемента 4 — уровень логического нуля. На выходе мажоритарного элемента 3 формируется уровень логической единицы, поступающий на вход установки регистра 1 в ноль, а на выходе мажоритарного элемента 4— уровень логического нуля.

На разрядных выходах регистра 1 формируются уровни логического нуля.

Если на входе накапливающего сумма" тора отрицательное число, то на третий вход мажоритарного элемента 3 поступает уровень логического нуля, а на третий вход мажоритарного элемента 4 — уровень логической единицы.

На выходе мажоритарного элемента 3 формнруется уровень логического нуля, а на выходе мажоритарного элемента 4— уровень логической единицы, поступающий на вход установки регистра 1 в единицу. На разрядных выходах регистра 1 формируются уровни логической единицы. Регистр 1. обнуляется или устанавливается в единичное состояние

1640685 шийся тем, что, с целью повышения точности при использовании накапливающего сумматора в качестве устройства усреднения входного числа для схем фазовой подстройки, в него введены первый и второй мажоритарные элементы, элемент НЕ, элемент И, триггер и элемент ИСКЛЮЧАКЩЕЕ ИЛИ, причем выход знакового разряда регистра соединен с первым входом элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен со знаковым разрядом шины входного числа и с входом элемента НЕ, выход элемента ИСКЛЮЧАКЩЕЕ ИЛИ соединен с,информационным входом триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с синхровходами

20 триггера и регистра, выход элемента

И соединен с первыми входами первого и второго мажоритарных элементов, вторые входы которых соединены с шиной нулевого потенциала, выход элемента HE соединен с третьим входом первого мажоритарного элемента, выход которого соединен с входом установки в нулевое состояние регистра, вход элемента НЕ соединен с третьим входом второго мажоритарного элемента, выход которого соединен с входом установки в единичное состояние регистра. и вновь начинает накапливать входные числа.

Установка регистра 1 накапливающего сумматора в ноль или единичное состояние необходима для коррекции знаков входного и выходного чисел.

Эффективность использования предлагаемого накапливающего сумматора в схеме фазовой подстройки заключается в том, что позволяет повысить точность фазовой подстройки тактовой частоты. Схема определяет равенство тактовых частот на передаче и приеме, 15 что позволяет повысить помехоустойчивость системы.

Формула изобретения

Накапливающий сумматор, содержащий комбинационный сумматор и регистр, разрядные выходы которого соединены соответственно с входами первой группы комбинационного сумматора, входы 25 второй группы которого соединены с шиной входного числа накапливающего сумматора, разрядные выходы комбинационного сумматора соединены соответственно с информационными входами ре- 30 гистра, вход синхронизации которого соединен с шиной синхронизации накапливающего сумматора, о т л и ч а ю—

Составитель В. Гусев

Редактор В,Бугренова Техред С,Мигунова Корректор

Заказ 1017 Тираж 402 Подписное

ВНИИ11И Государственного комитета по изобретениям и открытиям прн ГКНТ СССР

11I3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101