Устройство для контроля многомодульных логических блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля многомодульных логических блоков дискретных устройств. Целью из обретения является увеличение достоверности и глубины контроля. С этой целью в устройство , содержащее блок переключателей, первый и второй блоки сигнатурного анализа, дешифратор, блок индикации и распределитель импульсов, введены счетчик адреса, блок памяти тестов и группа переключателей обратной связи. 3 ил.

09) 011

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5}) G 06 F 11 00

ОПИСАНИЕ ИЭОБРЕТЕНИг»

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОсудАРстВенный нОмитет

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР. (21 ) 4390661/24 (22) 09.03.88 (46) 07.04.91 Бюп. Н 13 (72) В.И.Жуков (53) 681 3 (088.8) (56) Авторское свидетельство СССР

Р 890396, кл. G 06 F 11/00, 1981.

Авторское свидетельство СССР

У 1317440, кл, G 06 F 11/00, 1987. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МНОГОМОДУЛЬНЫХ ЛОГИЧЕСКИХ БЛОКОВ (57) Изобретение относится к автомаИзобретение относится к автоматике и вычислительной технике и может быть использовано для контроля многомодульных логических блоков дискрет,;ных устройств.

Цель изобретения - увеличение достоверности и глубины контроля.

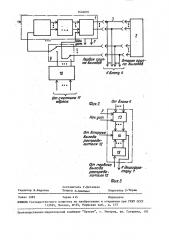

На фиг. приведена структурная схема устройства; на фиг. 2 детализированы связи модулей контролируемого логического блока и проверяемого логического модуля с остапьными блоками устройства; на фиг. 3 представлен пример выполнения блока сигнатурного анализа.

На фиг. 1 изображены контролируемый логический блок 1 и проверяежй логический модуль 2 (блок), которые соединены посредством блока 3 переключателей (кросс-платы) и блока 4 коммутаторов (образованного проводным» перемычками) с информационными входами первого и второго блоков 52 тике и вычислительной технике и может быть использовано для контроля многомодульных логических блоков дискретных устройств. Целью изобретения является увеличение достоверности и глубины контроля, С этой целью в устройство, содержащее блок переключателей, первый и второй блоки сигнатурного анапиза, дешифратор, блок индикации и распределитель импульсов, введены счетчик адреса, блок памяти тестов и группа переключателей обратной связи.

3 ил.

6 сигнатурного анализа. Кроме того, в состав устройства входят дешифратор

7; блок 8 индикации, группа переклю- Я чателей 9 обратной связи, блок 10 па мяти тестов, счетчик 11 адреса и распределитель 12 импульсов.

ОЪ

На фиг, 2 более детапьно показана структура связей модулей контролируемого логического блока 1, проверя» © емого модуля 2 и переключателей бло- Ж ка 3 и группы 9.

Блок 5 (или 6) сигнатурного анализа (фиг. 3) содержит формирователь

13 сигнатуры, схему 14 сравнения и память 15.

Устройство работает следующим об» разом.

В контролируемом логическом блоке с помощью органов управления устанавливают режим "Самоконтроль". Необходииае тестовые воздействия могут подаваться также от внешних источников, 1640691 например, установки тестового контроля УТК-2, С помощью блока 4 входные сигналы раздельно подключаются к информационным входам блока 5 сигнатур5 ного анализа, а выходные сигналы и выходные сигналы обратных связей проверяемого модуля 2 раздельно подключают к информационным входам блока 6 сигнатурного анализ а, Переключатели

9 отключают обратные связи контролируемого блока 1> и к образовавшимся в результате этого дополнительным входам подключаются выходы блока 10 памяти, Переключатели 9 (на фиг. 2) устанавливаются оператором в нижнее положение, В блок 10 памяти предварительно записывают даннные о значениях сигналов в цепях обратных связей, формируемых в режиме "Самоконтроль", Блок 10 памяти содержит смен ные кубы памяти, Для каждого проверяемого блока имеется свой куб памяти.

Данные о сигнапах в цепях обратных связей получают предварительно в про- 25 цессе моделирования, Таким образом, контролируемый блок 1 с помощью переключателей 9 преобразуется в дискретное устройство, не содержащее обратных связей. На алгоритм работы контролируемого блока 1 и проверяемого модуля 2 данное преобразование не влияет. Пример выполнения блоков 5 и 6 сигнатурного анализа приведен на фиг. 3. Каждый из блоков 5 и 6 сигна- 35 турного анализа содержит формирователь 13 сигнатуры, схему .14 сравнения и память 15, Формирователь 13 сигнатуры является многоканальным блоком формирования остатков. 40

Оператор с помощью распределителя

12 устанавливает продолжительность контроля проверяемого модуля (суббло» ка) 2. Затем на счетчик 11 адреса и распределитель 12 поступают сигна- 45 лы начальной установки и тактовой частоты, поступающие также на блок 5 сигнатурного анализа и блок 6 сигна турного анализа, в которых обрабатываются входные и выходные сигналы об- 50 ратных связей проверяемого модуля (субблока) 2. Счетчик 11 адреса подсчитывает поступающие тактовых импульсов. По выходным сигналам счетчика 11, адреса информация из блока 10 памяти (сменного куба памяти) считывается через переключатели 9 на входы контролируемого блока 1 образовавшиеся в результате отключения обратных свя- зей. Таким образом обеспечивается функционирование контроЛируемого бло» ка 1 с отключенными обратными связями по тому же алгоритму работы, что и с подключенными обратными связями, По истечении времени проверки модуля (субблока) 2 от распределителя 12 на блок 5 сигнатурного анализа и блок 6 сигнатурного анализа поступает сигнал

"Чтение" > затем сигнал "Опрос". Сигналы с блоков 5 и 6 сигнатурного анализа поступают на входы дешифратора 7, который при наличии правильных входной и выходной сигнатур формирует сигна "Норма" — признак годности, а при правильной входной и неправильной выходной сигнатурах - сигнал "Дефект" указывает на неисправность конкретного проверяемого модуля (субблока) 2.

Это увеличивает глубину поиска дефекта и вследствие однозначности результата проверки - производительность.

При неправильной входной сигнатуре формируется сигнал "Дефект по входу" признака ошибки по входу, например, иэ-за неисправности одного из предыдущих модулей, выходные сигналы которого являются входными для проверяемого блока.

Формула изобретения

Устройство для контроля многомодульных логических блоков, содержащее блок переключателей, первый и второй блоки сигнатурного анализа, дешифратор, блок индикации и распределитель импульсов, первый и второй выходы которого соединены соответственно с входами чтения и входами оп» роса первого и второго блоков сигнатурного анализа, выходы первого и второго блоков сигнатурного анализа подключены соответственно к первому и второму информационным входам дешифратора, выходы признака годности, признака ошибки и признака ошибки по входу которого соединены с одноименными входами блока индикации, входы начальной установки первого и второго блоков сигнатурного анализа и вход запуска распределителя импульсов образуют вход начальной установки устройства, синхровходы первого и второго блоков сигнатурного анализа и распределителя импульсов образуют синхровход устройства, а неподвиж5

16406 ные контак гы переключателей первой и второй групп блока переключателей подключены к информационным входам соответственно первого и второго

5 блоков сигнатурного анализа, о т л ич а ю щ е е с я тем, что, с целью увеличения достоверности и глубины контроля, оно содержит счетчик адреса, блок памяти тестов и группу переключателей обр атной связи, подвижные контакты которых являются выходами устройства для подключения к входам одноименных модулей контролируемого логического блока, первые подвижные контакты переключателей первой группы блока переключателей соединены с неподвижными контактами переключателей той же группы и являются входами устройства для подключе- 20 ния к выходам модулей контролируемого логического блока, вторые подвижные контакты переключателей первой

Группы блока переключателей подключены к неподвижным контактам переклю- 25

91 6 чателей той же группы и являются выходами усгройства для подключения к входам проверяемого логического модуля, первые подвижные контакты переключателей второй группы блока переключателей соединены с неподвижными контактами переключателей той же группы и являются входами устройства для подключения к выходам проверяемого логического модуля, вторые подвижные контакты переключателей второй группы блока переключателей подкЛючены к неподвижным контактам переюночателей той же группы и первым неподвижным контактам одноименных переключателей обр атной связи группы, вторые неподвижные контакты которых соединены с одноименными выходами блэка памяти тестов, а вход начальной установки, синхровход и выход счетчика адреса подключены соответственно к входу начальной установки и синхровходу устройства и адресному входу блока памяти тестов.

1640691

0m &окаФ

Уои.yc

0m Юмор

ЮыхаУа раслра7е

ЛЕ//7УРЛЯ

0m nyet

Аао ржлределилыля Q

ЦР РРакру 7

Составитель Г.Витапиев р д д.O>«<»„ Корректор C-Черни

Редактор Б.Федотов

Заказ 12б5 Тираж 415 Подпи сное

ВЯИИДИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва,.Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101