Устройство для выполнения быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

Устройство предназначено для выполнения быстрого преобразования Фурье (БПФ), которое используется при цифровой обработке сигналов, и может применяться в качестве сопро- i цессора универсальной микроЭВМ для повышения ее производительности при вычислении спектра сигналов и их фильтрации в частотной области Цель изобретения - сокращение объема аппаратурных затрате Устройство содержит арифметический блок, блок сдвиговых регистров, содержащий восемь сдвиговых регистров, блок синхронизации и коммутатора Устройство выполняет базовую операцию БПФ над данными, Хранящимися в памяти микроЭВМ в виде таблицы элементов выборки и таблицы поворотных множителей о Выборка данных из таблиц, передача их в устройство и прием результатов вычислений выполняются под управлением микроэвм, 1 з о п. ф-лы, 2 ил о (О (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (g!)g G 06 F 15/332. ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ"" :;- .- : ;=.

Н A BTOPCHOMV СВИДЕТЕЛЬСТВУ

1 (21) 4400835/24; 4400703/24 (22) 30. 03. 88 (46) 07.04. 91. Бюл. ¹ 13 (71) Особое конструкторско-технологи;— ческое бюро "Парсек" при Тольяттинсском политехническом институте (72) С.В.Редькин и Н.А.Игнатьева (53) 681.3(088.8) (56) Микропроцессорные средства и системы, !986, ¹ 2, с. 23. рис.3.

Авторское свидетельство СССР

¹- 1312611, кл. G 06 F 15/332, 1985, (54) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ (57) Устройство предназначено для выполнения быстрого преобразования

Фурье (БПФ), которое используется при цифровой обработке сигналов, и

Изобретение относится к вычислительной технике и предназначено для выполнения быстрого преобразования

Фурье (БПФ), которое используется при цифровой обработке сигналов.

Цель изобретения — сокращение аппаратурных затрат.

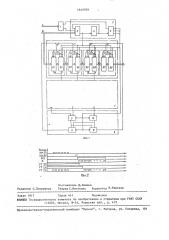

На фиг.1 представлена схема устройства; на фиг.2 — временная диаграмма работы устройства.

Устройство содержит дешифратор 1 адреса; блок 2 синхронизации, содержащий счетчик 3 тактов, управляемый генератор 4 и распределитель 5 синхросигналов, блок 6 сдвиговых регистров, содержащюЪ восемь сдвиговых регистров 6.1-6.8, коммутатор 7, арифмети-, „„SU„„1640709 А 1

2 может применяться в качестве сопроцессора универсальной микроЭВМ для повышения ее производительности при вычислении спектра сигналов и их фильтрации в частотной области. Цель изобретения — сокращение объема аппаратурных затрат. Устройство содержит арифметический блок, блок сдвиговых регистров, содержащий восемь .сдвиговых регистров, блок синхронизации и коммутатор. Устройство выполняет базовую операцию Б11Ф над данными, хранящимися в памяти микроЭВМ в виде таблицы элементов выборки и таблицы поворотных множителей. Выборка данных из таблиц, передача их в устройство и прием результатов вычислений выполняются под управлением микроЭВМ, 1 з.п. ф-лы, 2 ил, ческий блок 8, содержащий конвейерный умножитель 9 комплексных последовательных знакоразрядных двоичных чисел 7, блок 10 задержки, конвейер- 4 ный вычитатель 11 комплексных после- СР довательных знакоразрядных двоичных Ж чисел и конвейерный сумматор 12 комплексных последовательных знакоразряц . ных двоичных чисел.

Устройство работает следующим образом.

Перед выполнением БПФ сигнал с вы- В хода счетчика 3 запрещает работу генератора 4 и устанавливает блок 6 в режим ввода-вывода данных (фиг.1, 2).

При наличии адреса А! на адресном входе устройства на первом выходе де

1640709. шифратора 1 вырабатывается импульс, который через первый вход распределителя 5 проходит на его соответствующий выход и поступает на тактовый вход блока 6. При этом в регистры

6.1, 6.2 вводится слово данных с информационного входа устройства, а.в каждый следующий регистр вводится слово данных с выхода предыдущего ре- 10 гистра.

После занесения операндов в регистры 6.1-6.6 при наличии на адресном входе устройства адреса А2 на втором выходе дешифратора 1 вырабатывается импульс, по которому с входа Д1 устройства в счетчик 3 заносится код числа тактов. Сигнал с выхода счетчика

3 разрешает работу генератора 4 и переводит блок 6 в режим обмена данными с арифметическим блоком 8.

В момент выдачи генератором 4 первого тактового импульса сигнад с со" ответствующего выхода распределителя

5 удерживает коммутатор 7 в закрытом состоянии. При этом в арифметическом блоке 8 фиксируется наличие уровней логической единицы на первом и втором входе каждого операнда, т.е. состояние "маркера, по которому опреде-30 ляется начало очередного цикла работы.

Во втором такте значение уровня сигнала на соответствующем выходе распределителя 5 изменяется, коммутатор

7 открывается и подключает BblxopbI ре- 35 гистров 6.1, 6.3, 6.5 к соответствующим выходам. В арифметический блок 8 при этом заносятся старшие разряды операндов.

В третьем и последующих тактах по 40 сигналу с соответствующего выхода распределителя 5, коммутатор 7 подключает выходы регистров 6.2, 6.4, 6,6 к соответствующим выходам, а импульс с выхода генератора 4 через вто- 5 рой вход распределителя 5 поступает на тактовый вход блока 6, вызывая сдвиг информации в регистрах 6.1-6.8.

Очередные разряды операндов поступают при этом на соответствующие входы арифметического блока 8 и далее на входы умножителя 9 и блока 10 задержки..Разряды соответствующего операнда с выхода блока 10 задержки поступают на первые входы вычислителя 11 55 и сумматора 12, на вторые входы кдторых поступают одноименные разряды произведения операндов с выхода умножителя 9.

Задержанные на k тактов одноименные разряды результатов с выходов вычитателя 11 и сумматора 12 поступают соответственно на первый и второй информационные входы блока б и фиксируются в регистрах 6.1-6.8. После выдачи k+n тактовых импульсов с выхода генератора 4 на тактовый вход счетчика 3 сигнал с выхода последнего запрещает работу генератора 4 и переключает блок б в режим ввода-вывода данных

Вывод и-разрядных кодов результатов из регистров 6.1-6.8 выполняется путем последовательного считывания данных с выхода устройства по адресу Al .

Операции вывода результатов и занесения новых значений операндов могут быть совмещены во времени при наличии физических разделенных каналов ввода и вывода данных.

Формула изобретения

1. Устройство для выполнения быстрого преобразования Фурье, содержащее блок сдвиговых регистров, содержащий восемь сдвиговых регистров, коммутатор, арифметический блок и блок синхронизации, причем первый и второй выходы результата арифметического блока соединены соответственно с первым и вторым информационными входами последовательной записи блока сдвиговых регистров, с первого по третий выходы которого соединены соответственно с первого по третий информационными входами коммутатора, первый и второй выходы которого соединены соответственно с входами первого и второго операндов арифметического блока, первый управляющий вход коммутатора соединен с первым выходом блока синхронизации, о т л и ч а ю щ е е с я тем, что, с целью сокращения анпаратурных затрат, третий выход коммутатора соединен с входом третьего операнда арифметического блока, тактовый вход которого соединен с тактовым входом блока сдвиговых регистров и вторым выходом блока синхронизации, третий и четвертый выходы которого соединены соответственно с вторым управляющим входом коммутатора и входом управления параллельной записью блока сдвиговых регистров, информационньпЪ вход параллельной записи которо1640709 го соединен с входом задания режима

1 работы блока синхронизации и подключен к входу загрузки данных устройства четвертый выход блока сдвигоЭ

5 вых регистров является выходом устройства, вход запуска и вход задания режима загрузки устройства подключены соответственно к первому и второму входам задания режима блока синхронизации, причем в блоке сдвиговых регистров информационный вход параллельной записи первого сдвигового регистра является информационным входом параллельной записи блока, выход параллельной информации i-го сдви" гового регистра (i=1 7} соединен с информационным входом параллельной записи (i+1)-го сдвигового регистра, выход параллельной информации восьмо- 20 го сдвигового регистра является четвертым выходом блока, тактовые входы всех сдвиговых регистров соединены между собой и подключены к тактовому входу блока, вход управления парал- 25 лельной записью которого подключен к одноименным входам всех сдвиговых регистров, информационные входы последовательной записи с первого по четвертый сдвиговых регистров образуют 30 первый информационный вход последовательной записи блока, второй информационный. вход которого образуют информационные входы последовательной записи с пятого по восьмой сдвиговых регистров, выходы последовательной информации первого и второго сдвиговых регистров образуют третий выход блока, первый и второй выходы которого образуют выходы последовательной информации третьего, четвертого и пятого, шестого сдвиговых регистров.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что арифметический блок содержит умножитель, сумматор, вычитатель и узел задержки, выход которого соединен с первыми входа" ми сумматора и вычитателя, вторые входы которых соединены с выходом умножителя, тактовый вход которого соеди-. нен с тактовыми входами сумматора и вычитателя и является тактовым входом блока, выходы сумматора и вычитателя являются соответственно первым и вторым выходами результата блока, входы коэффипнентов, первого и второго операндов являются соответственно первым входом умножителя, вторым входом умножителя и входом узла задержки, 1640709 быха,1ц эсвМ псаМ сп б ,гт N

FT (>) гтрк

Со ст авит ель Ю. Л андо в

Редактор С.Патрушева Техред С.Мигунова Корректор Н РеасК

Заказ 1017 Тираж 414 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

)13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул, Гагарина, 101