Ячейка памяти на основе комплементарных моп-транзисторов

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой технике и может быть использовано в микросхемах программируемой логики , динамически реконфигурируемых БИС, микропроцессорах и прочих устройствах обработки дискретной информации с использованием оперативного запоминающего устройства (ОЗУ) в качестве управляющей памяти. Цель изобретения - повышение быстродействия ячейки памяти. Поставленная цель достигается за счет введения третьего ключевого элемента 10 на р-канальном МОП. При этом ячейка памяти устойчиво функционирует пои записи как Лог. О, так и Лог, 1, не требуя понижения напряжения питания ячейки до какого-то промежуточного значения , т.е. исключаются по сравнению с прототипом временные потери на переход напряжения питания от одного значения к другому, и наоборот. Перезаряд точки соединения стоковых областей элементов 3, 4 схемы лог. О к Лог, 1 происходит быстрее вследствие отрыва элемента 3 от потенциала шины 8 ячейки, что, в свою очередь, приводит к уменьшению размеров элемента 5 до размеров элементов 3, 4 и, как следствие, ведет к уменьшению площади, занимаемой ячейкой. 1 ил. §

СО03 СОВЕТСНИХ

ССЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„Я0„„16407 (5Ф)5 G 11 С 11/40

ГОСУДАРСТ8ЕННЫЙ НОМИТЕГ

ll0 ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ - — " - - - — -1

Изобретение относится к цифровой технике и может быть использовано в микросхемах программируемой логики, динамически реконфигурируемых БИС, микропроцессорах и прочих устройствах обработки дискретной информации с использованием оперативного запоминающего устройства (ОЗУ) в качестве управляющей памяти.

Цель, изобретения — повышение быстродействия ячейки памяти.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4670888/24 (22), 30.03.89 (46) 07.04.91. Бюл. 11 13 (72) С.Н.Венжик, А.Г.Гарицын и M.Ï.Ñàõàðîâ (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР

N - 1444888, кл. G 11 С 11/40, 1987.

Алексеенко А.Г. и Шагурин И,И.

Микросхемотехника. M.: Радио и связь, 1982, с. 225, рис. 7, 7а. (54) ЯЧЕЙКА ПАМЯТИ НА ОСНОВЕ КОМППЕМЕНТАРНЫХ ИОПТРАНЗИСТОРОВ (57) Изобретение относится к цифровой технике и может быть использовано в микросхемах програмьыруемой логики, динамически реконфигурируемых

БИС, микропроцессорах и прочих устрой- ствах обработки дискретной информации с использованием оперативного запоминающего устройства (ОЗУ) в ка-. честве управляющей памяти. Цель изобретения — повышение быстродействия

2 ячейки памяти. Поставленная цель достигается за счет введения третьего ключевого элемента 10 на р-канальном ИОП. При этом ячейка памяти устойчиво функционирует пои записи как

Лог, "О", так и Лог, "1", не требуя понижения напряжения питания ячейки до какого-то промежуточного значения, т,е. исключаются по сравнению с прототипом временные потери на переход напряжения питания от одного значения к другому, и наоборот, Перезаряд точки соединения стоковых областей элементов 3, 4 схемы лог. "0" к Лог, "1" происходит быстрее вследствие "отрыва" элемента 3 от потенциала шины 8 ячейки, что, в свою очередь, приводит к уменьшению размеров элемента 5 до размеров элементов

3, 4 и, как следствие, ведет к уменьшению площади, занимаемой ячейкой.

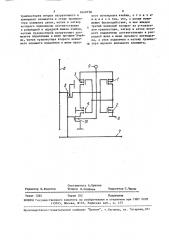

На чертеже приведена схема ячейки памяти.

Ячейка содержит вторые нагрузочный и ключевой элементы 1, 2, первые нагрузочный и ключевой элементы 3, 4, элемент 5 связи, разрядную н адрес- 1 . ную шины 6, 7, шину 8 нулевого потенциала и шину 9 питания, третий ключевой элемент 10 ячейки. Ячейка памяти выполнена на основе комплементарных.. транзисторов. B качестве элементов

1640738

3, 10 используются р-канапьные МОПтранзисторы, а в качестве элементов

2, 4, 5 - n-канальные МОП-транзисторы. Ячейка работает следующим обра5 эом, На шину 6 ячейки подают напряжение Лог. "0", на шину 7 ячейкиЛог, "1", По приходе лог. "1" на затворы элементов 5 и 10 элемент 5 открывается, а элемент 1О закрывается. Т.к. элемент 5 без искажения передает Лог. "0", напряжение на затво» рах транзисторов элементов 1 и 2 шунтируется Лог О, приходящим с шины

6 ячейки. Появление Лог. "О" на затворах транзисторов элементов 1 и 2 приводит к включению элемента 1 и выключению элемента 2, Включение элемента 1 вызывает по явление Лог. "1" в точке соединения стоковых областей элементов 1 и 2 и, следовательно, напряжение высокого уровня на затворах транзисторов 3 и

4. Появление Лог. "1" на затворах транзисторов 3 и 4 приводит к выключению р-канального МОП-транзистора 3 и включению п-канального МОП-транзистора 4. Вследствие этого заряд, образующийся в точке соединения стоковой области транзистора 10 и истоковой области транзистора 4, рассасывается через транзисторы 4 и 5 на разрядную шину 6, а напряжение в точке уменынается. По окончании действия сигнала Лог. "1" на шине 7 ячейки, элемент 5 закрывается, а элемент 10 открывается, подтверждая напряжение низкого уровня на истоке элемента 4.

При записи Лог, "1" на шину 6 nol1 П дают напряжение Лог- 1, на шину 7 адреса - Лог. "О", По приходе

Лог. "1" на затворы элементов 5 и 10 элемент 10 закрывается, а элемент 5 открывается, Выкпючение элемента 10 приводит к отрыву истоковой области элемента 4 от общей шины 7 и таким образом исключает возможность шунти рования высокого напряжения, приходящего с шины 6 через элемент 5 на затворы элементов 1 и 2. Несмотря на то, что элемент 5 передает с искажением напряжения Лог. "1" (Е,-U<>), это, в конечном итоге, не влияет иа переключение элементов 1 и 2, Появле55 ние напряжения высокого уровня на затворе элемента 1 (большего Up< ) приводит,к его включению и появлению

«J напряжения Лог. "0" на э ат вор ах элементов 3 и 4, элемент 1 при этом закрывается. Появление Лог. "0" на затворах элементов 3 и 4 йриводит к включению элемента 3 и выключению (по цепи затвора) выключенного по истоковой цепи элемента 4. Включение элемента 3 приводит к подтверждению записываемого в ячейку напряжения

Лог. "1". По окончании сигнала раз решения (напряжение на шине 7 ячейки меняется с Лог. "1" на Лог. "О") элемент 5 закрывается, а элемент 10 включается. Включение элемента 10 не влияет на схему, т.к, элемент 4 заперт по цепи затвора напряжением

Лог, "О".

При считывании информации.

Так как ячейка памяти предназначена для работы в качестве ячейки управляющего ОЗУ, то цепи записи и считывания информации следует разграничить. При управлении объектами электронных схем (например, элементами коммутации или выступая в качестве источника опорного логического сигнала) выходное напряжение с ячейки можно снимать с точек: прямой сигнал - точка соединения стоковых областей элементов 3 и 4; инверсный сигнап - точка соединения стоковых областей элементов 1 и 2.

По сравнению с прототипом повьппается быстродействие ячейки памяти при записи информации путем исключения операции перехода на промежуточное значение напряжения питания при записи Лог. "1" в ячейку, а также за счет исключения шунтирующего действия элемента 4, который в момент записи отключается от шины 8 ячейки. Помимо этого, отключение элемента 4 поз воляет выполнить элемент 10 минимапь- ных топологических размеров и тем самам скомпенсировать потери ппощади от введения элемента 10 в ячейку памяти.

Формула изобретения °

Ячейка памяти на основе комплементарных МОП-транзисторов, содержащая первый и второй нагрузочные элементы на р-канальных транзисторах, первый и второй кпючевые элементы и элементы связи на п-канальных транзисторах, причем стоки транзисторов первых нагруэочного и кпючевого элементов объединены и подключены к затворам

5 1640738 6 транзисторов вторых нагрузочного и вого потенциала ячейки, о т л Н ч аключевого элементов и стоку транзис- ю щ а я с я тем, что, с целью поют тора элемента связи, исток и затвор шения быстродействия, в нее введен которого подключены соответственно третий ключевой элемент на р-канапь5 к разрядной и адресной шинам ячеики, ном транзисторе, затвор и исток котоистоки транзисторов нагрузочных эле- рого подкпючены соответственно к разментов подключены к шине питания я"ей рядной шине и шине нулевого нотенциаки, исток транзистора второго ключе- ла, а сток подключен к истоку транзисвого элемента подкпючен к шине нуле 1р тора первого ключевого элемента.

Составитель А. Ершова

Техред Л.Олийнык Корректор С. Черни

Редактор Б. Федотов

Заказ 1265 Тираж 352 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственио-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101