Преобразователь параллельного кода в последовательный

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей информации из параллельной формы в последовательную . Цель изобретения - расширение области применения за счет возможности управления параметрами преобразования. Преобразователь содержит мультиплексор 1, регистр 2 сдвига, первый-третий счетчики 3-5, первый - третий триггеры 6-8, первый и второй элементы 9 и 10 сравнения ,- первый - пятый элементы И 11- 15, элемент ИЛИ 16, элемент НЕ 17, элемент И-НЕ 18, информационные 19, управляющий 20, тактовый 21, первые и вторые 22 и 23 управляющие входы преобразователя, шину 24 лог.О и выход 25 преобразователя. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУЬЛИН

„„SU„„1640828

yg)g Н 03 M 9/ОЭ (ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ пО изОБРетениям и ОчнРытиям

ПРИ ГКНТ СССР (21) 4345415/24 (22). 17.12.87 (46) 07.04.91. Бюл. Р 13 (72) В.В.Ермаков (53) 681.325(088.8) (56) Авторское свидетельство СССР

II 1243097, кл. Н 03 М 9/00, 1984. (54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО

КОДА B ПОСЛЕДОВАТЕЛЬНЫЙ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей информации из параллельной формы в последоИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей информации из параллельной формы в последовательную.

Цель изобретения — расширение области применения за счет возможности управления параметрами преобразования.

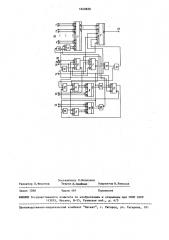

На чертеже представлена схема преобразователя.

Преобразователь содержит мультиплексор 1, регистр:2 сдвига, первый - третий счетчики 3-5, первый-третий триггеры 6-8, первый и второй элементы 9 и 10 сравнения, первый-пятый элементы И 11-15, элемент ИЛИ 16, элемент HE 17, элемент -HE 18, информационные 19, управляющий 20, тактовый 21, первый и вторые 22 и 23 управляющие входы

2 вательную. Цель изобретения — расширение области применения за счет возможности управления параметрами преобразования. Преобразователь содержит мультиплексор 1, регистр

2 сдвига, первый-третий счетчики 3-5, первый - третий триггеры 6-8, первый и второй элементы 9 и 10 сравнения,- первый — пятый элементы И 1115, элемент ИЛИ 16, элемент НЕ 17, элемент И-НЕ 18, информационные 19, управляющий 20, тактовый 21, первые и вторые 22 и 23 управляющие входы преобразователя, шину 24 лог."0" и выход 25 преобразователя. 1 ил. преобразователя, шину лог."0" 24 и выходы 25 преобразователя.

Преобразователь работает следую- . щим образом.

Перед началом преобразования элементы устройства находятся в исходном состоянии. На управляющем входе

20 преобразователя находится низкий уровень напряжения. Этот уровень поступает через элемент 17 на счетчик

3, откуда на все шины управления мультиплексора 1 поступают сигналы низкого уровня. В результате на выходе мультиплексора устанавливается необходимый для преобразования первый по счету код, поступающий с одной из и групп входов 19 преобразователя. Низкий уровень с входа

20 лодается на разрешающий вход регистра 2 и управляет третьим состоянием выхода 25 преобразователя. Тот же уровень с входа 20 подается че1640828. рез элемент И 11 íà R-входы триггеров 6 и 7, в результате они находятся в нулевом состоянии, низкий уровень напряжения с прямого выхода триггера 6 обнуляет триггер 8. С ин- версного выхода триггера 7 на регистр 2 поступает высокий уровень напряжения, который разрешает запись параллельного кода с мультиплексо- 1п ра 1.

При поступлении на вход 20 сигнала разрешения работы в виде высокого уровня напряжения преобразователь начинает свою работу. Высокий уровень 15 напряжения поступает на триггер 6 и через элемент И 11 - íà R-входы триггеров 6 и 7. К-входы этих триггеров соединены с шиной 24 логического "0".

Высокий уровень с входа 20 снимает третье состояние на выходе регистра 2. При поступлении первого тактового импульса на вход 21 на прямом выходе триггера 6 устанавливается вы- . сокий уровень напряжения, на инверс- 25 ном - низкий. Высокий уровень напряжения с прямого выхода триггера 6 поступает на триггер 7 и подготавливает к работе триггер 8 и элемент

И 14. Второй тактовый импульс через элемент И 14 и элемент ИЛИ 16 поступает на регистр 2 и записывает инфор" мацию с мультиплексора в регистр 2.

По заднему фронту второго тактового импульса триггер 7 взводится. Низкий уровень напряжения с инверсного выхода триггера 7 запрещает работу элемента И 14 и разрешает работу сдвигового регистра. в режиме выдачи последовательного кода на выход

25 устройства. Высокий уровень напряжения с триггера 7 разрешает работу элемента И 12. Низкий уровень напряжения с инверсного выхода триггера 5 разрешает работу счетчиков 4 и 45

5. Третий импульс поступает через элемент И 12 на счетчик 4 и через эле" мент ИЛИ 16 — на С-вход регистра 2, с выхода которого начинается вывод информации в последовательной форме.

При совпадении информации на выходе счетчика 4, поступающей на входы элемента 9 сравнения, с информацией управляющего кода на входах

22 преобразователя, поступающей на

55 вторые входы элемента 9, на выходе элемента 9 устанавливается высокий уровень напряжения. Первый же после сравнения тактовый импульс

4 через элемент И 13 проходит на тактовые входы счетчика 3 и триг- . гера 8. По его переднему фронту триггер 8 взводится, низкий уровень напряжения с его инверсного выхода запрещает работу элемента И 12, а высокий уровень с его прямого выхода разрешает работу элемента И 15.

Счетчик 3 производит счет. На выходе мультиплексора 1 устанавливается следующий параллельный код, который необходимо преобразовать. Код на входе 22 задает количество разрядов выдаваемой информации и может, например, устаналвиваться с портов ввода-вывода микропроцессора. Тактовые импульсы теперь поступают через элемент И 15 на тактовый вход счетчика 21. Содержимое счетчика непрерывно сравнивается на элементе 10 с кодом, поступающим на этот элемент с входов 23 преобразователя. Второй управляющий код определяет длительность паузы между выдачами преобразованной информации во внешние устройства. При равенстве информации на первых и вторых входах элемента 10 сравнения на его выходе устанавливается высокий уровень напряжения, который разрешает прохождение тактового импульса через элемент И-НЕ 18 на второй вход

:,элемента И 11.Импульс с элемента И 11 обнуляет триггеры 6 и 7.

Низкий уровень напряжения с прямого выхода триггера 6 обнуляет триггер 8 ° Устройство устанавливается в состояние, необходимое для обработки следующего параллельного кода с мультиплексора 1, и процесс повторяется.

Формула изобретения

Преобразователь параллельного кода в последовательный, содержащий мультиплексор, информационные входы которого являются информационными входами преобразователя, первый счетчик, выходы которого соединены с управляющими входами мультиплексора, первый триггер, I-вход которого объединен с первым входом первого элемента И и является управляющим входом преобразователя, выход первого элемента И и соединен с R-входом первого триггера, прямой выход первого триггера соединен с

16

I-входом второго триггера, прямой выход которого соединен с первым входом второго элемента И, тактовый вход второго триггера является тактовым входом устройства, третий-пятый элементы И и элемент ИЛИ, о т-. л и ч а ю шийся тем, что, с целью расширения области применения, за счет возможности управления параметрами преобразования, в преобразователь введены второй н третий счетчики, элементы сравнения, элемент И-НЕ, элемент НЕ, третий триггер шина логического нуля и регистр сдвига, выход которого является выходом преобразователя, выходы мультиплексора подключены к соответствующим входам параллельной загрузки регистра сдвига, 0-вход регистра сдвига, Квходы первого и второго тригперов объединены и подключены к шине логического нуля, инверсный выход первого триггера подключен к R-входам второго и третьего счетчиков, выходы которых подключены к соответствующим первым входам соответствующих элементов сравнения, вторые входы которых являются соответственно первьвии и вторыми установочными входами преобразователя, выходы элементов сравнения подключены к первым входам со, ответственно третьего элемента И и элемента И«НЕ, выход элемента И-НЕ

40828

6 соединен с вторым входом первого элемента И, выход третьего элемента

И соединен с С-входами третьего триггера и первого счетчика, R u D-входы третьего триггера и первый вход четвертого элемента И объединены и под; ключены к прямому выходу первого триггера, прямой и инверсный выходы третьего триггера соединены соответственно со вторым входом пятого элемента И и вторым входом второго элемента И, выходы пятого элемента И соединены е С-входом третьего счет15 чика, выход второго элемента И соединен с С-входом второго счетчика и первым входом элемента ИЛИ, выход которого соединен с С-входом регистра сдвига, инверсный выход второго

20 триггера соединен с V-входом регистра сдвига и вторым входом четвертого элемента И, выход которого соединен с вторым входом элемента ИЛИ, W-вход регистра сдвига и вход элемента НЕ объединены и подключены к управляющему входу преобразователя, выход элемента НЕ соединен с R-входом первого счетчика, С-вход первого триггера, третьи входы второго и четвер30 того элементов И, вторые входы третьего и пятого элементов И и элемента И-НЕ объединены и подключены к тактовому входу преобразователя.

1640828

Составитель О.Неплохов

Редактор Б.федотов Техред Л,Олийнык

Корректор Н.Ревская

Ъ

Тирах 461

Заказ 1266

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ултород, ул. Гагарина, 101