Устройство для контроля последовательности событий

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при контроле и наладке сложных цифровых устройств, в частности микропроцессорных систем. Целью изобретения является повышение достоверности контроля. Устройство состоит из блока 1 памяти, схемы 2 сравнения, формирователей 3 и 4 импульсов , элемента И 5, счетчика 6, триггера 7, мультиплексора 8 и переключателя 9 о Информация с выходов счетчика сравнивается 6 информацией, поступающей с блока памяти В результате сравнения счетчик увеличивает свое значение на единицу0 Схема сравнения сравнивает очередные значения счетчика и блока памяти. Этот алгоритм повторяется до тех пор, пока не будет достигнуто значение счетчика , соответствующее заданной длине последовательности, или же не произойдет сброс в начальное состояние. Устройство может быть запрограммировано на опознание очень длинных цифровых последовательностей, что позволяет фиксировать перемежающиеся сбойные ошибки, тем самым повышается достоверность контроля, 4 ил

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1 424 4

С 06 Г 1 1/28, 1 1/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ и2.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4486816/24 (22) 26.09.88 (46) 15,04.91. Бюл. Р 14 (72) А.Н. Бучнев, В,Р, Горовой, О.А. Зимнович, Е.И. Карпунин и Ю.П. Крылатых (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 1170458, кл. G 06 F 11/00, 1985.

Авторское свидетельство СССР

Р 1340415, кл. G 06 F 11/00, 1986..(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕ ДОВАТЕЛЬНОСТИ СОБЫТИЙ (57) Изобретение относится к вычислительной технике и может быть ис,пользовано при контроле и наладке .сложных цифровых устройств, в частности микропроцессорных систем. Целью изобретения является повышение достоверности контроля. Устройство состоит из блока 1 памяти, схемы 2

2 .сравнения, формирователей 3 и 4 импульсов, элемента И 5, счетчика 6, триггера 7, мультиплексора 8 и переключателя 9. Информация с выходов счетчика сравнивается с информацией, поступающей с блока памяти. В результате сравнения счетчик увеличивает свое значение на единицу. Схема сравнения сравнивает очередные значения счетчика и блока памяти. Этот алгоритм повторяется до тех пор, пока не будет достигнуто значение счетчика, соответствующее заданной длине последовательности, или же не произойдет сброс в начальное состояние.

Устройство может быть запрограммировано на опознание очень длинных цифровых последовательностей, что позволяет фиксировать перемежаю,щиеся сбойные ошибки, тем самым повышается достоверность контроля. ,4 ил.

1642474

Изобретение относится к вычислительной технике и может быть использовано при контроле и наладке сложных цифровых устройств, в частности микропроцессорных систем.

Целью изобретения является повышение достоверности контроля за счет реализации режима отслеживания данных последовательностей в прохождении программы в контролируемом логическом блоке.

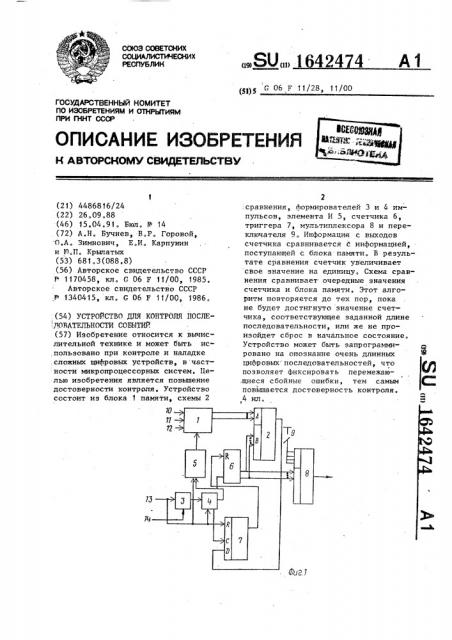

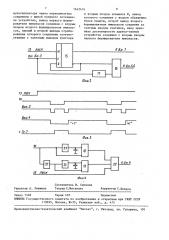

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 — блок-схема второго формирователя импульсов; на фиг. 3 — временные диаграммы работы устройства; на фиг. 4 — блок-схема первого фор10 мирователя импульсов.

Устройство (фиг. 1) содержит блок

1 памяти, схему 2 сравнения, первый и второй формирователи 3 и 4 импульсов, элемент И 5, счетчик 6, триггер

7, мультиплексор 8 и переключатель 9. 25

Первая группа адресных входов блока 1 памяти соединена с группой входов 10 устройства, Информационная группа входов 11 логического компаратора соединена с информационной группой входов блока 1 памяти, группа выходов которого соединена с первой группой входов схемы 2 сравнения, Вторая группа входов схемы 1 сравнения соединена с группой выходов счетчика 6

35 и группой адресных входов мультиплексора 8, информационные входы которого могут выборочно подключаться к нулевой шине переключателем 9. Управляющий вход записи/чтения блока 1 памяти является управляющим входом 12 устройства. Вход "Пуск" 13 устройства соединен с входом формирователя 3, первым входом формирователя 4, первым входом элемента И 5 и нулевым входом триггера 7. Выход формирователя 3 соединен с вторым входом формирователя 4, первый выход которого соединен с вторым входом .элемента И

5 и тактирующим входом счетчика 6, 50 нулевой вход которого соединен с выходом триггера 7. Тактирующий вход триггера 7 соединен с вторым выходом формирователя 4. Выход схемы 2 сравнения соединен с установочным входом триггера 7. Выход мультиплексора 8 является выходом устройства„ Второй вход формирователя 3 является вхо-. дом 14 признака достоверности - преса данных контролируемого логического блока. Выход элемента И 5 соединен с выходом выборки блока 1 памяти, Формирователь 4 импульсов содержит (фиг. 2) триггер 15, элемент

И 16 и элемент 17 задержки. Нулевой вход триггера 15 соединен с входом

"Пуск" 13 устройства, а тактирующий вход — с выходом формирователя 3 и первым входом элемента И 16 через элемент 17 задержки, второй вход которого соединен с инверсным выходом и установочным входом триггера 15.

Выход элемента И 16 соединен с вторым входом элемента И 5 и тактирующим входом счетчика 6. Прямой выход триггера 15 соединен с тактирующим входом триггера 7.

Формирователь 3 (фиг. 4) содержит элементы И 18, 19 и 20, элемент

НР 21 и элементы 22 и 23 задержки.

Формирователь 3 обеспечивает формирование импульса по переднему фронту сигнала и по заднему фронту сигнала с последующей трансляцией.

Устройство работает следующим образом.

Устройство имеет два основных режима работь1, определяемых сигналом на входе "Пуск" 13: первьп" — режим начальной установки (на входе 13—

"0"), по которому осуществляется запись информации соответствующей требуемой логической последовательности в блок 1 памяти. "0" на входе 13 устанавливает через элемент И 5 вход выборки блока 1 памяти в состояние

"0" — разрешается режим записи в блок 1.

Запись производится по следующему алгоритму.

На входы 10 устройства подается адрес ячейки памяти, в которую необходимо записать требуемую информацию, которая подается на информационную группу входов блока 1 памя и с входов 11 устройства. Адрес и информация на входах блока 1 памяти стробируется импульсом "0" по входу 12 устройства. Этим импульсом информация записывается в ячейку блока 1 памяти. Эта процедура повторяется до тех пор, пака не будет прописан весь блок 1 памяти.

1642474

Например, для восьмиразрядного адреса:

Адрес Данные

00000001 О

00000100 1

10000000 2

11001100 3

11110000 .4

00011111 5

Второй режим работы — поиск заданной последовательности событий.

К входам .10 устройства подключается объект (контролируемое логическое устройство). На вход 12 устройства подается сигнал уровня "1", что обеспечивает работу блока 1 памяти в режиме чтения. Согласно временной диаграмме, приведенной на фиг, 3, после задания на входе "Пуск" 13 "1", фор- 20 мирователю 3 разрешена работа. Формирователь 3 по сигналам достоверности адреса (данных, поступающих о" контролируемого устройства на вход 14 (фиг. 3)), по каждому фронту сигнала 25 формирует импульс "О . На каждый входной импульс по входу 14 формирователь 3 формирует два импульса "0", а формирователь 4 — два стробирующих сигнала. Первый сигнал "Вых. 4"

30 (фиг. 3) формируется на выходе элемента И 16 (фиг„2), является сигналом выборки блока 1 памяти и сигналом, по заднему фронту которого (переход из состояния "0 в состояние "1") происходит инкремент "1" в счетчик 6. Второй стробируюпцлй сигнал с выхода формирователя 4 (фиг„ 3) поступает с прямого выхода триггера 15 на вход триггера 7, который срабатывает по переднему фронту стробирующего сигнала (переход из состояния "О" в состояние "1").

Согласно приведенному примеру входная последовательность событий поступает на адресные входы блока 1 памяти„ Этой последовательности соответствует последовательность данных на выходе блока 1 памяти от О с инкре-. ментом до 5. До тех пор, пока на выходе блока 1 памяти не появится значение О, счетчик 6 заблокирован по входу обнуления, так как триггер

7 первым же тактирующим импульсом (фиг. 3) устанавливается в состояние

"О". На вход 10 поступает комбинация, соответствующая значению 00000001.

На выходе блока 1 памяти устанавливается сигнал "О", который поступает на первую группу входов схемы 2 сра внения. На вторую группу входов поступает сигнал "О" сс счетчика 6. В результате на вьжоде схемы сравнения формируется сигнал сравнения — "1", которьп. по синхросигналу (фиг, 3) на тактирующем входе триггер". 7 устанавливает его в состояние "1", тем самым снимая блокировку счетчика 6. По заднему фронту сигнала "Выход 4" (переход из состояния "О" в состояние

"1") счетчик 6 увеличивает значение на +1. Этот алгоритм работы устройства выполняется до тех пор, пока не произойдет нарушение в последовательном инкременте "+1" в счетчик 6 изза того, что блок 1 памяти выберет значение, не соответствующее заданной последовательности, Устройство возвращается в исходное состояние и обнаруживает заданную последовательность заново, мультиплексор,8 с помощью переключателя 9 устапавлиьает на одном из своих информационных входов сигнал "0". Этот сигнал транслируется на выход устройства только тогда, когда выполняется заданная последовательность входных событий.

Формула и з о б р е т е н и я

Устройство для контроля последовательности событий, содержащее блок памяти, триггер, мультиглексор и элемент И, причем выход мультиплексора является выходом результата сравнения устройства, входы адресный, информационньпт и записи устройства соединены соответственно с входами адресным, информационным и записи блока памяти, о т л и ч а ю щ е е с я тем, что, с целью повьппения достоверности контроля, в него введены первый и второй формирователи импульсов, переключатель, счетчик и схема сравнения, причем группа информационных выходов блока памяти соедпнены с первой группой схемы сравнения, выход равенства которой соединен с информационным входом триггера, вход запуска устройства соединен с первьпп входами элемента И, первого и второго формирователей импульсов и нулевым ьходом триггера, прямой выход которого соединен с нулевым входом счетчика, группа выходов которого соединена с группой адресных входов мультиплексора и второй группой входов схемы сравнения, информационные вхбды

1б42474

Фиг.2

13 ЛУП

Вых 3

8 .4 +7" с Тг.7.

Фиг. 3

Фиг.4

Составитель И. Сигалов

Техред С.Мигунова

Корректор С.Шевкун

Редактор А, Лежнина

Заказ 1148 Тираж 422 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101 мультиплексора через переключатель соединены с шиной нулевого потенциала устройства, выход первого формирователя импульсов соединен с вторым входом второго формирователя импуль5 сов, первый и второй выходы стробирования которого соединены соответственно с тактовым выходом триггера

I и вторым входом элемента И, выход которого соединен с входом обращения блока памяти, второй: выход второго формирователя импульсов соединен со счетным входом счетчика, вход признака достоверности адреса-записи устройства соединен с вторым входом первого формирователя импульсов.