Одноразрядный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ, Целью изобретения является упрощение сумматора . Одноразрядный сумматор содержит МО 1Ь транзисторы п-типа 1-6 и р-типа 7-11, диод 12, входы X, Y, Z и выходы суммы S и переноса С. Поставленная цель достигается за счет введения новых связей в подключении входов Y и Z. 1 ил.

СОЮЗ СОВЕТСКИХ х

РЕСПУБЛИК (5})5 G 06 F 7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТИЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОЧНРЫТИЯМ

ПРИ fHHT СССР (21) 4608804/24 (22) 22.11.88 (46) 23.04.91. Бюл. }} 15 (71) Ленинградский электротехнический институт нм. В.И.Ульянова (Ленина) (72) В.И.Варшавский, А.Ю.Кондратьев, В.А.Романовский и Б.С.Цирлин (53) 681. 325.5 (088. 8) (56) Авторское свидетельство СССР

N 1439578, кл. С 06 F 7/50, 1987.

Авторское. свидетельство СССР

}} 1509874, кл. С 06 F 7/50, 1987..,SUÄÄ 1644132 А 1

2 (54) ОДНОРАЗРЯДНЫЙ СУИМАЮР (57) Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ. Целью изобретения является упрощение сумматора. Одноразрядный сумматор содержит МОП-транзисторы и-типа 1-6 и р-типа 7-11, диод 12, входы Х, Y Z и выходы суммы S и переноса С. Поставленная цель достигается за счет введения новых связей в подключении входов Y u Z. 1 ил.

1644132 л

Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВИ.

Цель изобретения — упрощение сум5 матора.

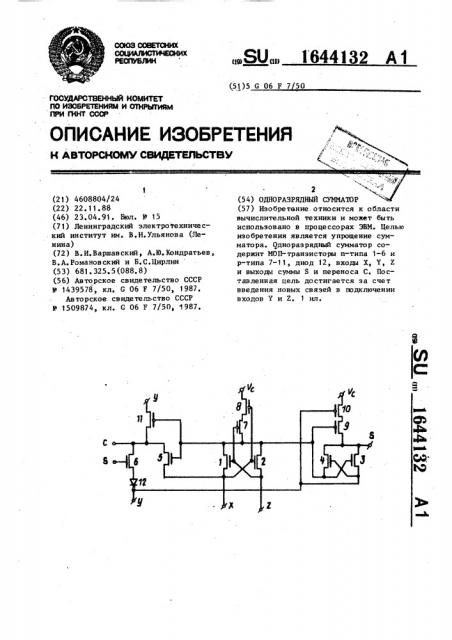

На чертеже приведена схема однораэрядно ro сумматора.

Одноразрядный сумматор содержит

ИОП-транзисторы п-типа 1-6 и р-типа

7-11, диод 12, входы Х, Y и Е и выходы суммы S и переноса С.

Сумматор работает следующим образом.

Если на вход Х подается сигнал единичного уровня, а на вход Z — нулевого или наоборот (Х = 1, 2 = О, или Х = О, Z = 1), то один из транзисторов 1 или 2 будет открыт и на их стоках установится низкий потен- 2р циал с одного из входов Х или Z так как один из транзисторов 7 или 8 будет при этом закрыт. Если Х = Z = 1, то транзисторы 7 и 8 закрываются, а транзисторы 1 и 2 открываются, в ре- 25 эультате чеМ на их стоках устанавливается высокий потенциал. Если Х =

= Е = О, то транзисторы 1 и 2 закрываются, но открываются транзисторы 7 и 8 и пропускают высокий потенциал с шины питания на стоки транзиСторов

1 и 2. Таким образом, транзисторы

1,2,7 и 8 образуют логический элемент равнозначности (Х 9 Z) .

Аналогично транзисторы 3,4,9 и 10 выполняют логическую операцию равно35 эначности над сигналами, поступакщими с первого элемента РАВНОЗНАЧНОСТЬ и входа У, формируя тем самым на выходе S сумму трех входных слагаемых:

Формула изо бре те ния

Одноразрядный сумматор, содержащий шесть МОП-транзисторов п-типа, пять MOII-транзисторов р-типа и диод, причем затворы первых транзисторов пи р-типа соединены с истоком второго транзистора п-типа, затвор которого соединен с истоками первого и третьего транзисторов п-типа, первым входом сумматора и затвором второго транзистора р-типа, сток которого сое\ динен с.истоком первого транзистора р-типа, исток которого соединен со стоками первого и второго транзисторов п-типа, затворами третьих и четвертых транзисторов и- и р-типа и истоком пятого транзистора п-типа, затвор которого соединен с катодом диода,. истоком четвертого транзистора п-.типа и затвором пятого транзистора р-типа, сток которого соединен с истоком че тв е рто ro тран э исто ра р- типа, сток которого соединен со стоками четвертого и пятого транзисторов птипа, выходом суммы сумматора и затвором шестоro транзистора п-типа, исток которо ro соединен с анодом диода, а сток — со стоками третьих транзисторов п- и р-типа и выходом переноса сумматора, шина питания которого подключена к истокам второго и пятого транзисторов р-типа, о т— л и чающий ся тем, что, сцелью упрощения сумматора, его второй вход подключен к катоду диода и истоку третьего транзистора р-типа, а третий вход сумматора — к истоку-второго транзистора п-типа.

8=(Х Ю Z) QY=XQY®Z, Если на выходе первого элемента

РАВНОЗНАЧНОСТЬ устанавливается нуле- 45 вое значение потенциала (XQZ = О), то открывается транзистор 11 и пропускает на выход C сигнал с входа У, В противном случае (XP+Z = 1) открывается транзистор 5 и на выход С про- 50

:ходит сигнал с входа X. Таким образом, на выходе С реализуется функция переноса:

С=(Х®Е)У + (Х®Z)X=XY + XZ + YZ

Если (ХЩ Z) = О и Y = О, на выходе S устанавливается высокий потенциал, транзистор 6 открывается и низкий потенциал проходит с входа Y на выход С через диод 12 и транзистор 6, что обеспечивает понижение уровня лоrнческого нуля на выходе .С. Если на выходе С устанавливается низкий уровень, диод 12 будет находиться в закрытом состоянии, что исключает влияние сигнала, формируемого на выходе С, на функцию, реализуемую на выходе S.