Устройство для вычитания

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах для распознавания образов, поиска информации и автоматизации принятия решений в нечетных условиях. Целью изобретения является упрощение устройства. Для этого в устройство, содержащее регистр сдвига, группу элементов ИЛИ, группу элементов И и элемент ИЛИ-НЕ, введен элемент ЗАПРЕТ с соответствующими связями. Устройство предназначено для вычисления модуля разности |А-В|, отрицания 1-А и степени нечетного равенства двух чисел 1-JA- -В I для чисел, представленных в унитарном коде один из т. 1 ил. с «

СОЮЗ СОВЕТСКИХ соцИАлистических

РЕСПУБЛИК (51)5 G 06 F 7/50

ОПИСАНИЕ ИЗОбРЕТЕНИЯ

Н А STOPCHOMY СВИДЕТЕЛЬСТВУ (9, ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯМ

ПРИ ГКНТ СССР

1 (21 ) 4681 465/24 (22 ) 1 9. 04. 89 (46) 23. 04. 91. Бюл. Х - 15 (71) Таганро гский радиотехнический институт им. В. Д. Калмыкова (72) А. Н.Мелихов, В.П. Карелин и В.Н.Решетняк (53) 681. 325 (088. 8) (56) Авторское свидетельство СССР

В 739532, кл. G 06 F 7/50, 1979.

Авторское св иде тельство СССР

N- 1376079, кл.. С 06 F 7/50, 1987.

Авторское свидетельство С0СР

Ф 1487028, кл. G 06 F 7/50, 1987. (54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ (57) Изобретение относится к вычисИзобретение относится к вычислительной технике и может быть использовано в устройствах для распознанания образцов, поиска информации и автоматизации принятия решений в нечетных условиях.

Цель изобретения — упрощение устройств а.

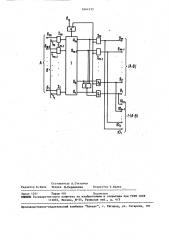

На чертеже приведена.функциональная схема устройства.

Устройство для вычитания содержит регистр 1 сдвига, группу 2 элементов ИЛИ, группу 3 элементов И, элемент ЗАПРЕТ 4 и элемент HJIH-HE 5.

Устройство имеет входы 6 и 7 операндов, тактовый вход 8, выходы 9 разрядов разности и вых оды 10 разрядов степени нечетного равенства.

Устройство предназначено для.вычисления модуля разности R где 8. =

=lA-В I, отрицания А = 1-А и степени С

„.80„„1644133 А 1

2 лительной технике и может быть использовано в устройствах для распознавания образов, поиска информации и автоматизации принятия решений в нечетных условиях. Целью изобретения является упрощение устройства. Для этого в .устройство, содержащее регистр сдвига, группу элементов ИЛИ, группу элементов И и элемент ИЛИ-НЕ, введен элемент ЗАПРЕТ с соответствующими связями. Устройство предназначено для вычисления модуля разности ) А-В(, отрицания 1-А и степени нечетного равенства двух чисел i-1А-В для чисел, представленных в унитарном коде один из m. 1 ил.

I нечетного равенств а (эквивалентности) двух чисел A и В, по формуле

С = 1-R = 1 — IA-В (, где A,В,С,R — числа из инте рв ала 0, 1) представленные m-разрядным унитарным кодом (один из m)

Алгоритм работы устройства следующийй °

В параллельный регистр сдвига записывается код, полученный объединением унитарных кодов чисел А и В.

Затем содержимое регистра сдвигается в сторону младших разрядов до появления единицы в младшем разряде, т.е. на у позиций, где О,у — меньшее из чисел А и В. При этом, если

АфВ, то, заменив единицу на нуль в младшем разряде кода полученного в регистре после окончания сдвига, имеют унитарный код модуля разности чисел А и В. Если же А=В, то в регист1644133

50 ре после сдвига уже будет сформирован унитарный код числа нуль (так как

R А-В = О), и этот код корректировать не нужно; Унитарный код степени С нечетного равенства чисел А и В, где С = 1 - )А-В, образуется иэ унитарного кода числа R = lA В I путем перестановки единицы, стоящей в i-м разряде числа К в (пгд+1)-й разряд и записи в i-й разряд числа нуль.

Вычисление отрицания А = 1-А числа А сводится к рассмотренной операции вычисления модуля R разности чи" сел А и В, где В = 1, т.е. к получению значения А =. К = lA-BI=IA-1l= l1"А = I-А, так как для нечетных переменных всегда выполняется А(1.

Устройство работает следующим об- 20 разом.

На входы 6 и 7 подаются числа А и В иэ интервала i 0,1), представленные унитарным m-разрядным кодом (один из m-разрядов — единичный, остальные нулевые), на выходах элементов ИЛИ 2 -2 „ образуется двоичный код, представляющий собой объединение кодов чисел А и В, который записывается в регистр 1 сдвига. Далее 30 на вход 8 поступают тактовые, импульсы, которые через открытый элемент

ЗАПРЕТ 4 поступают на вход управления сдв игом ре гис тра 1. Как только после очередного сдвига в младшем разряде регистра 1 будет записана

35 единица, элемент ЗАПРЕТ 4 запирается, а на выходе одного из элементов

И 3 (определяемом положением в данный момент единичного разряда в регистре 1) будет логическая единица, которая поступит на выход соответствующего разряда модуля разности чисел 9. Если после сдвига содержимого регистра 1 кроме единицы в младшем 45 разряде регистра 1 единица будет еще в некотором i-м разряде, где i=2...,, m, что обусловлено неравенством А В то с целью получения унитарного кода модуля разности чисел А и В единица с выхода младшего разряда на выход первого элемента И 3 не проходит.

Зта коррекция кода осуществляется при помощи элемента HJIH-НЕ 5, на (i+1)-й вход которого поступает еди55 ница с выхода i-го разряда регистра. Сигнал уровня лЬ гичес ко го нуля с выхода элемента KlH-НЕ 5 запретит прохождение единичного сигнала на выход элемента И 3, что и обусловит формирование на выходах 9 устройства унитарного кода величины R=(А-В !.

Если же А=В, то в регистре 1 после сдвига содержимого единица будет только лишь в младшем разряде, а на выходе элемента ИЛИ-НЕ 5 будет сформирован сигнал уровня единицы, что I обеспечит прохождение унитарного кода, сформированного в регистре 1, на выходы элементов И 3 беэ изменения.

Поскольку А,В Я (0,1), то на симметрично расположенных выходах разрядов

10 -10„образуется унитарный код дополнения С величины R, т.е. код степени нечетного равенства С = 1-R =

= 1-1А-В(.

Для вычисления отрицания А=1-А на группы входов 6 и 7 устройства подаются соответственно унитарный код числа А и унитарный код числа B=0, При этом на выходах 9 будет сформирован унитарный код числа A а на выходах 10 — код числа A=1-А.

Формула изобретения

Устройство для вычитания, содержащее регистр сдвига, группу из m элементов ИЛИ (где m — разрядность операндов), группу из m элементов И и элемент ИЛИ-НЕ, причем первые входы элементов И группы соединены с выходами соответствующих разрядов регистра сдвига, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит элемент ЗАПРЕТ, выход которого соединен с входом управления сдвигом регистра сдвига, первые входы элементов ИЛИ группы подключены к входам первого операнда устройства, а вторые входы — к входам второго операнда устройства, выходы элементов ИЛИ группы соединены с входами соответствующих разрядов регистра сдвига, выходы разрядов которого с второго по m-й соединены с входами элемента ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента И группы, первый. вход которого подключен к вторым входам элементов И группы с второго по m-й и к инверсному входу элемента ЗАПРЕТ, прямой вход которого является тактовым входом устройства, выход i-го элемента И группы (i=1,..., m) соеди" нен с выходом i-ro разряда модуля разности чисел устройства и выходом (m-i+1)-ro разряда. степени нечетного равенства чисел устройства.

1644133

7ъ/Д .Я /

Составитель А. Степанов

Редактор Е. Папп Техред Л.Сердюкова Корректор Т.Малец

Заказ 1241 Тираж 401 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101